名称:30分钟倒计时设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

时间可调的倒计时器设计

1、可以通过加减按键控制倒计时起始时间

2、按下开始按键后开始倒计时

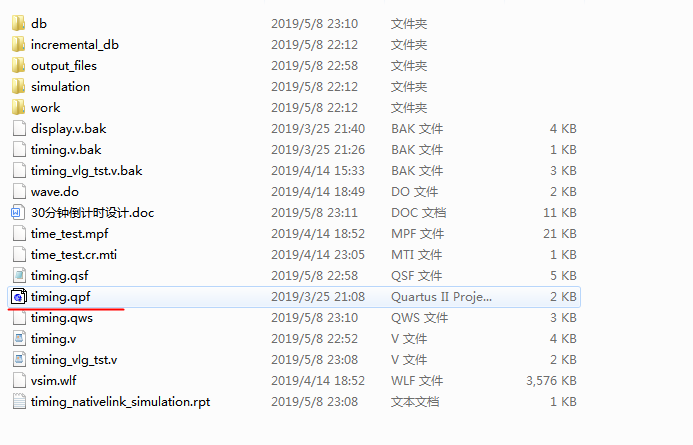

1. 工程文件

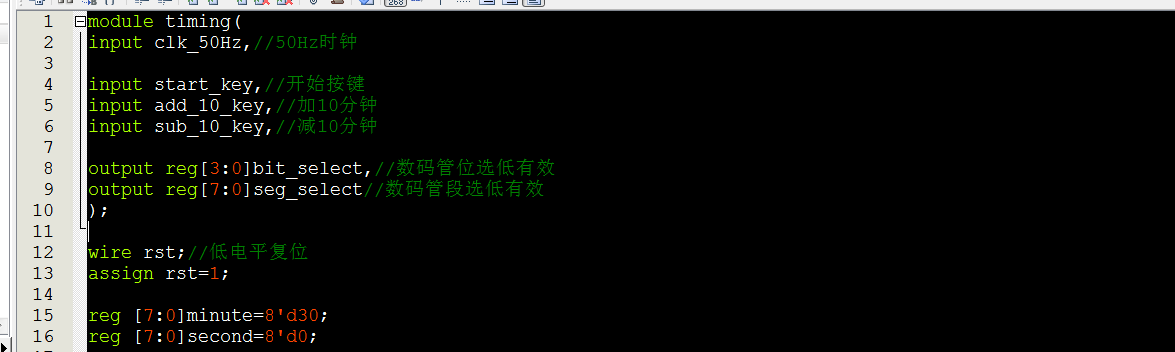

2. 程序文件

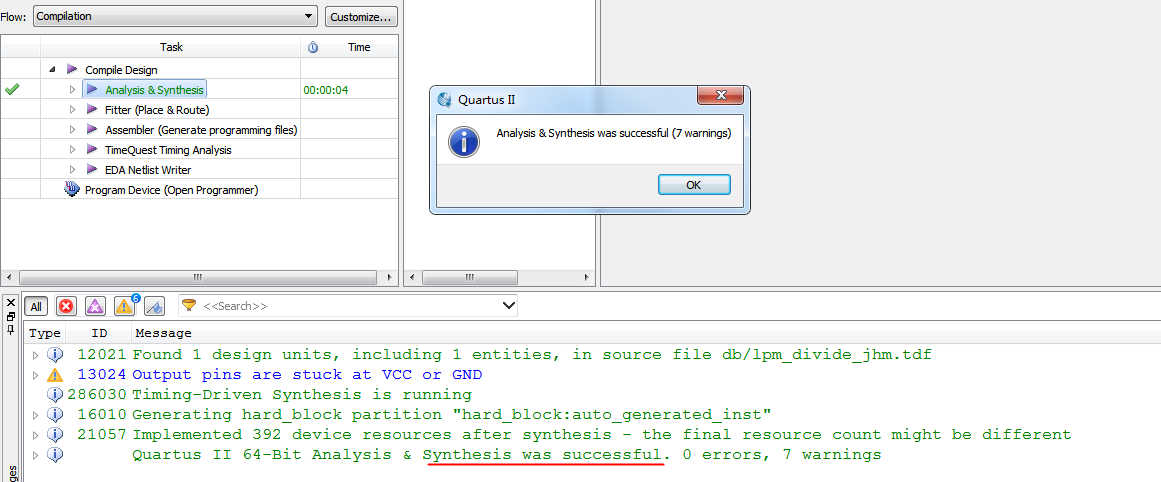

3. 程序编译

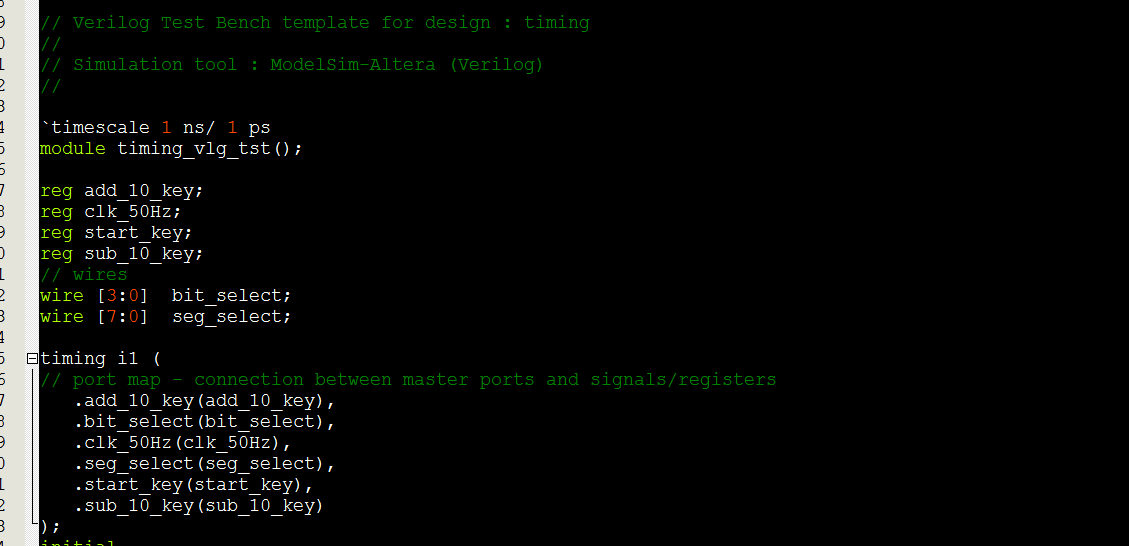

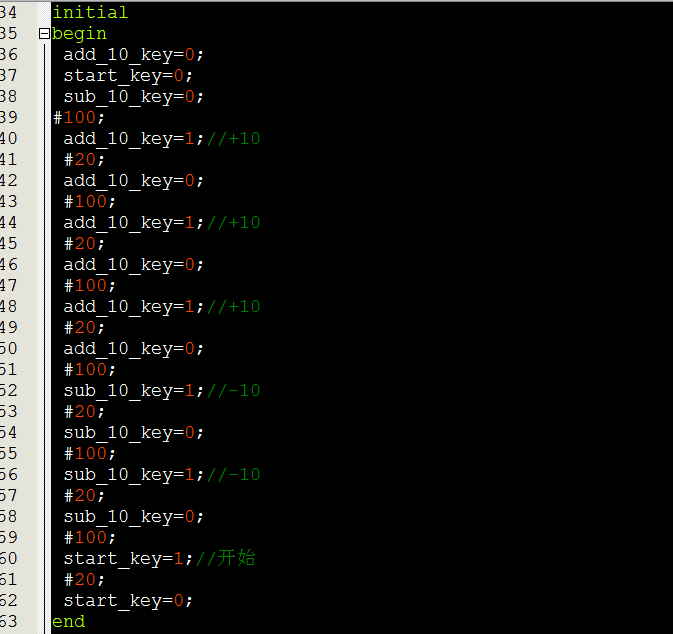

4. testbench

5. 仿真图

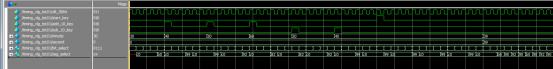

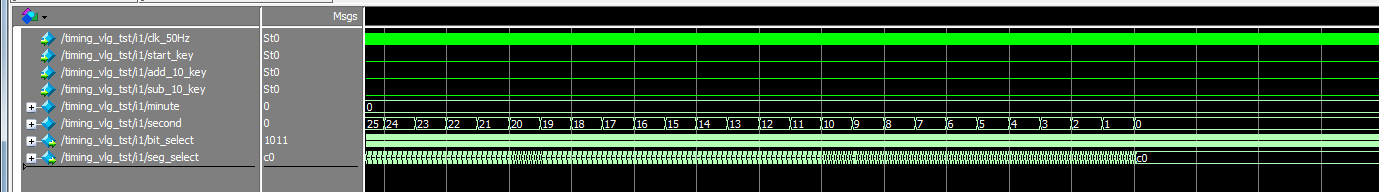

整体仿真图

按键设置加10,减10分钟,按下开始按键后开始倒计时

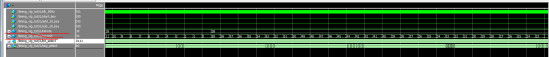

倒计时,分钟和秒钟

倒计时结束

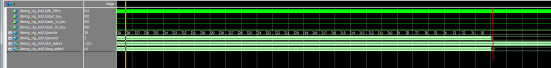

数码管位选和段选(对应程序中数码管段选译码和位选)

部分代码展示:

module timing( input clk_50Hz,//50Hz时钟 input start_key,//开始按键 input add_10_key,//加10分钟 input sub_10_key,//减10分钟 output reg[3:0]bit_select,//数码管位选低有效 output reg[7:0]seg_select//数码管段选低有效 ); wire rst;//低电平复位 assign rst=1; reg [7:0]minute=8'd30; reg [7:0]second=8'd0; ///分频计时1s reg [31:0] time_count=32'd0; reg clk_1Hz=1'd0; always@(posedge clk_50Hz) if(time_count==32'd49)//分频到1Hz begin time_count<=32'd0; clk_1Hz<=1; end else begin time_count<=time_count+32'd1; clk_1Hz<=0; end /状态机/ reg [1:0]current_state; reg [1:0]next_state; parameter idle =2'd0;//起始状态 parameter timing =2'd1;//定时状态 parameter alarm =2'd2;//定时结束 always@(posedge clk_50Hz) begin if(rst==1'd0) begin current_state <=idle; end else begin current_state<=next_state; end end //状态机设计 always@(*) begin case (current_state) idle: begin if(start_key==1)//按下开始键开始倒计时 next_state=timing; else next_state=idle; end timing: begin if(minute==8'd00 && second==8'd00)//倒计时结束后到alarm状态 begin next_state=alarm; end else begin next_state=timing; end end alarm: begin next_state=idle;//回到起始状态 end default: begin current_state=idle; end endcase end always@(posedge clk_50Hz) begin if(rst==1'd0) begin minute <=8'd30;//复位后显示30分钟00秒 second <=8'd0; end case (current_state) timing://倒计时 begin if(clk_1Hz)//1秒钟变一次 if(minute==8'd0 && second==8'd0)begin minute<=8'd0; second<=8'd0; end else if(second==8'd0)begin minute<=minute-8'd1; second<=8'd59; end else begin minute<=minute; second<=second-8'd1; end end idle://设置倒计时时间 begin if(add_10_key==1)//加10分钟 if(minute>=8'd99) minute<=8'd99;//最大不超过99分钟 else minute<=minute+8'd10;//加10分钟 else if(sub_10_key==1)//减10分钟 if(minute<8'd10) minute<=8'd10;//最小不低于10分钟,否则再减10变为负数 else minute<=minute-8'd10;//减10分钟 end default:; endcase end

源代码

扫描文章末尾的公众号二维码

3364

3364

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?