名称:自动售货机设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

设计内容

在EDA环境下,使用VHDL语言设计一个自动饮料售卖机

设计任务和目标

1.使用VHDL语言描述一个自动饮料售卖机,能够接收5角以上10元以下共4

种面额的货币,进行饮料的购买,并根据实际情况找零

2.饮料共6种,对应6个按键。饮料售价分为1元、1.5元、2元和3元,存在两种或两种以上的饮料对应相同售价的情况

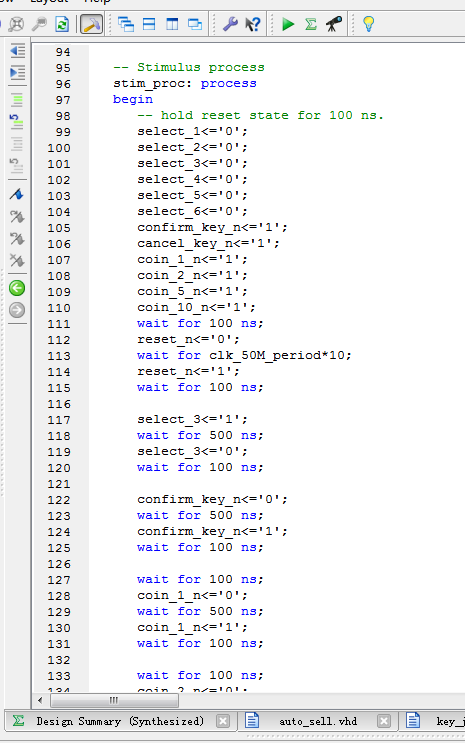

3.编写合适的 testbench文件,对上述系统进行测试并仿真

4.完成该系统的ⅦHDL模块化描述,注意使用分层次设计,并在顶层设计中采用

元件例化的方式指定模块间的硬件连接方式

1. 自动售货机功能描述

2. 工程文件

3. 程序文件

4. 程序编译

5. RTL图

6. Testbench

7. 仿真图

整体仿真图

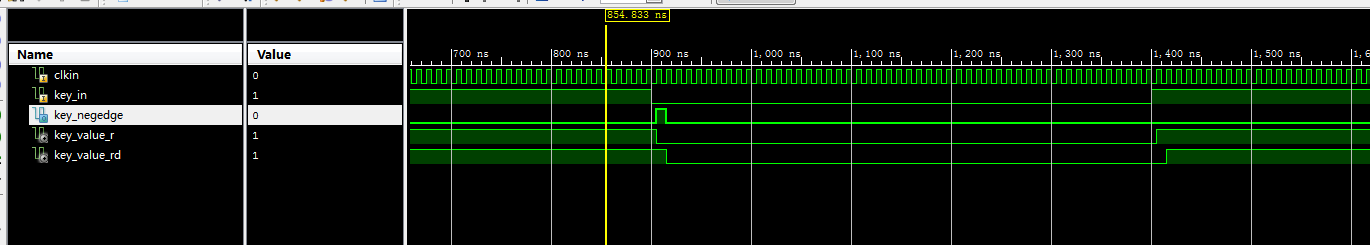

按键下降沿检测模块仿真

售货机控制模块仿真

数码管显示模块仿真

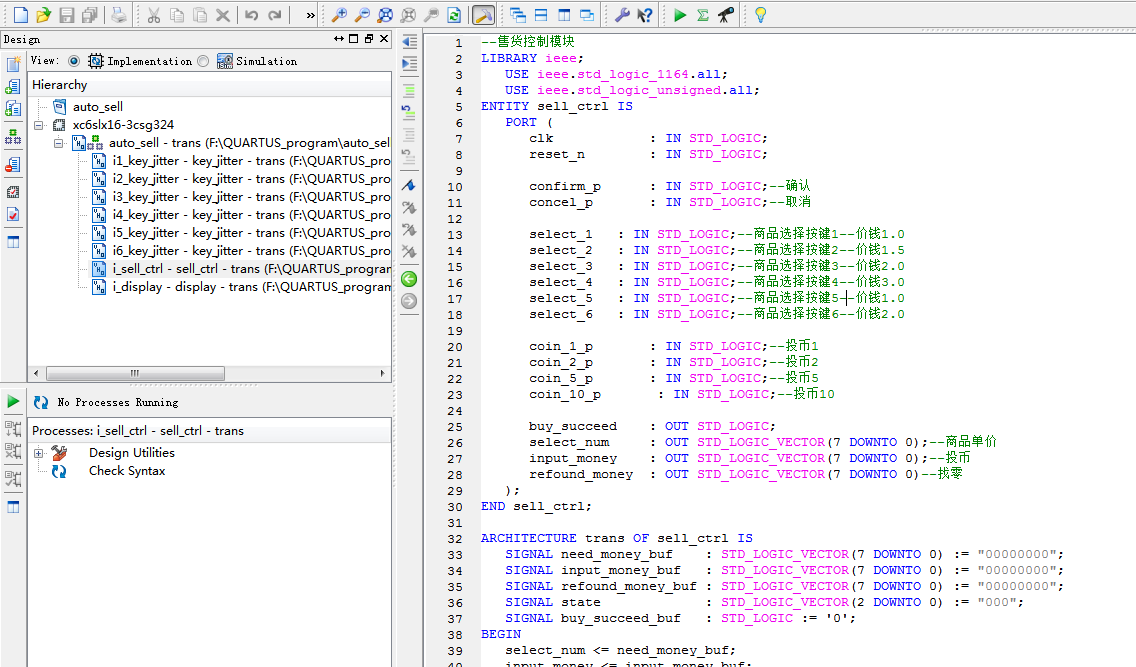

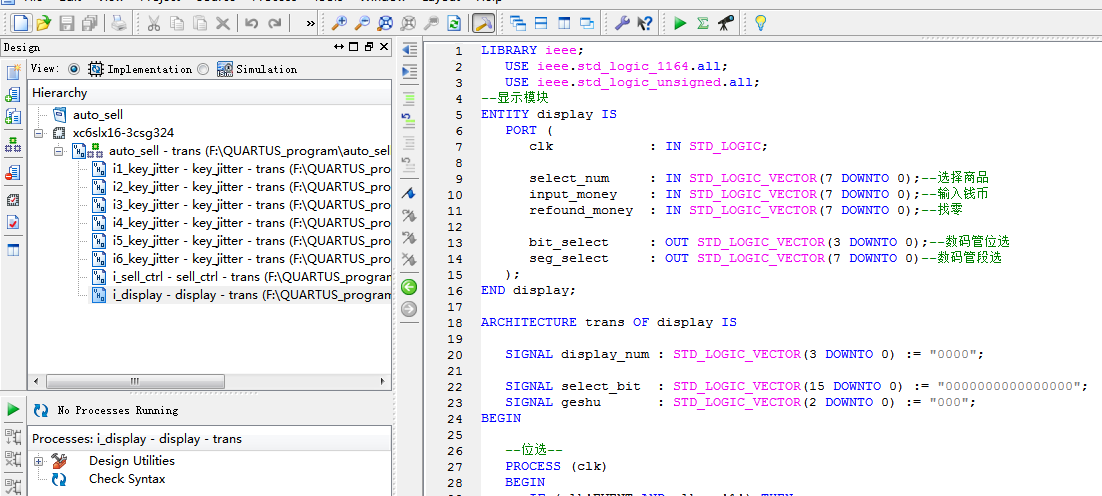

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY auto_sell IS PORT ( clk_50M : IN STD_LOGIC;--时钟 reset_n : IN STD_LOGIC;--复位 select_1 : IN STD_LOGIC;--商品选择按键1--价钱1.0 select_2 : IN STD_LOGIC;--商品选择按键2--价钱1.5 select_3 : IN STD_LOGIC;--商品选择按键3--价钱2.0 select_4 : IN STD_LOGIC;--商品选择按键4--价钱3.0 select_5 : IN STD_LOGIC;--商品选择按键5--价钱1.0 select_6 : IN STD_LOGIC;--商品选择按键6--价钱2.0 confirm_key_n : IN STD_LOGIC;--确认按键 cancel_key_n : IN STD_LOGIC;--取消按键 coin_1_n : IN STD_LOGIC;--投币1元 coin_2_n : IN STD_LOGIC;--投币0.5元 coin_5_n : IN STD_LOGIC;--投币5元 coin_10_n : IN STD_LOGIC;--投币10元 buy_succeed : OUT STD_LOGIC;--购买成功 bit_select : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--数码管位选 seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选 ); END auto_sell; ARCHITECTURE trans OF auto_sell IS --售货控制模块 component sell_ctrl IS PORT ( clk : IN STD_LOGIC; reset_n : IN STD_LOGIC; confirm_p : IN STD_LOGIC; concel_p : IN STD_LOGIC; select_1 : IN STD_LOGIC;--商品选择按键1--价钱1.0 select_2 : IN STD_LOGIC;--商品选择按键2--价钱1.5 select_3 : IN STD_LOGIC;--商品选择按键3--价钱2.0 select_4 : IN STD_LOGIC;--商品选择按键4--价钱3.0 select_5 : IN STD_LOGIC;--商品选择按键5--价钱1.0 select_6 : IN STD_LOGIC;--商品选择按键6--价钱2.0 coin_1_p : IN STD_LOGIC; coin_2_p : IN STD_LOGIC; coin_5_p : IN STD_LOGIC; coin_10_p : IN STD_LOGIC;--投币10元 buy_succeed : OUT STD_LOGIC; select_num : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); input_money : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); refound_money : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END component; --按键下降沿检测模块 component key_jitter IS PORT ( clkin : IN STD_LOGIC; key_in : IN STD_LOGIC; key_negedge : OUT STD_LOGIC ); END component; --显示模块 component display IS PORT ( clk : IN STD_LOGIC; select_num : IN STD_LOGIC_VECTOR(7 DOWNTO 0); input_money : IN STD_LOGIC_VECTOR(7 DOWNTO 0); refound_money : IN STD_LOGIC_VECTOR(7 DOWNTO 0); bit_select : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END component; SIGNAL select_num : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL input_money : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL refound_money : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL confirm_p : STD_LOGIC; SIGNAL concel_p : STD_LOGIC; SIGNAL coin_1_p : STD_LOGIC; SIGNAL coin_2_p : STD_LOGIC; SIGNAL coin_5_p : STD_LOGIC; SIGNAL coin_10_p : STD_LOGIC; -- Declare intermediate signals for referenced outputs SIGNAL buy_succeed_buf : STD_LOGIC; SIGNAL bit_select_buf : STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL seg_select_buf : STD_LOGIC_VECTOR(7 DOWNTO 0); BEGIN buy_succeed <= buy_succeed_buf; bit_select <= bit_select_buf; seg_select <= seg_select_buf; --调用按键下降沿检测模块 i1_key_jitter : key_jitter PORT MAP ( clkin => clk_50M, key_in => confirm_key_n, key_negedge => confirm_p ); --调用按键下降沿检测模块 i2_key_jitter : key_jitter PORT MAP ( clkin => clk_50M, key_in => cancel_key_n, key_negedge => concel_p ); --调用按键下降沿检测模块 i3_key_jitter : key_jitter PORT MAP ( clkin => clk_50M, key_in => coin_1_n, key_negedge => coin_1_p ); --调用按键下降沿检测模块 i4_key_jitter : key_jitter PORT MAP ( clkin => clk_50M, key_in => coin_2_n, key_negedge => coin_2_p ); --调用按键下降沿检测模块 i5_key_jitter : key_jitter PORT MAP ( clkin => clk_50M, key_in => coin_5_n, key_negedge => coin_5_p ); --调用按键下降沿检测模块 i6_key_jitter : key_jitter PORT MAP ( clkin => clk_50M, key_in => coin_10_n, key_negedge => coin_10_p ); --调用售货控制模块 i_sell_ctrl : sell_ctrl PORT MAP ( clk => clk_50M, reset_n => reset_n, confirm_p => confirm_p, concel_p => concel_p, select_1 => select_1, select_2 => select_2, select_3 => select_3, select_4 => select_4, select_5 => select_5, select_6 => select_6, coin_1_p => coin_1_p, coin_2_p => coin_2_p, coin_5_p => coin_5_p, coin_10_p => coin_10_p, buy_succeed => buy_succeed_buf, select_num => select_num, input_money => input_money, refound_money => refound_money ); --调用显示模块 i_display : display PORT MAP ( clk => clk_50M, select_num => select_num, input_money => input_money, refound_money => refound_money, bit_select => bit_select_buf, seg_select => seg_select_buf ); END trans;

源代码

扫描文章末尾的公众号二维码

958

958

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?