名称:1位全减器设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

给出1位全减器的 Verilog HDL描述。要求

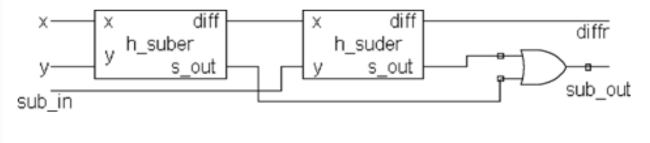

l)首先设计1位半减器,然后用例化语句将它们连接起来,图中 h_ suber是半减器,diff是输出差,Sout是借位输出, sub_in是借位输入

2)根据图设计1位全减器

3)以1位全减器为基本硬件,构成串行借位的8位全减器,要求用例化语句来完成此项设计

(1)将RTL代码复制黏贴到下面

(2)将 testbench仿真测试代码复制黏贴在下方

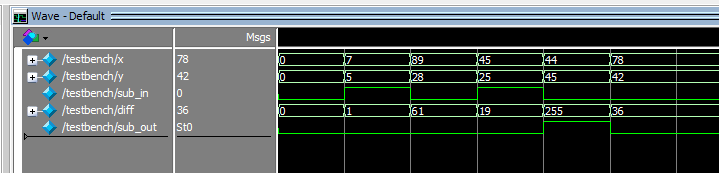

(3)截图波形,波形能够清晰反映所有变量的变化情况

(4)截图RTL视图

module f_suber_8bit(

input [7:0]x,

input [7:0]y,

input sub_in,

output [7:0]diff,

output sub_out

);

wire sub_out1;

wire sub_out2;

wire sub_out3;

wire sub_out4;

wire sub_out5;

wire sub_out6;

wire sub_out7;

f_suber i0_f_suber(

. x(x[0]),

. y(y[0]),

. sub_in(sub_in),

. diff(diff[0]),

. sub_out(sub_out1)

);

f_suber i1_f_suber(

. x(x[1]),

. y(y[1]),

. sub_in(sub_out1),

. diff(diff[1]),

. sub_out(sub_out2)

);

f_suber i2_f_suber(

. x(x[2]),

. y(y[2]),

. sub_in(sub_out2),

. diff(diff[2]),

. sub_out(sub_out3)

);

f_suber i3_f_suber(

. x(x[3]),

. y(y[3]),

. sub_in(sub_out3),

. diff(diff[3]),

. sub_out(sub_out4)

);

f_suber i4_f_suber(

. x(x[4]),

. y(y[4]),

. sub_in(sub_out4),

. diff(diff[4]),

. sub_out(sub_out5)

);

f_suber i5_f_suber(

. x(x[5]),

. y(y[5]),

. sub_in(sub_out5),

. diff(diff[5]),

. sub_out(sub_out6)

);

f_suber i6_f_suber(

. x(x[6]),

. y(y[6]),

. sub_in(sub_out6),

. diff(diff[6]),

. sub_out(sub_out7)

);

f_suber i7_f_suber(

. x(x[7]),

. y(y[7]),

. sub_in(sub_out7),

. diff(diff[7]),

. sub_out(sub_out)

);

endmodule

Testbench代码

module testbench();

reg [7:0]x;

reg [7:0]y;

reg sub_in;

wire [7:0]diff;

wire sub_out;

f_suber_8bit i_f_suber_8bit(

.x(x),

.y(y),

.sub_in(sub_in),

.diff(diff),

.sub_out(sub_out)

);

initial begin

x=0;

y=0;

sub_in=0;

#10;

x=7;

y=5;

sub_in=1;

#10;

x=89;

y=28;

sub_in=0;

#10;

x=45;

y=25;

sub_in=1;

#10;

x=44;

y=45;

sub_in=0;

#10;

x=78;

y=42;

sub_in=0;

#10;

end

endmodule

仿真图

RTL图

部分代码展示:

module f_suber( input x, input y, input sub_in, output diff, output sub_out ); wire diff1; wire s_out1; wire s_out2; h_suber i1_h_suber( . x(x), . y(y), . diff(diff1), . s_out(s_out1) ); h_suber i2_h_suber( . x(diff1), . y(sub_in), . diff(diff), . s_out(s_out2) ); assign sub_out= s_out1 | s_out2; endmodule

源代码

扫描文章末尾的公众号二维码

6124

6124

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?