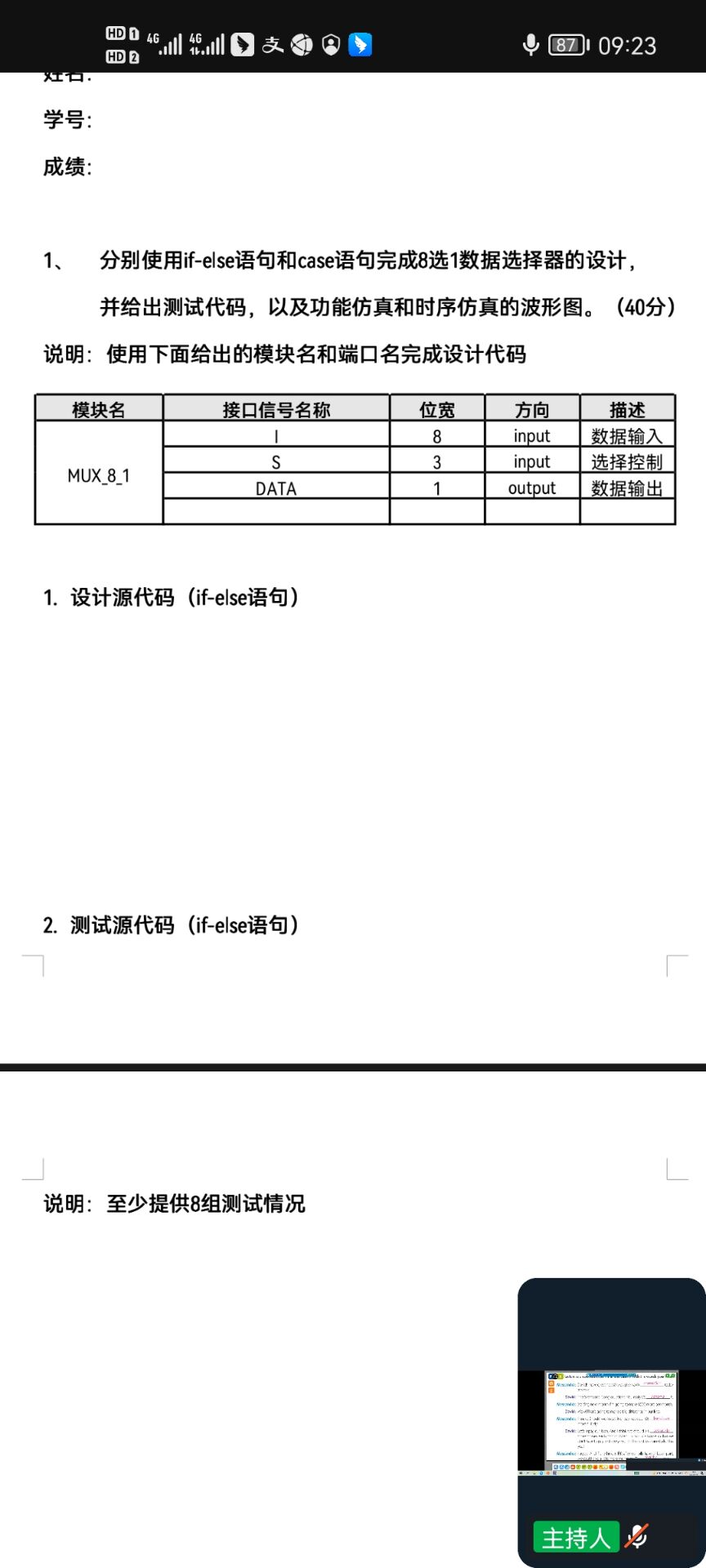

名称:基于FPGA的8选1数据选择器设计Verilog代码ISE仿真(文末获取)

软件:ISE

语言:Verilog

代码功能:

分别使用f-else语句和case语句完成8选1数据选择器的设计并给出测试代码,以及功能仿真和时序仿真的波形图。

说明:使用下面给出的模块名和端口名完成设计代码

设计源码(case)

//8选1数据选择器,使用CASE语句

module MUX_8_1(

input [7:0] I,//输入

input [2:0] S,//控制

output reg DATA //输出

);

always@(S)

case(S)//控制

3'b000:DATA=I[0];

3'b001:DATA=I[1];

3'b010:DATA=I[2];

3'b011:DATA=I[3];

3'b100:DATA=I[4];

3'b101:DATA=I[5];

3'b110:DATA=I[6];

3'b111:DATA=I[7];

default:;

endcase

endmodule

测试源码(case)

`timescale 1ns / 1ps

module test;

// Inputs

reg [7:0] I;

reg [2:0] S;

// Outputs

wire DATA;

// Instantiate the Unit Under Test (UUT)

MUX_8_1 uut (

.I(I),

.S(S),

.DATA(DATA)

);

initial begin

// Initialize Inputs

I = 8'b10100011;//输入

//S为000~111共8种情况

S = 3'b000;

#100;

S = 3'b001;

#100;

S = 3'b010;

#100;

S = 3'b011;

#100;

S = 3'b100;

#100;

S = 3'b101;

#100;

S = 3'b110;

#100;

S = 3'b111;

#100;

end

endmodule

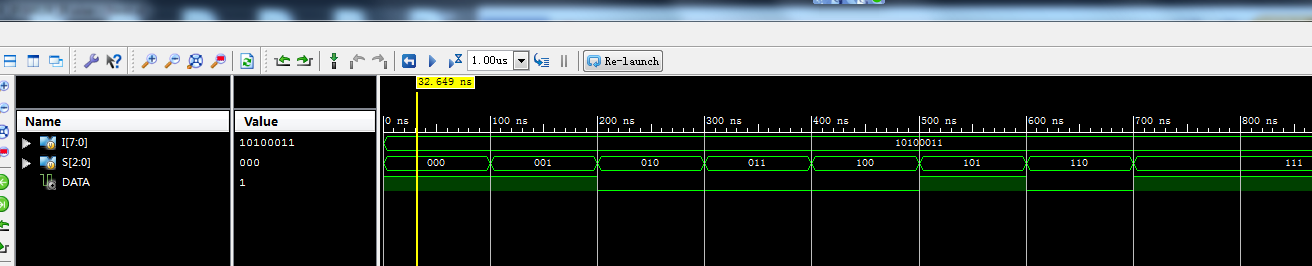

功能仿真

时序仿真

设计源码(if-else)

//8选1数据选择器,使用IF语句

module MUX_8_1(

input [7:0] I,//输入

input [2:0] S,//控制

output reg DATA //输出

);

always@(S)

if(S==3'b000)

DATA=I[0];

else if(S==3'b001)

DATA=I[1];

else if(S==3'b010)

DATA=I[2];

else if(S==3'b011)

DATA=I[3];

else if(S==3'b100)

DATA=I[4];

else if(S==3'b101)

DATA=I[5];

else if(S==3'b110)

DATA=I[6];

else

DATA=I[7];

endmodule

测试源码(if-else)

`timescale 1ns / 1ps

module test;

// Inputs

reg [7:0] I;

reg [2:0] S;

// Outputs

wire DATA;

// Instantiate the Unit Under Test (UUT)

MUX_8_1 uut (

.I(I),

.S(S),

.DATA(DATA)

);

initial begin

// Initialize Inputs

I = 8'b10100011;//输入

//S为000~111共8种情况

S = 3'b000;

#100;

S = 3'b001;

#100;

S = 3'b010;

#100;

S = 3'b011;

#100;

S = 3'b100;

#100;

S = 3'b101;

#100;

S = 3'b110;

#100;

S = 3'b111;

#100;

end

endmodule

功能仿真

时序仿真

部分代码展示:

//8选1数据选择器,使用CASE语句 module MUX_8_1( input [7:0] I,//输入 input [2:0] S,//控制 output reg DATA //输出 ); always@(S) case(S)//控制 3'b000:DATA=I[0]; 3'b001:DATA=I[1]; 3'b010:DATA=I[2]; 3'b011:DATA=I[3]; 3'b100:DATA=I[4]; 3'b101:DATA=I[5];

源代码

扫描文章末尾的公众号二维码

2701

2701

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?