名称:基于FPGA的可变模计数器VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

可变模计数器

1、可以通过按键切换为模10、模12、模24、模60计数器

2、可以通过开关控制正计数还是倒计数(递增计数还是递减计数)

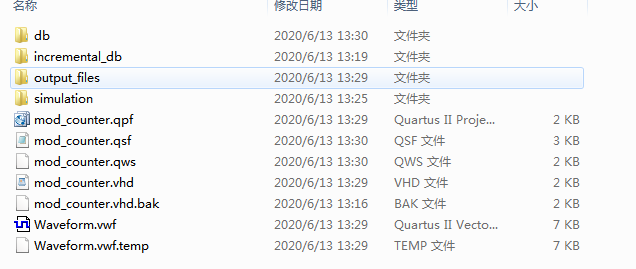

1. 工程文件

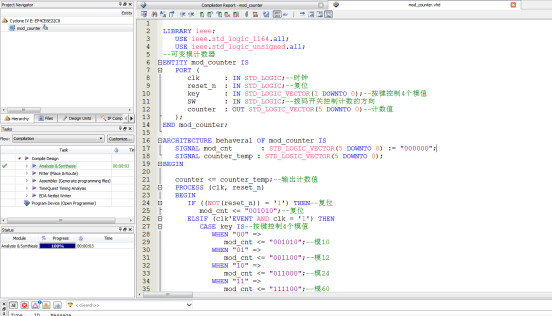

2. 程序文件

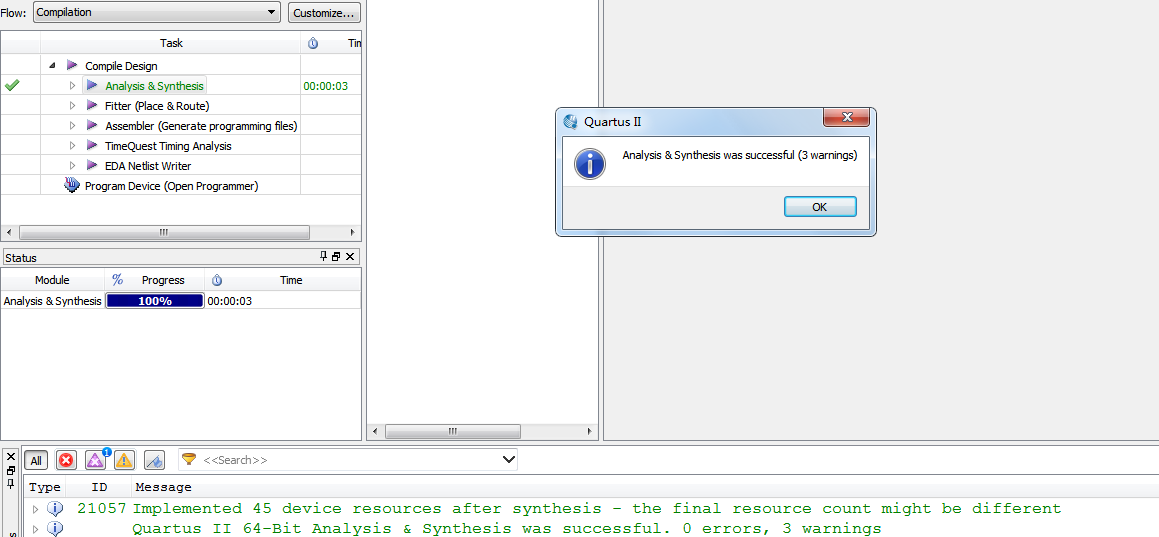

3. 程序编译

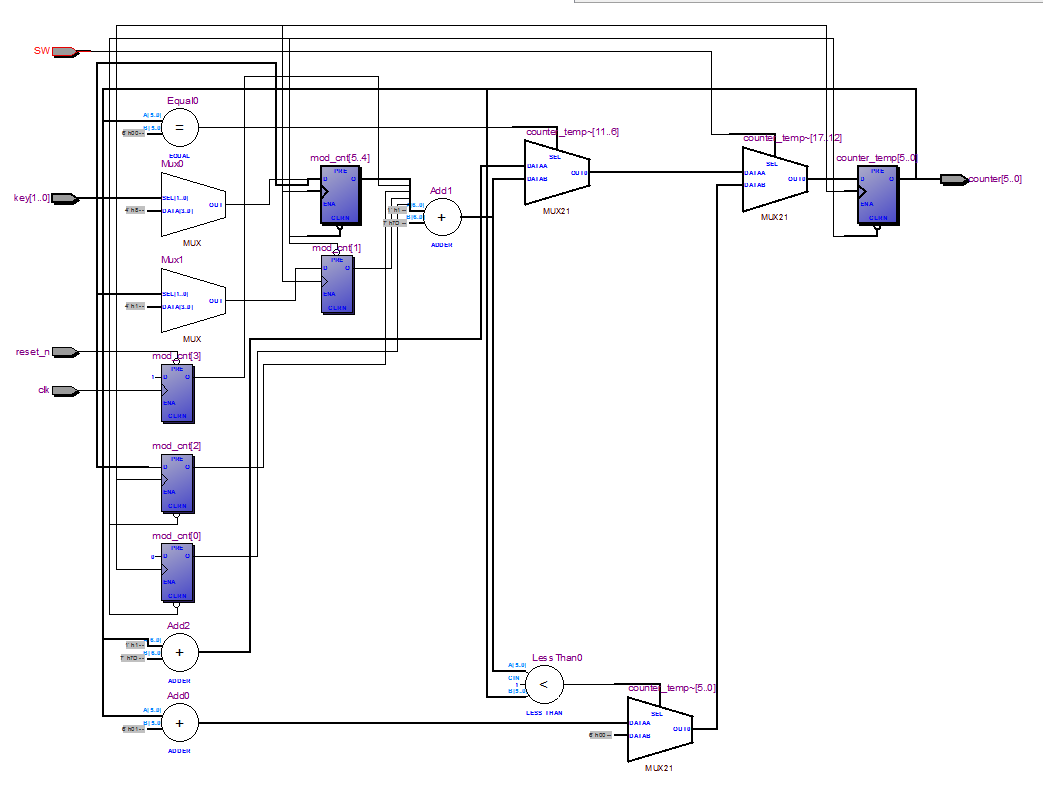

4. RTL图

5. 仿真文件

6. 仿真图

整体仿真图

Key=00,sw=0,模10,递减计数

Key=01,sw=0,模12,递减计数

Key=10,sw=1,模24,递增计数

Key=11,sw=1,模60,递增计数

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --可变模计数器 ENTITY mod_counter IS PORT ( clk : IN STD_LOGIC;--时钟 reset_n : IN STD_LOGIC;--复位 key : IN STD_LOGIC_VECTOR(1 DOWNTO 0);--按键控制4个模值 SW : IN STD_LOGIC;--拨码开关控制计数的方向 counter : OUT STD_LOGIC_VECTOR(5 DOWNTO 0)--计数值 ); END mod_counter; ARCHITECTURE behaveral OF mod_counter IS SIGNAL mod_cnt : STD_LOGIC_VECTOR(5 DOWNTO 0) := "000000"; SIGNAL counter_temp : STD_LOGIC_VECTOR(5 DOWNTO 0); BEGIN counter <= counter_temp;--输出计数值 PROCESS (clk, reset_n) BEGIN IF ((NOT(reset_n)) = '1') THEN--复位 mod_cnt <= "001010";--复位 ELSIF (clk'EVENT AND clk = '1') THEN CASE key IS--按键控制4个模值 WHEN "00" => mod_cnt <= "001010";--模10 WHEN "01" => mod_cnt <= "001100";--模12 WHEN "10" => mod_cnt <= "011000";--模24 WHEN "11" => mod_cnt <= "111100";--模60 WHEN OTHERS => END CASE; END IF; END PROCESS; --计数控制 PROCESS (clk, reset_n) BEGIN IF ((NOT(reset_n)) = '1') THEN counter_temp <= "000000";--复位 ELSIF (clk'EVENT AND clk = '1') THEN

源代码

扫描文章末尾的公众号二维码

2173

2173

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?