名称:基于FPGA的16QAM调制Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

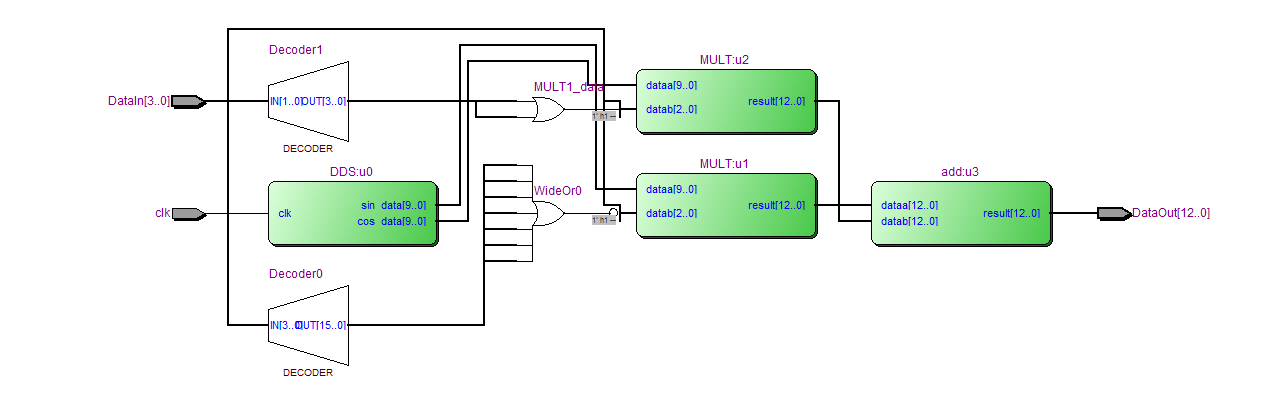

16QAM调制过程可以简化为下图,I路Q路分别乘以cos和sin,再相加即得到调制信号

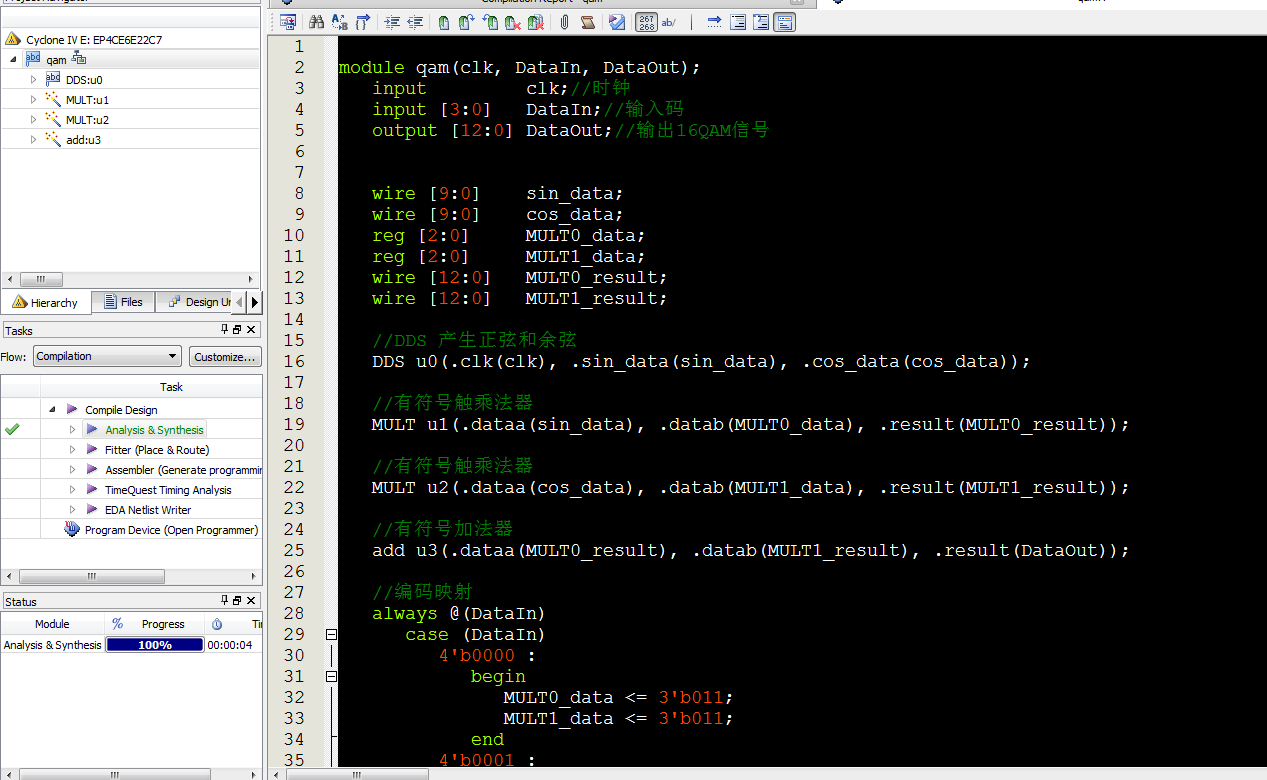

包含正余弦产生模块、有符号乘法器模块、有符号加法器模块以及编码映射

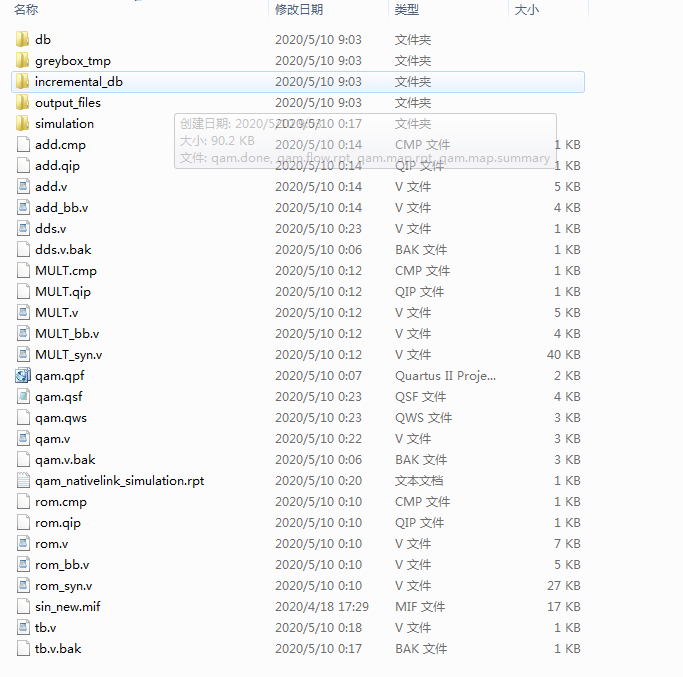

1. 工程文件

2. 程序文件

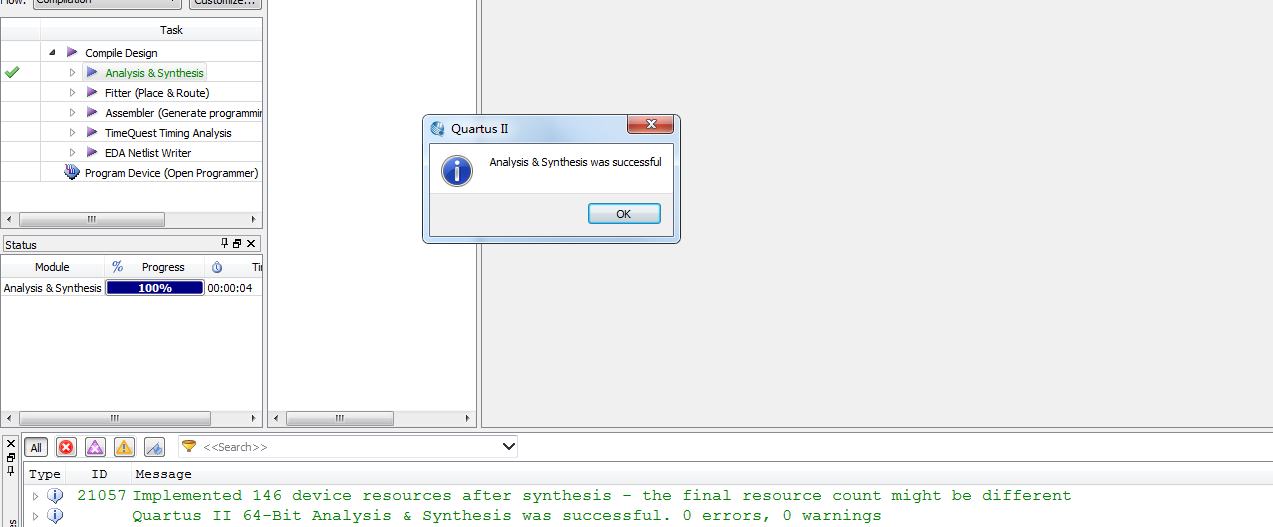

3. 程序编译

4. RTL图

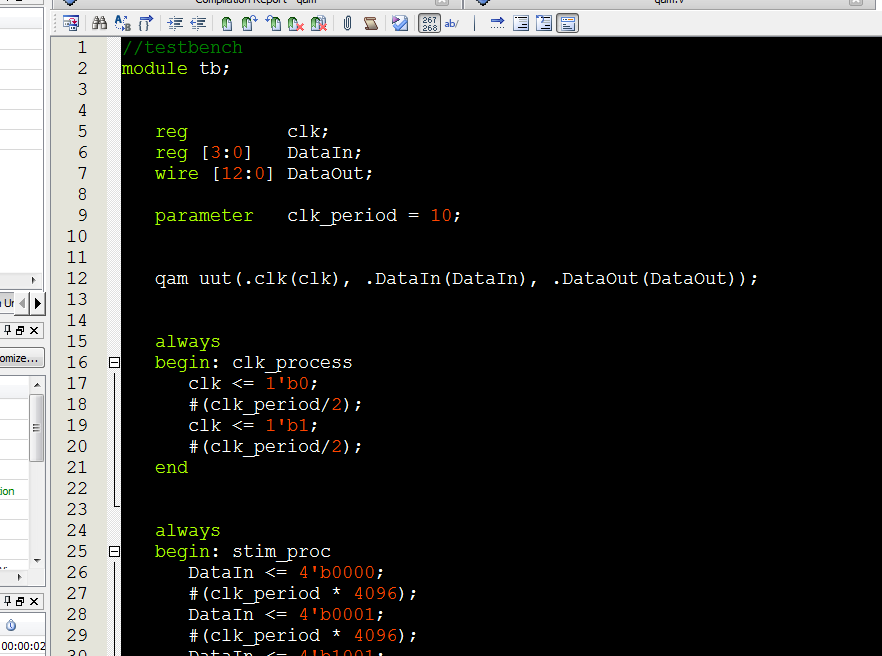

5. Testbench

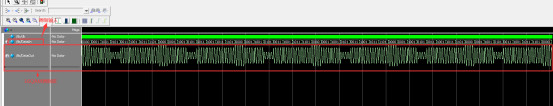

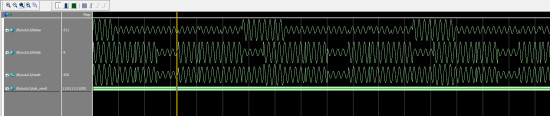

6. 整体仿真

16QAM调制过程可以简化为下图,I路Q路分别乘以cos和sin,再相加即得到调制信号。

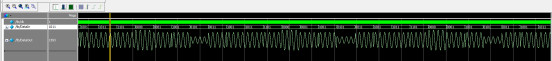

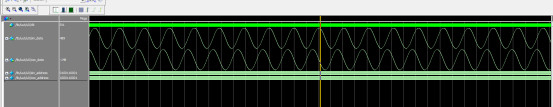

7. DDS模块仿真,用于产生sin和cos

地址sin_address累加,cos_address累加,依次读取ROM里面所存的sin和cos值。输出波形如上图所示。

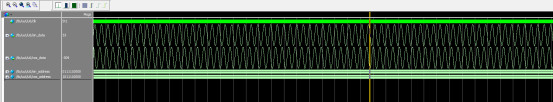

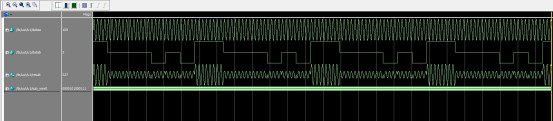

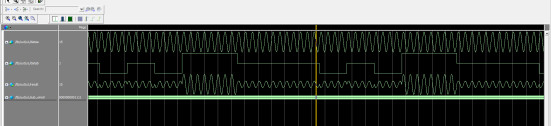

8. 相乘模块仿真

Dataa信号和datab信号相乘得到result信号。可以看到result的幅值包络与datab有关。

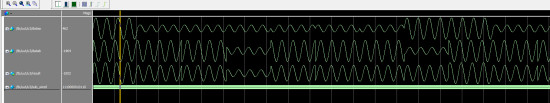

9. 相加模块仿真

相加模块将dataa得值和datab得值相加,得到result得值。result得值即为16QAM调制波形

部分代码展示:

module qam(clk, DataIn, DataOut); input clk;//时钟 input [3:0] DataIn;//输入码 output [12:0] DataOut;//输出16QAM信号 wire [9:0] sin_data; wire [9:0] cos_data; reg [2:0] MULT0_data; reg [2:0] MULT1_data; wire [12:0] MULT0_result; wire [12:0] MULT1_result; //DDS 产生正弦和余弦 DDS u0(.clk(clk), .sin_data(sin_data), .cos_data(cos_data)); //有符号触乘法器 MULT u1(.dataa(sin_data), .datab(MULT0_data), .result(MULT0_result)); //有符号触乘法器 MULT u2(.dataa(cos_data), .datab(MULT1_data), .result(MULT1_result)); //有符号加法器 add u3(.dataa(MULT0_result), .datab(MULT1_result), .result(DataOut)); //编码映射 always @(DataIn) case (DataIn) 4'b0000 : begin MULT0_data <= 3'b011; MULT1_data <= 3'b011; end 4'b0001 : begin MULT0_data <= 3'b001; MULT1_data <= 3'b011; end 4'b0011 : begin MULT0_data <= 3'b111; MULT1_data <= 3'b011; end 4'b0010 : begin MULT0_data <= 3'b101; MULT1_data <= 3'b011; end 4'b0110 : begin MULT0_data <= 3'b101; MULT1_data <= 3'b001; end 4'b0111 : begin MULT0_data <= 3'b111; MULT1_data <= 3'b001; end 4'b0101 : begin MULT0_data <= 3'b001; MULT1_data <= 3'b001; end 4'b0100 : begin MULT0_data <= 3'b011; MULT1_data <= 3'b001; end 4'b1100 : begin MULT0_data <= 3'b011; MULT1_data <= 3'b111; end 4'b1101 : begin MULT0_data <= 3'b011; MULT1_data <= 3'b111; end 4'b1111 : begin MULT0_data <= 3'b111; MULT1_data <= 3'b111; end 4'b1110 : begin MULT0_data <= 3'b101; MULT1_data <= 3'b111; end 4'b1010 : begin MULT0_data <= 3'b101; MULT1_data <= 3'b101; end

源代码

扫描文章末尾的公众号二维码

本文详细介绍了如何使用Verilog语言在FPGA中实现16QAM调制过程,涉及正余弦生成、有符号乘法和加法操作,以及编码映射,同时展示了在Quartus工具中的工程文件、程序文件和RTL图的编译与仿真过程。

本文详细介绍了如何使用Verilog语言在FPGA中实现16QAM调制过程,涉及正余弦生成、有符号乘法和加法操作,以及编码映射,同时展示了在Quartus工具中的工程文件、程序文件和RTL图的编译与仿真过程。

1153

1153

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?