名称:PCM编码复接逻辑设计Verilog代码Quartus仿真(文末获取)

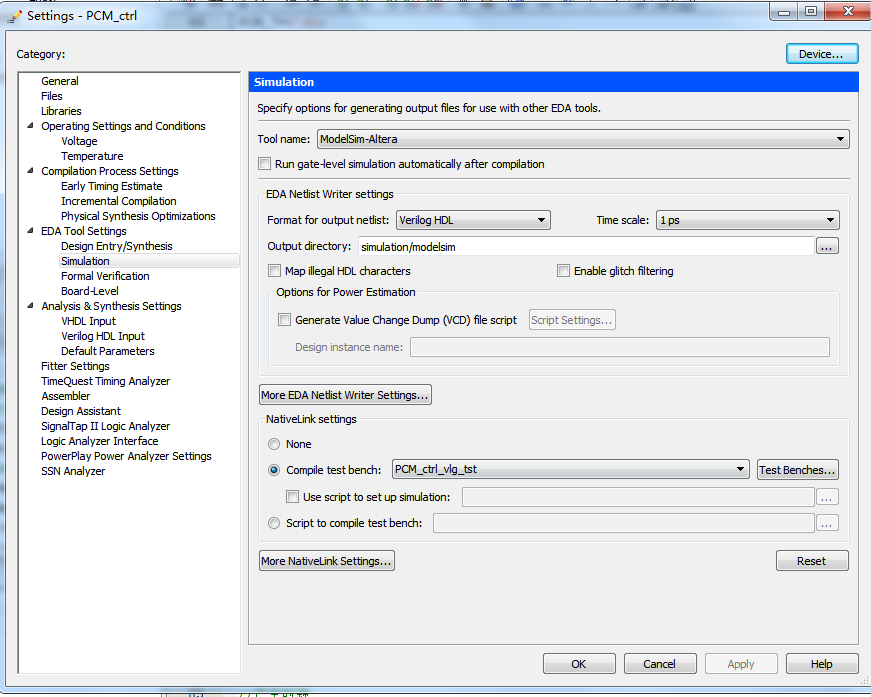

软件:Quartus

语言:Verilog

代码功能:

PCM编码复接逻辑设计

设计内容

利用-PCA开发板,设计一个多路PCM编的接器,已知8路电话信号已经过PCM编码,每路位宽8bit,频率8KZ,以64比特宽度并行输入到复接器,要求复接逻辑能够把8电话路信号顺序排队,以8it宽度,64KHz频率依次输出1一8路电话PCM编码。要求设计实现该功能逻辑,并进行仿真验证。(提示:需要用到嵌RAM作为数据缓冲器,或采用多级流水线结构)

1. 工程文件

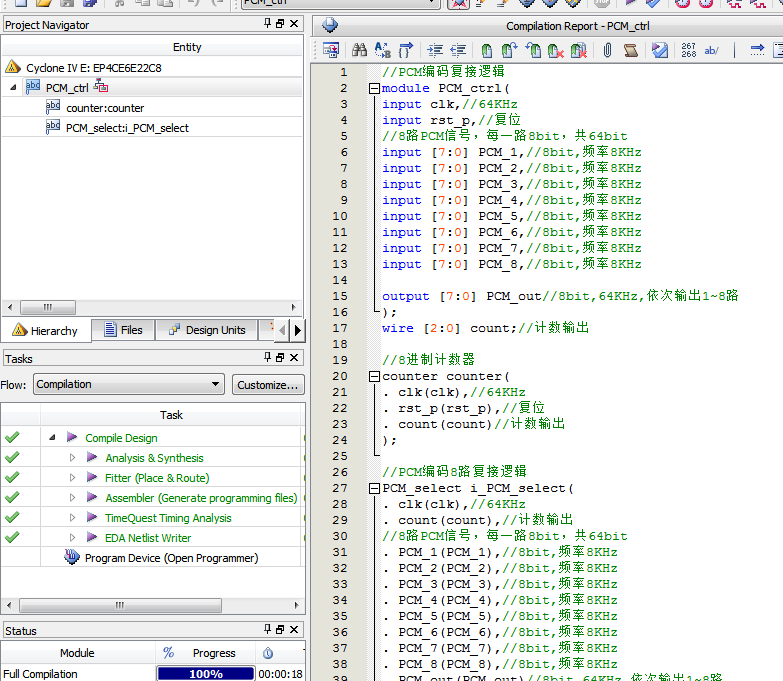

2. 程序文件

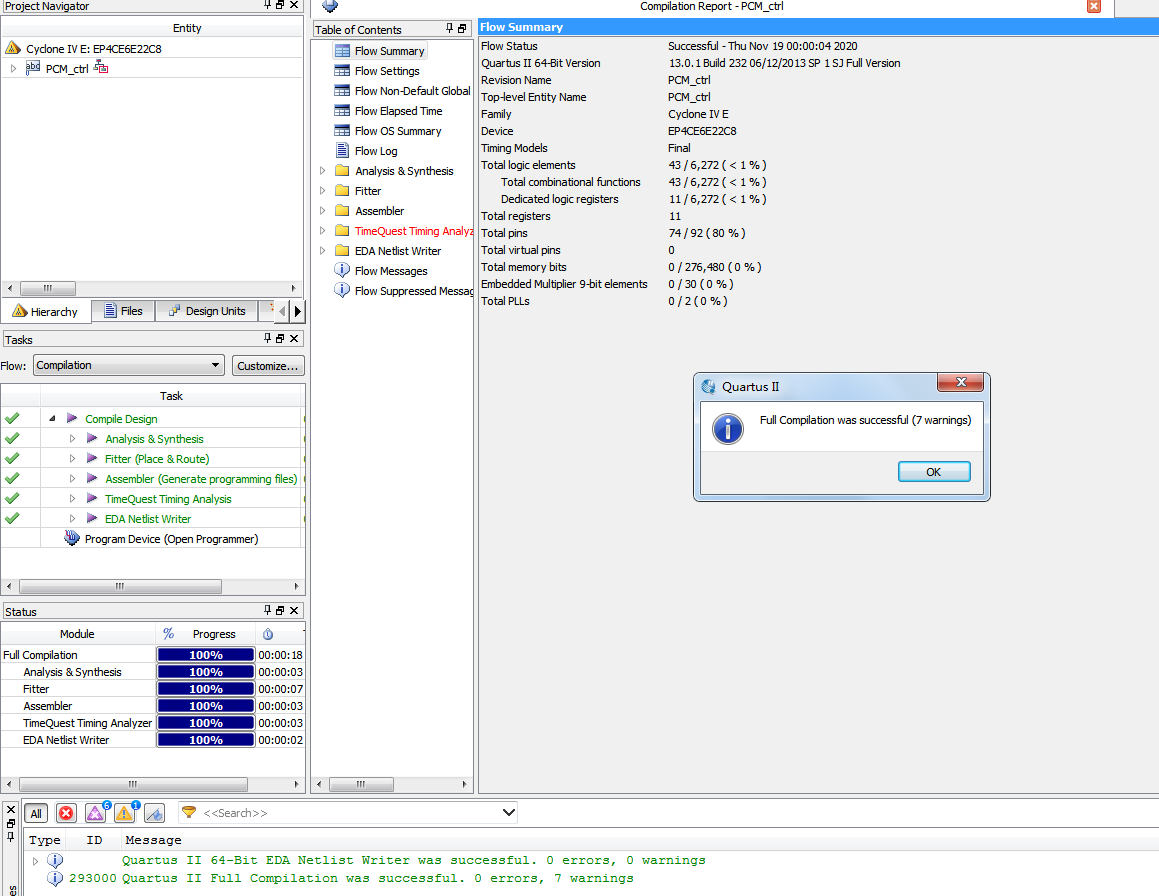

3. 程序编译

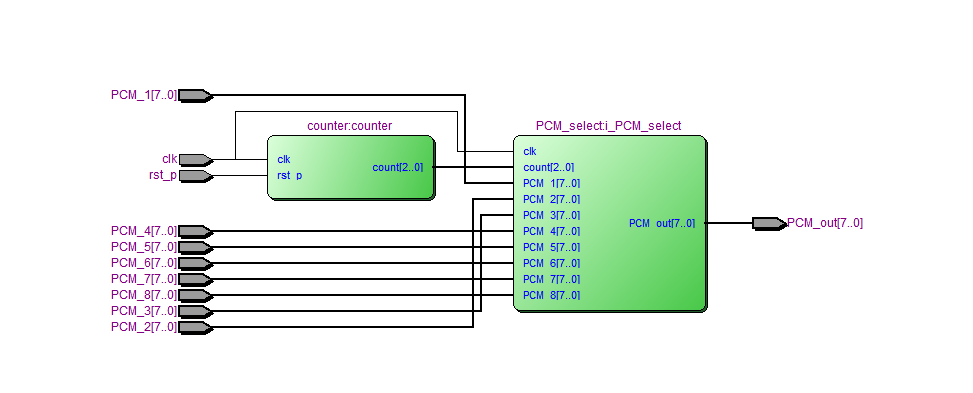

4. RTL图

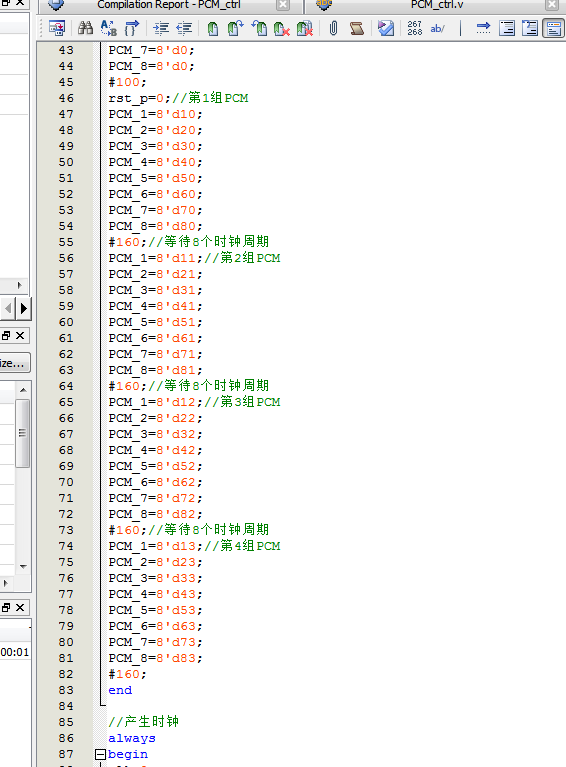

5. Testbench

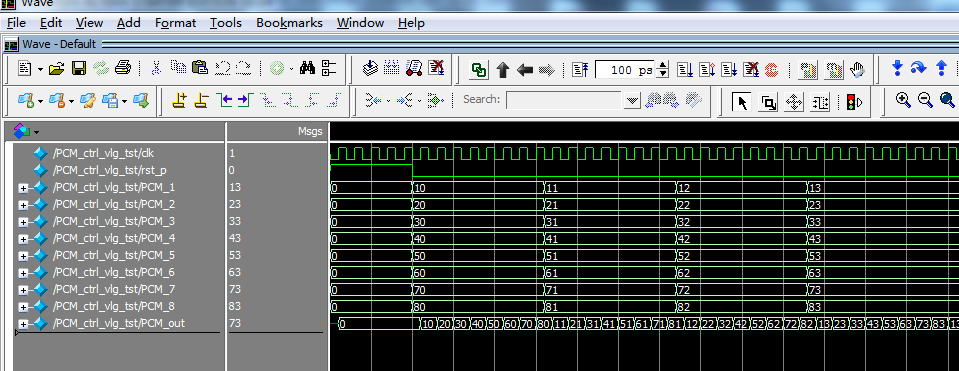

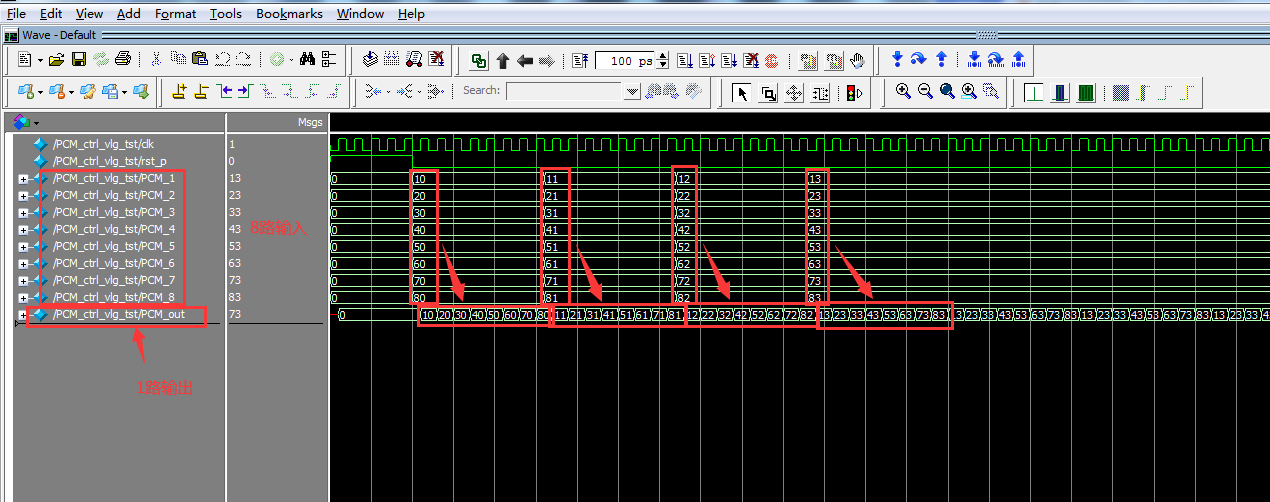

6. 仿真图

8路并行输入的PCM信号,以串行方式依次输出(PCM_out)

部分代码展示:

//PCM编码复接逻辑 module PCM_ctrl( input clk,//64KHz input rst_p,//复位 //8路PCM信号,每一路8bit,共64bit input [7:0] PCM_1,//8bit,频率8KHz input [7:0] PCM_2,//8bit,频率8KHz input [7:0] PCM_3,//8bit,频率8KHz input [7:0] PCM_4,//8bit,频率8KHz input [7:0] PCM_5,//8bit,频率8KHz input [7:0] PCM_6,//8bit,频率8KHz input [7:0] PCM_7,//8bit,频率8KHz input [7:0] PCM_8,//8bit,频率8KHz output [7:0] PCM_out//8bit,64KHz,依次输出1~8路 ); wire [2:0] count;//计数输出 //8进制计数器 counter counter( . clk(clk),//64KHz . rst_p(rst_p),//复位 . count(count)//计数输出 ); //PCM编码8路复接逻辑 PCM_select i_PCM_select( . clk(clk),//64KHz . count(count),//计数输出 //8路PCM信号,每一路8bit,共64bit . PCM_1(PCM_1),//8bit,频率8KHz . PCM_2(PCM_2),//8bit,频率8KHz . PCM_3(PCM_3),//8bit,频率8KHz . PCM_4(PCM_4),//8bit,频率8KHz . PCM_5(PCM_5),//8bit,频率8KHz . PCM_6(PCM_6),//8bit,频率8KHz . PCM_7(PCM_7),//8bit,频率8KHz . PCM_8(PCM_8),//8bit,频率8KHz . PCM_out(PCM_out)//8bit,64KHz,依次输出1~8路 ); endmodule

源代码

扫描文章末尾的公众号二维码

214

214

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?