名称:基于FPGA的自动售货机设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

自动售货机设计

要求

1.利用外部按键当作外部的输入,利用数码管、蜂鸣器和LED作为输出表示。

2.外部输入有1元的按键、0.5元的按键和选择商品的按键。

3.无论什么按键按下,蜂鸣器都要出声音

4.共有两种商品,一种商品2.5元,另一种商品3.5元。

5.在投钱之前,必须要选择商品,如果没有选择,则默认第一种(2.5元)。投钱的过程中,不允许更换商品。每次卖出商品或者钱数被清零的话,商品也要恢复默认。

6.第一个数码管显示选择的商品(1:优表2.5元商品。2:代表3.5元的商品)

7.最后两个数码管显示当前所投入的钱数(中间的点需要点亮)

8.2.5元的商品卖出采用1个LED亮1s来表示。3.5元的商品卖出采用2个LED亮1s来表示

9.找零的话,采用1个LED呼吸灯(呼吸4S)。

10.投钱过程中,需要倒计时,倒计时的时间为1min。如果1min之内没有连续投入钱币,则钱数自动清零。倒计时,显示在第二个和第三个数码管上

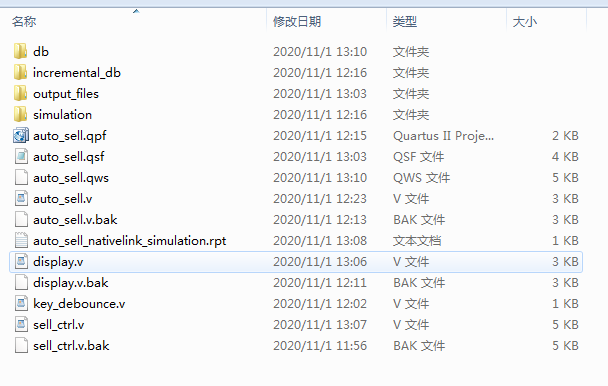

1. 工程文件

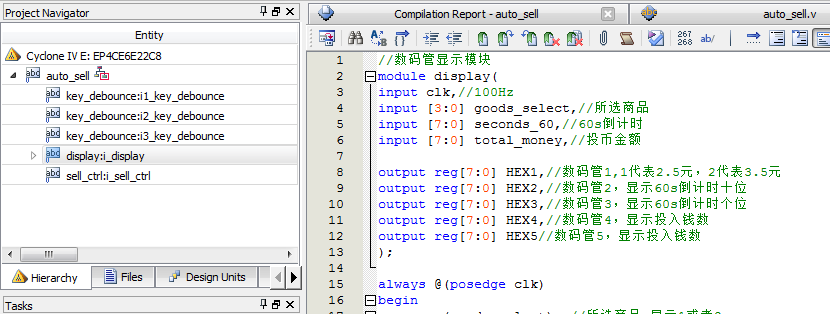

2. 程序文件

3. 程序编译

4. RTL图

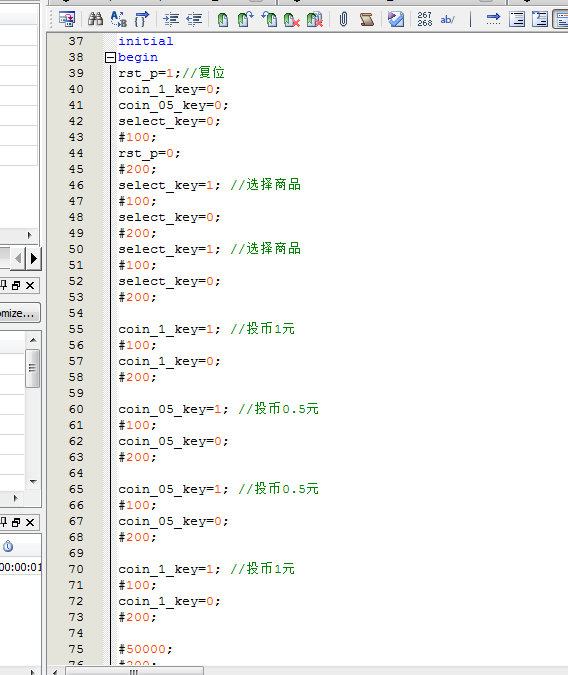

5. Testbench

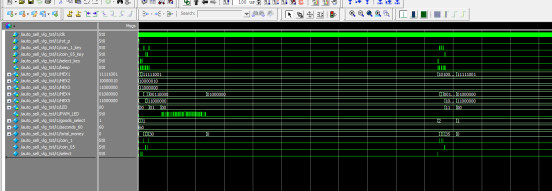

6. 仿真图

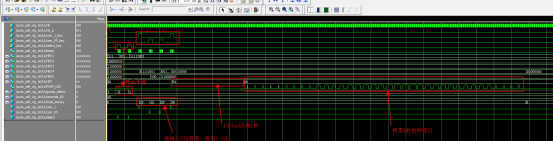

整体仿真图

下图为选择2.5元商品,投币1+0.5+0.5+1=3元,有找零的仿真过程

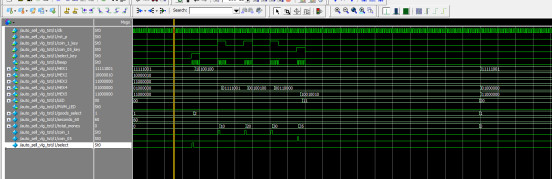

下图为选择3.5元商品,投币1+1+1+0.5=3.5元,没有找零的仿真过程

可以看到led点亮1秒后,回到默认选择2.5元商品(goods_select=1)

部分代码展示:

//售货机 module auto_sell( input clk,//100Hz input rst_p,//复位 input coin_1_key,//1元输入按键 input coin_05_key,//0.5元输入按键 input select_key,//商品选择按键 output beep,//蜂鸣器 output [7:0] HEX1,//数码管1,1代表2.5元,2代表3.5元 output [7:0] HEX2,//数码管2,显示60s倒计时 output [7:0] HEX3,//数码管3,显示60s倒计时 output [7:0] HEX4,//数码管4,显示投入钱数 output [7:0] HEX5,//数码管5,显示投入钱数 output [1:0]LED,//卖出,2.5元1个LED亮,3.5元2个led亮 output PWM_LED//找零呼吸灯 ); wire [3:0] goods_select;//所选商品 wire [7:0] seconds_60;//60s倒计时 wire [7:0] total_money;//投币金额 wire coin_1; wire coin_05; wire select; //按键响蜂鸣器 assign beep=(coin_1_key | coin_05_key | select_key) & clk; //按键控制,将按键转换为1个时钟的高电平信号 key_debounce i1_key_debounce( . clk(clk),//100Hz . key_in(coin_1_key),//按键输入 . key_out(coin_1)//1个时钟的高电平信号输出 ); //按键控制,将按键转换为1个时钟的高电平信号 key_debounce i2_key_debounce( . clk(clk),//100Hz . key_in(coin_05_key),//按键输入 . key_out(coin_05)//1个时钟的高电平信号输出 ); //按键控制,将按键转换为1个时钟的高电平信号 key_debounce i3_key_debounce( . clk(clk),//100Hz . key_in(select_key),//按键输入 . key_out(select)//1个时钟的高电平信号输出 ); //售货机控制模块 sell_ctrl i_sell_ctrl( . clk(clk),//100Hz . rst_p(rst_p),//复位 . coin_1(coin_1),//1元输入,一个时钟高电平 . coin_05(coin_05),//0.5元输入,一个时钟高电平 . select(select),//商品选择,一个时钟高电平 . goods_select(goods_select),//所选商品 . seconds_60(seconds_60),//60s倒计时 . total_money(total_money),//投币金额 . LED(LED),//卖出,2.5元1个LED亮,3.5元2个led亮 . PWM_LED(PWM_LED)//找零呼吸灯 ); //数码管显示模块 display i_display( . clk(clk),//100Hz . goods_select(goods_select),//所选商品 . seconds_60(seconds_60),//60s倒计时 . total_money(total_money),//投币金额 . HEX1(HEX1),//数码管1,1代表2.5元,2代表3.5元 . HEX2(HEX2),//数码管2,显示60s倒计时十位 . HEX3(HEX3),//数码管3,显示60s倒计时个位 . HEX4(HEX4),//数码管4,显示投入钱数 . HEX5(HEX5)//数码管5,显示投入钱数 ); endmodule

源代码

扫描文章末尾的公众号二维码

1773

1773

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?