名称:基于FPGA的14位全加器设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

14位全加器

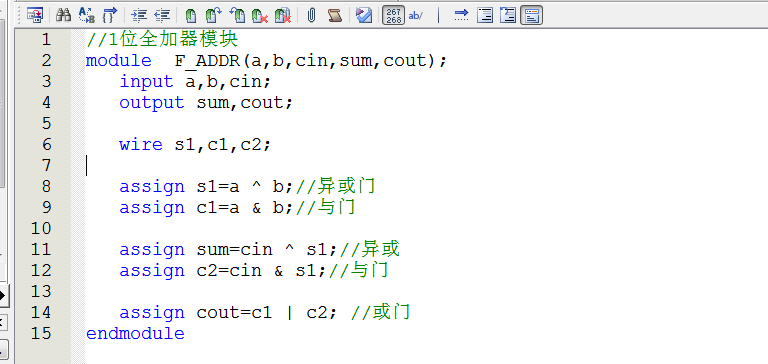

设计1位全加器,并将1位全加器组合为14位全加器

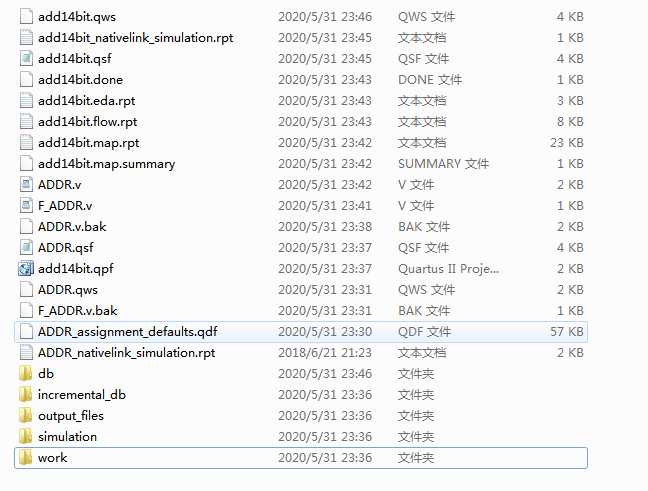

1.程序工程文件

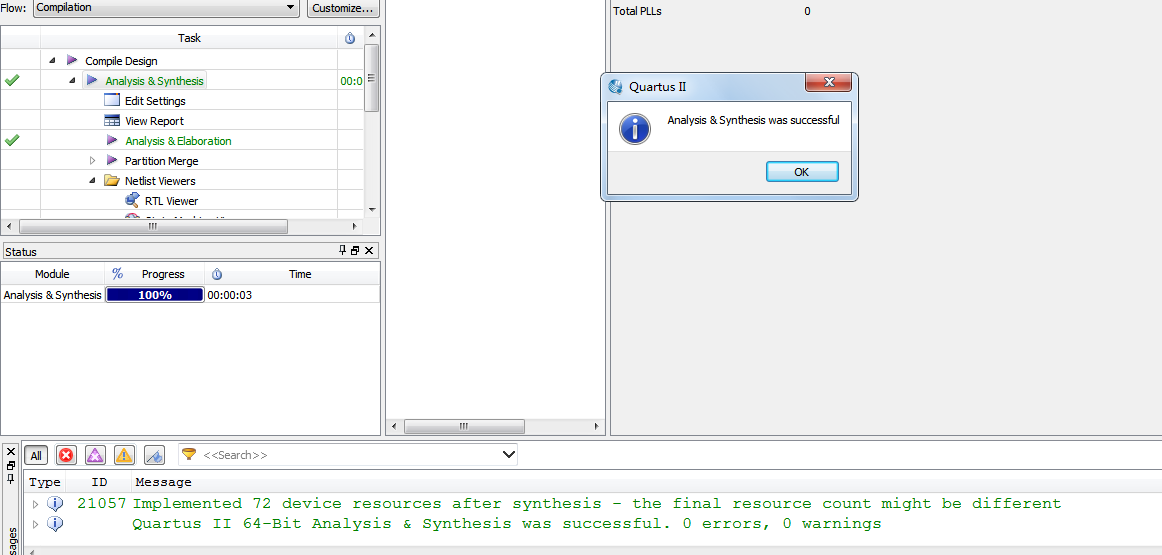

2.程序运行

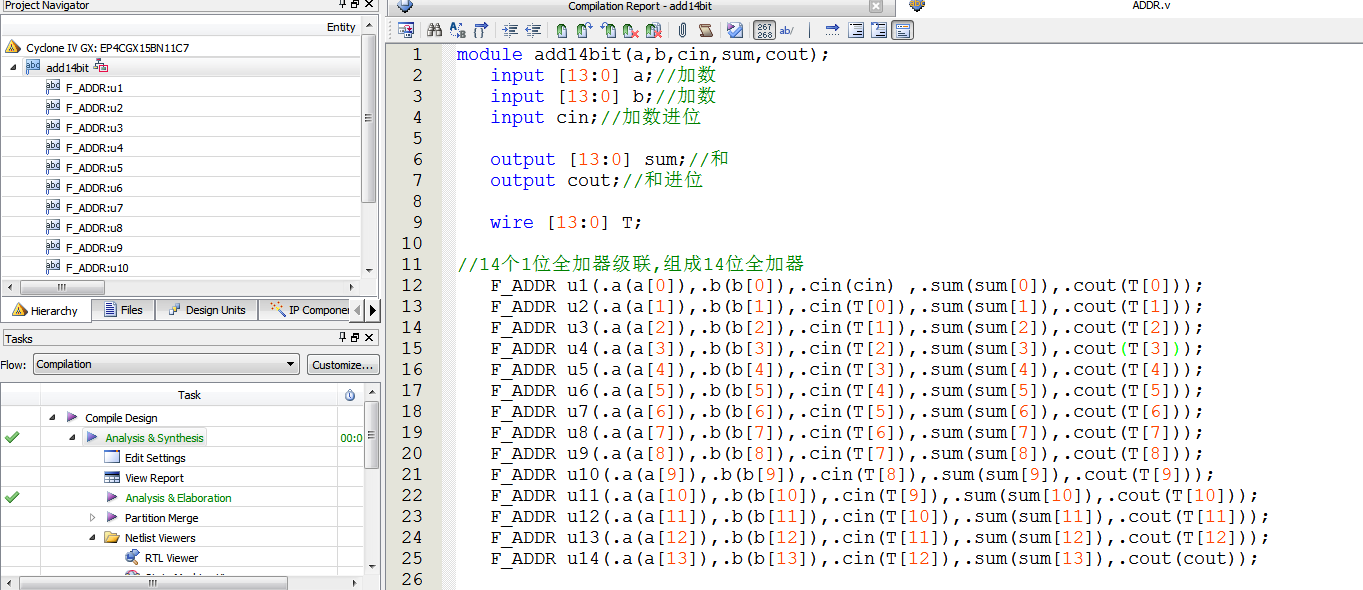

3.程序文件

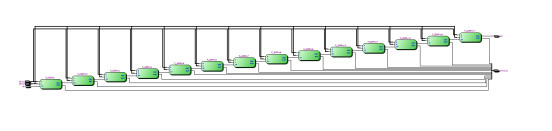

4.程序结构(RTL图)

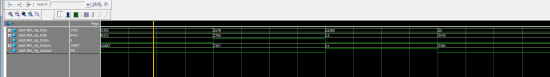

5.程序仿真

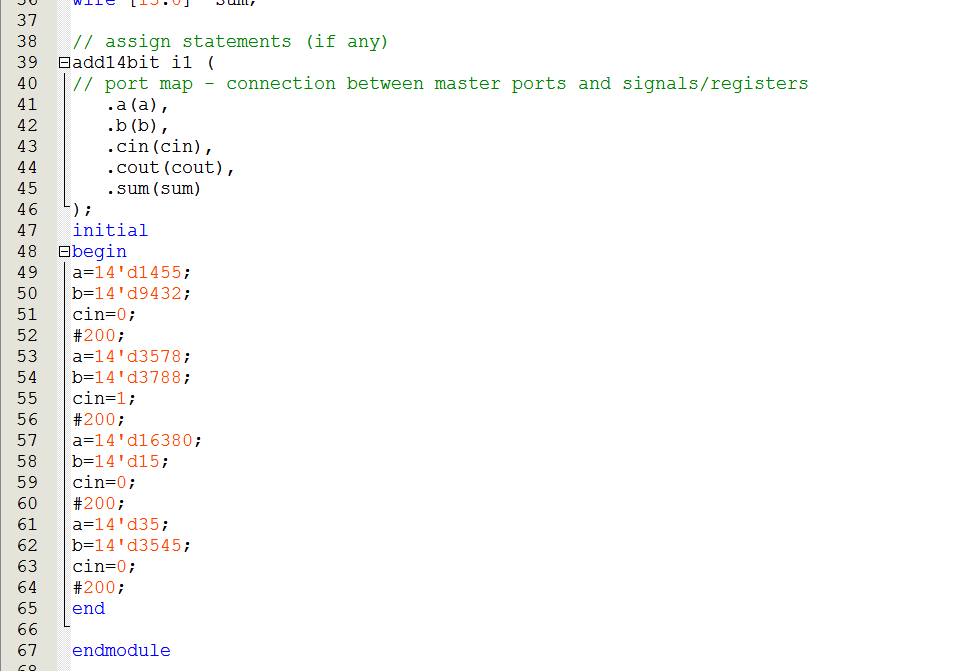

testbench

十进制表示

部分代码展示:

module add14bit(a,b,cin,sum,cout); input [13:0] a;//加数 input [13:0] b;//加数 input cin;//加数进位 output [13:0] sum;//和 output cout;//和进位 wire [13:0] T; //14个1位全加器级联,组成14位全加器 F_ADDR u1(.a(a[0]),.b(b[0]),.cin(cin) ,.sum(sum[0]),.cout(T[0])); F_ADDR u2(.a(a[1]),.b(b[1]),.cin(T[0]),.sum(sum[1]),.cout(T[1])); F_ADDR u3(.a(a[2]),.b(b[2]),.cin(T[1]),.sum(sum[2]),.cout(T[2])); F_ADDR u4(.a(a[3]),.b(b[3]),.cin(T[2]),.sum(sum[3]),.cout(T[3])); F_ADDR u5(.a(a[4]),.b(b[4]),.cin(T[3]),.sum(sum[4]),.cout(T[4])); F_ADDR u6(.a(a[5]),.b(b[5]),.cin(T[4]),.sum(sum[5]),.cout(T[5])); F_ADDR u7(.a(a[6]),.b(b[6]),.cin(T[5]),.sum(sum[6]),.cout(T[6])); F_ADDR u8(.a(a[7]),.b(b[7]),.cin(T[6]),.sum(sum[7]),.cout(T[7])); F_ADDR u9(.a(a[8]),.b(b[8]),.cin(T[7]),.sum(sum[8]),.cout(T[8])); F_ADDR u10(.a(a[9]),.b(b[9]),.cin(T[8]),.sum(sum[9]),.cout(T[9])); F_ADDR u11(.a(a[10]),.b(b[10]),.cin(T[9]),.sum(sum[10]),.cout(T[10])); F_ADDR u12(.a(a[11]),.b(b[11]),.cin(T[10]),.sum(sum[11]),.cout(T[11])); F_ADDR u13(.a(a[12]),.b(b[12]),.cin(T[11]),.sum(sum[12]),.cout(T[12])); F_ADDR u14(.a(a[13]),.b(b[13]),.cin(T[12]),.sum(sum[13]),.cout(cout)); endmodule

源代码

扫描文章末尾的公众号二维码

2230

2230

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?