名称:基于FPGA的16位加法器设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

16位加法器

1、设计4位加法器

2、将4个加法器并联组成16位加法器

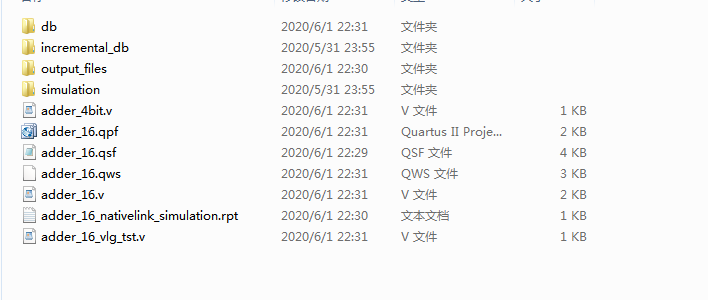

1. 工程文件

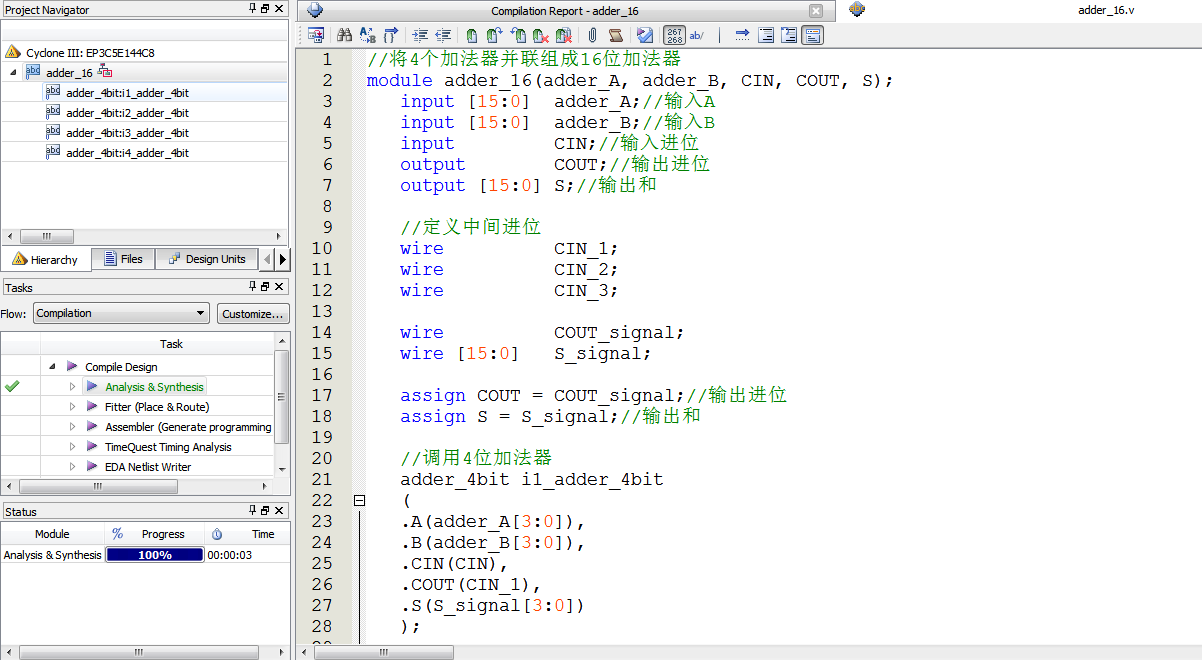

2. 程序文件

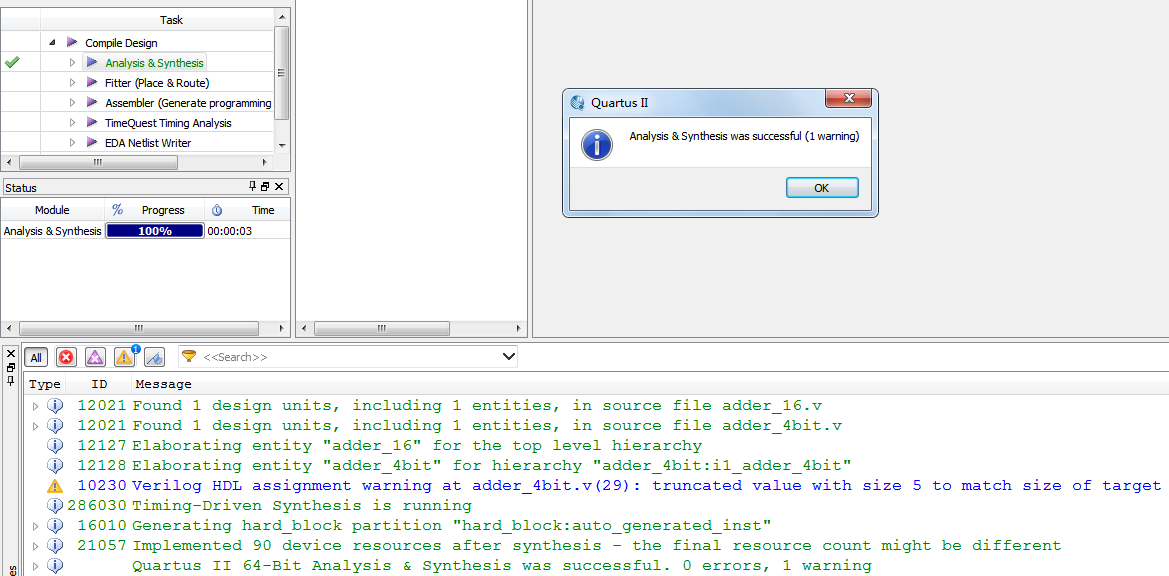

3. 程序编译

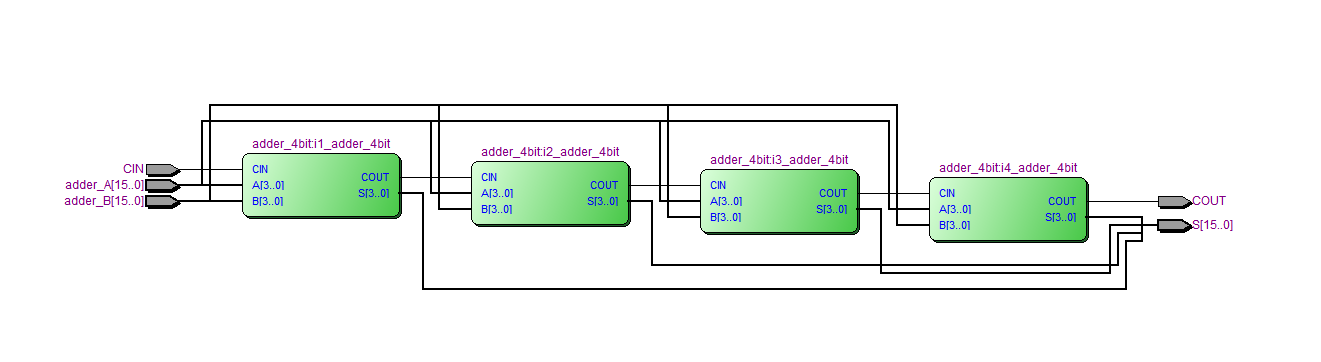

4. RTL图

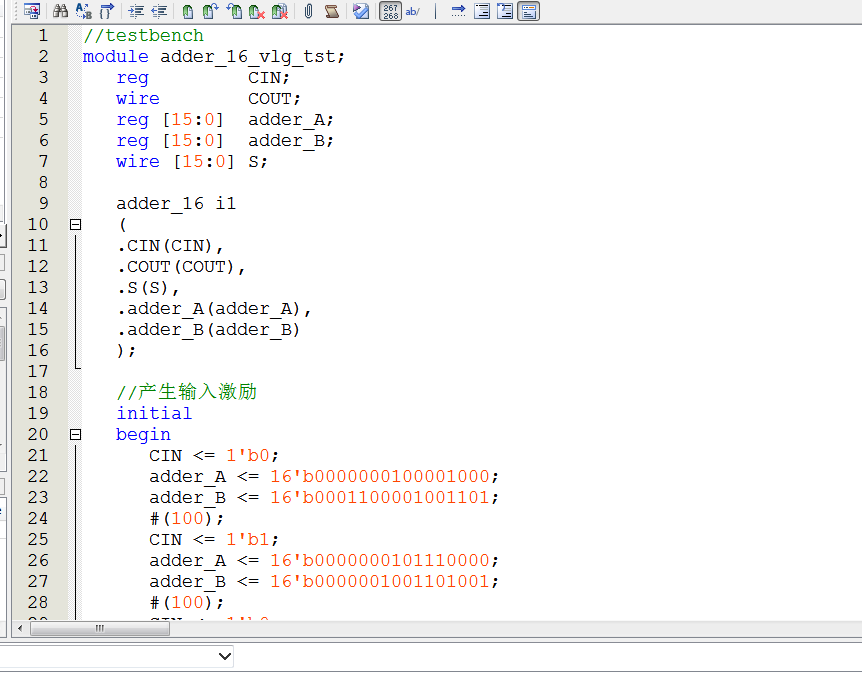

5. Testbench

6. 仿真图

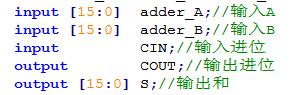

部分代码展示:

//将4个加法器并联组成16位加法器 module adder_16(adder_A, adder_B, CIN, COUT, S); input [15:0] adder_A;//输入A input [15:0] adder_B;//输入B input CIN;//输入进位 output COUT;//输出进位 output [15:0] S;//输出和 //定义中间进位 wire CIN_1; wire CIN_2; wire CIN_3; wire COUT_signal; wire [15:0] S_signal; assign COUT = COUT_signal;//输出进位 assign S = S_signal;//输出和 //调用4位加法器 adder_4bit i1_adder_4bit ( .A(adder_A[3:0]), .B(adder_B[3:0]), .CIN(CIN), .COUT(CIN_1), .S(S_signal[3:0]) ); //调用4位加法器 adder_4bit i2_adder_4bit ( .A(adder_A[7:4]), .B(adder_B[7:4]), .CIN(CIN_1), .COUT(CIN_2), .S(S_signal[7:4]) ); //调用4位加法器 adder_4bit i3_adder_4bit ( .A(adder_A[11:8]), .B(adder_B[11:8]), .CIN(CIN_2), .COUT(CIN_3), .S(S_signal[11:8]) ); //调用4位加法器 adder_4bit i4_adder_4bit ( .A(adder_A[15:12]), .B(adder_B[15:12]), .CIN(CIN_3), .COUT(COUT_signal), .S(S_signal[15:12]) ); endmodule

源代码

扫描文章末尾的公众号二维码

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?