名称:基于FPGA的CPU的ALU数据通路设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

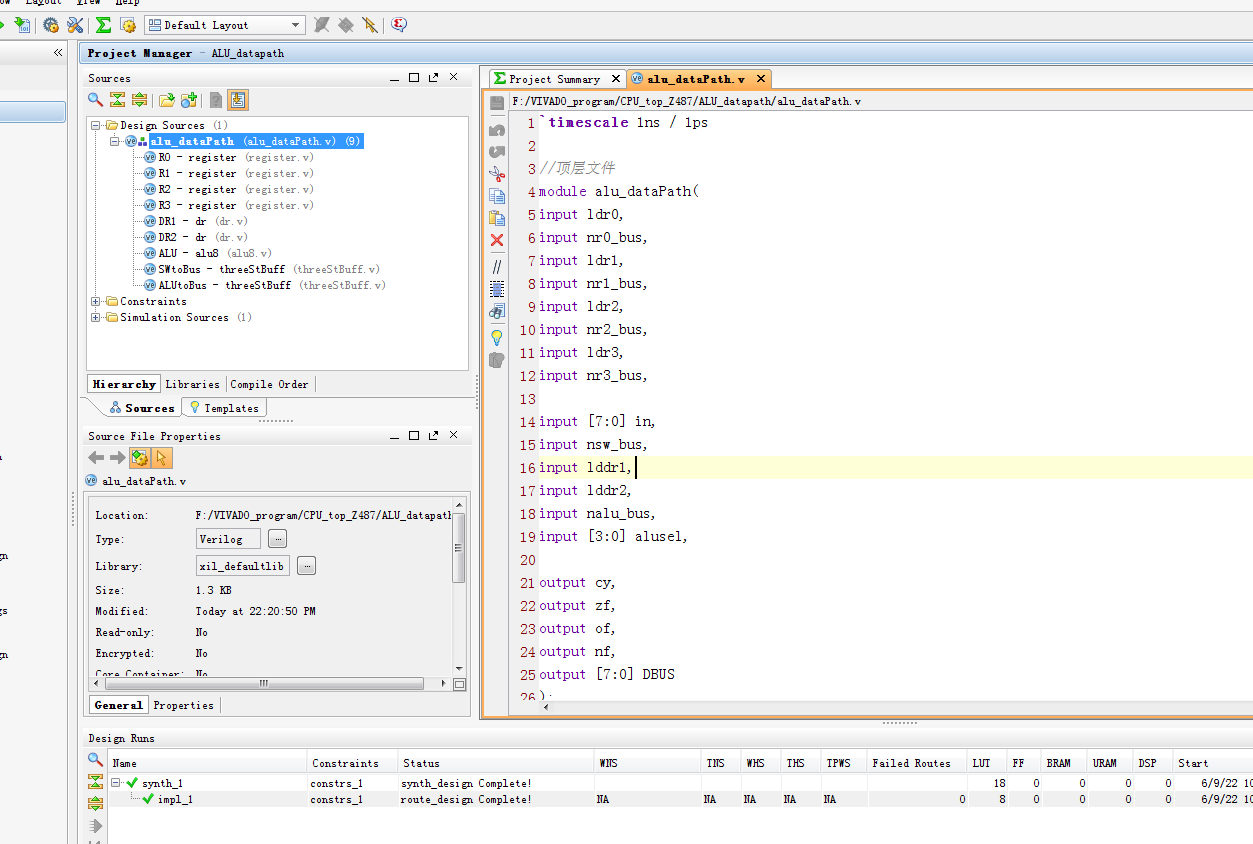

![]()

ALU数据通路

一、分析

1.ALU模块(alu8.v)的控制信号:

综合考虑,确定ALU输入输出信号如下:

| 方向 | 信号名 | 说明 |

| 输入 | a[7:0] | 操作数1 |

| 输入 | b[7:0] | 操作数2 |

| 输入 | alusel[3:0] | 运算功能选择。实验任务1要求设计加/减法器电路,实验任务2要设计具有13个功能的ALU模块。所以,确定该信号位宽位4bits。 |

| 输出 | y[7:0] | 运算结果 |

| 输出 | zf | 0标志。运算结果=0时,zf=1;否则,zf=0 |

| 输出 | cy | 进位标志。运算结果有进位或借位时,cy=1;否则,cy=0。仅用于算术运算。 |

| 输出 | of | 溢出标志。运算结果溢出时,of=1;否则,of=0。仅用于算术运算。 |

| 输出 | nf | 负数标志。运算结果为负时,nf=1;否则,nf=0。仅用于算术运算。 |

2. 输入/输出缓冲器(threeStBuff.v)模块的控制信号:

综合考虑,确定输入/输出缓冲器的输入输出信号如下:

| 方向 | 信号名 | 说明 |

| 输入 | DataIn[7:0] | 输入数据 |

| 输入 | nDataToBus | 输入控制,nDataToBus=0时,缓冲器打开;否则输出端为高阻态。 |

| 输出 | DataOut[7:0] | 输出数据,三态 |

本次实验的输入缓冲和ALU的输出缓冲采用此模块。

3. 寄存器(不带输出控制)(dr.v)模块的控制信号:

综合考虑,确定寄存器(不带输出控制)的输入输出信号如下:

| 方向 | 信号名 | 说明 |

| 输入 | d[7:0] | 输入数据 |

| 输入 | lddr | 输入数据锁存信号。上升沿时刻,输入存入。 |

| 输入 | clrn | 输入控制。clrn =0时,寄存器复位,即输出q[7:0]为0。 |

| 输出 | q[7:0] | 输出数据 |

本次实验的DR1和DR2采用此模块。

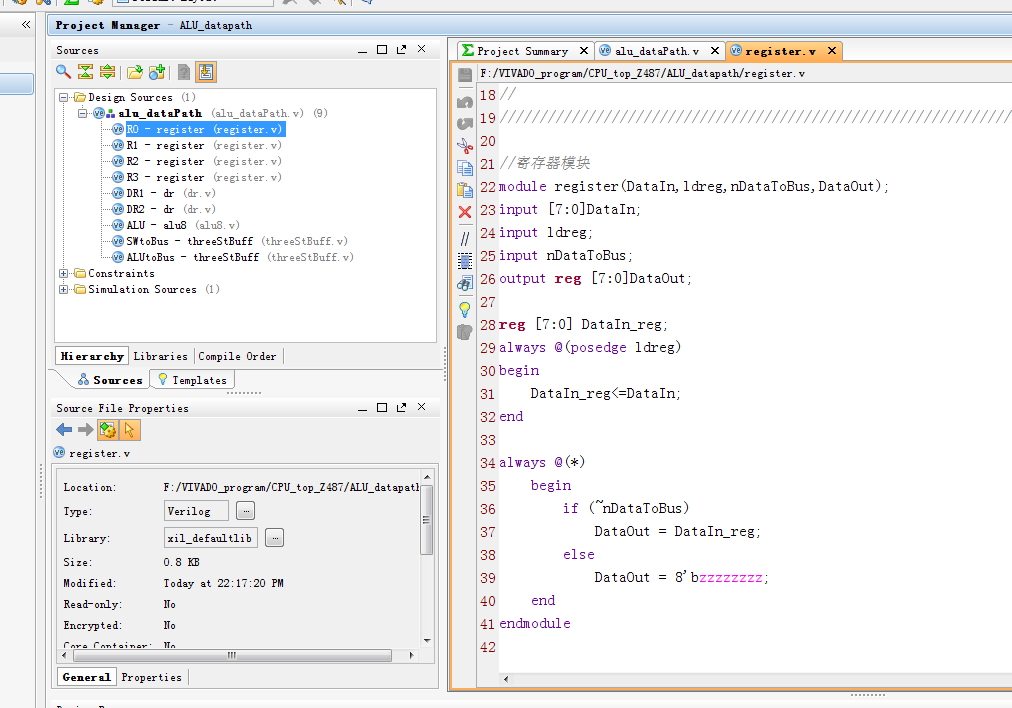

4. 三态缓冲寄存器(register.v)模块的控制信号:

综合考虑,确定寄存器(不带输出控制)的输入输出信号如下:

| 方向 | 信号名 | 说明 |

| 输入 | DataIn[7:0] | 输入数据 |

| 输入 | ldreg | 输入数据锁存信号。上升沿时刻,输入存入。 |

| 输入 | nDataToBus | 输入控制,nDataToBus=0时,寄存器锁存的值输出;否则输出端为高阻态。 |

| 输出 | DataOut[7:0] | 输出数据 |

本次实验的R0,R1,R2和R3采用此模块。

请参考下列源文件,设计具有上述功能的电路模块。

(1)修改参考文件alu8.v的内容,分别实现实验任务1和实验任务2的要求。

(2)参考dr.v和threeStBuff.v,设计三态缓冲寄存器模块。

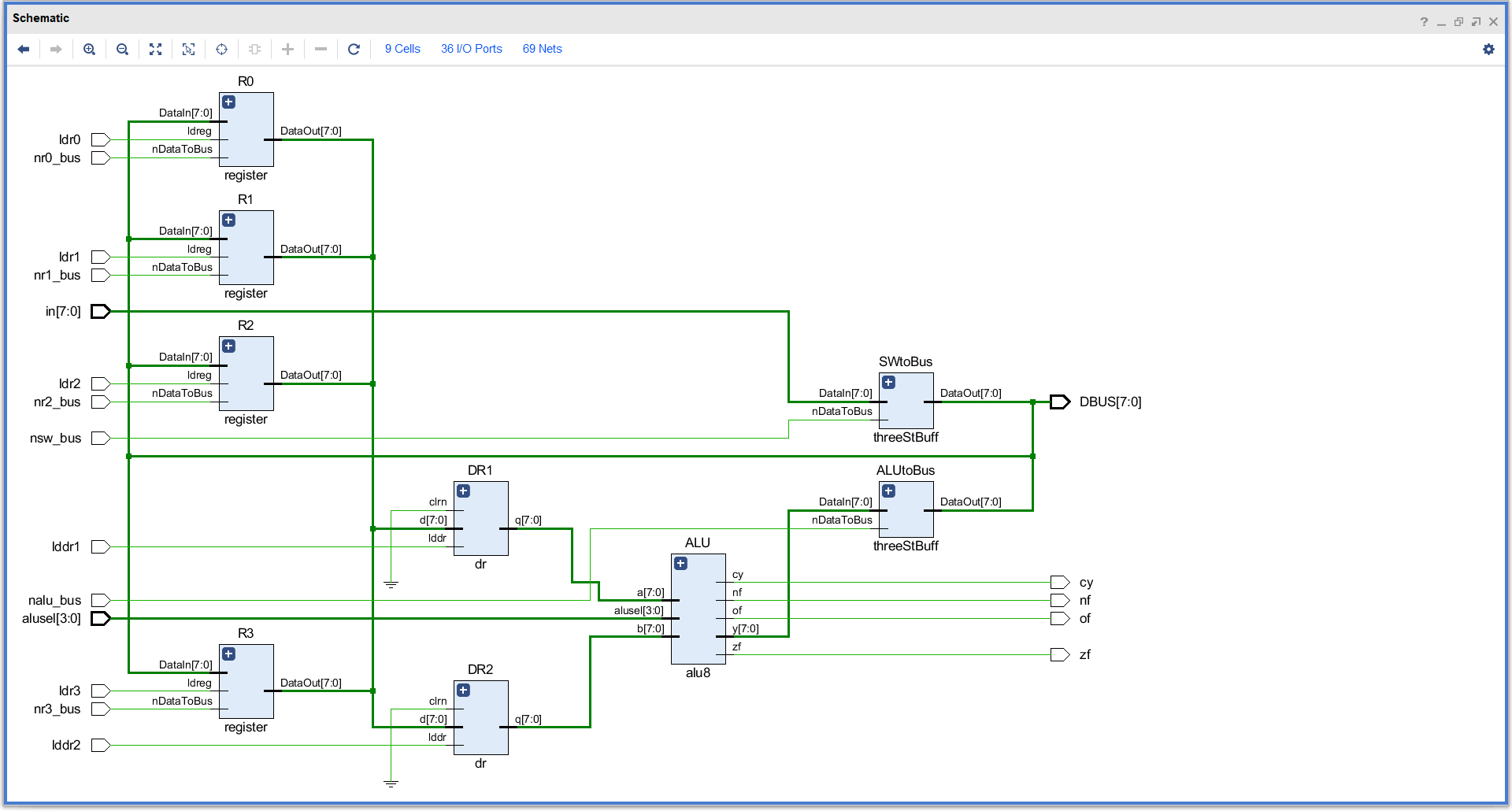

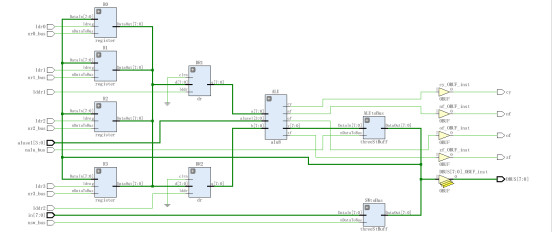

(3)根据实验指导书电路原理图要求,参考下图所示电路,设计本次实验的顶层模块。

(4)参考alu_dataPath_sim.v,编写测试文件,分别仿真测试各电路模块以及顶层模块。仿真测试通过后,上板验证。自行设计仿真和上板验证(可选)过程,并分析仿真和上板验证(可选)结果。

设计出的运算器数据通路实验顶层电路图如下(alu_dataPath.v):

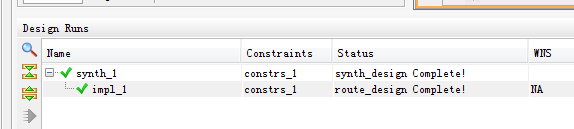

1. 工程文件

2. 程序文件

3. 程序编译

4. RTL图(顶层电路图)

部分代码展示:

`timescale 1ns / 1ps //顶层文件 module alu_dataPath( input ldr0, input nr0_bus, input ldr1, input nr1_bus, input ldr2, input nr2_bus, input ldr3, input nr3_bus, input [7:0] in, input nsw_bus, input lddr1, input lddr2, input nalu_bus, input [3:0] alusel, output cy, output zf, output of, output nf, output [7:0] DBUS ); wire [7:0] data_in; wire [7:0] data_out; wire [7:0] q_a; wire [7:0] q_b; wire [7:0] ALU_y; //寄存器模块 register R0( .DataIn (data_in), .ldreg (ldr0), .nDataToBus (nr0_bus), .DataOut (data_out) ); //寄存器模块 register R1( .DataIn (data_in), .ldreg (ldr1), .nDataToBus (nr1_bus), .DataOut (data_out) ); //寄存器模块 register R2( .DataIn (data_in), .ldreg (ldr2), .nDataToBus (nr2_bus), .DataOut (data_out) ); //寄存器模块 register R3( .DataIn (data_in), .ldreg (ldr3), .nDataToBus (nr3_bus), .DataOut (data_out) ); dr DR1( .clrn (1'b0), .d (data_out), .lddr (lddr1), .q (q_a) ); dr DR2( .clrn (1'b0), .d (data_out), .lddr (lddr2), .q (q_b) ); alu8 ALU( .a (q_a), .alusel(alusel), .b (q_b), .cy (cy), .nf (nf), .of (of), .y (ALU_y), .zf (zf) ); threeStBuff SWtoBus( .nDataToBus(nsw_bus), .DataIn (in), .DataOut (data_in) ); threeStBuff ALUtoBus( .nDataToBus(nalu_bus), .DataIn (ALU_y), .DataOut (data_in) ); assign DBUS=data_in; endmodule

源代码

扫描文章末尾的公众号二维码

815

815

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?