名称:基于FPGA的DDS产生正弦波设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

DDS产生正弦波

使用ROM设计DDS信号发生器,产生正弦波

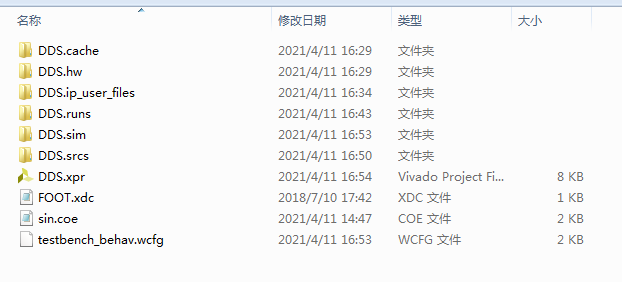

1. 工程文件

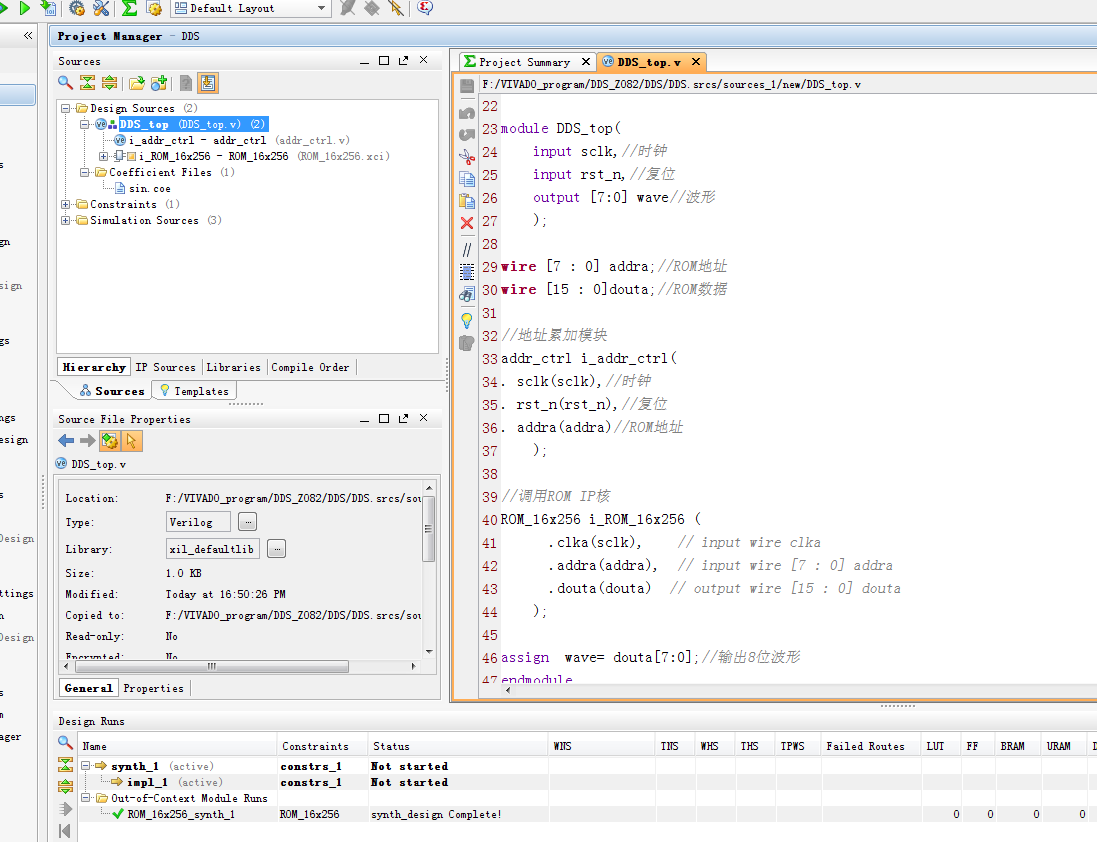

2. 程序文件

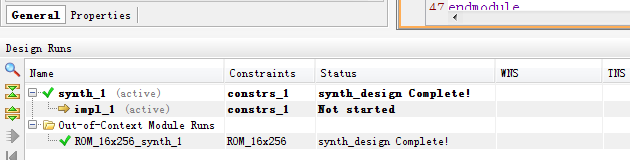

3. 程序编译

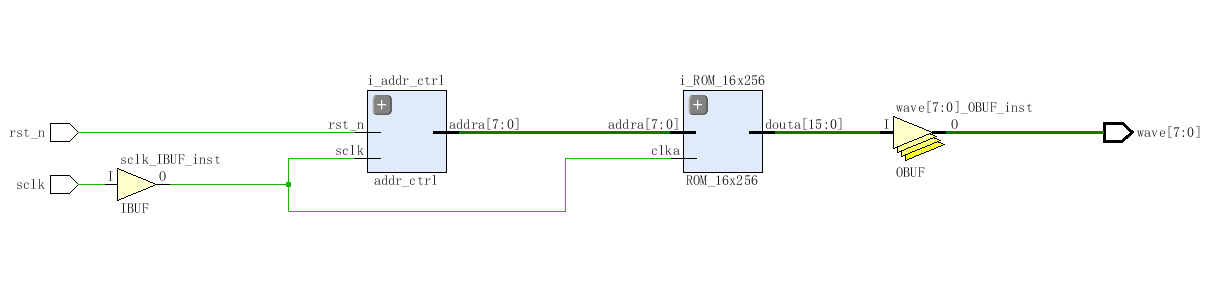

4. RTL图

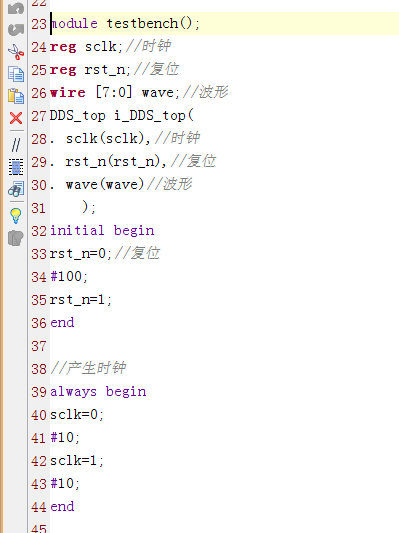

5. Testbench

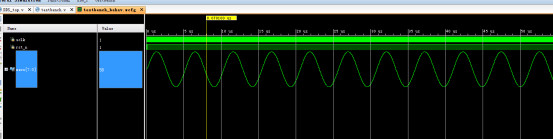

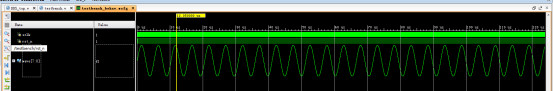

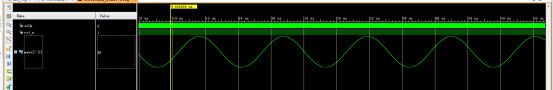

6. 仿真图

部分代码展示:

`timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 2021/04/11 16:31:34 // Design Name: // Module Name: DDS_top // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module DDS_top( input sclk,//时钟 input rst_n,//复位 output [7:0] wave//波形 ); wire [7 : 0] addra;//ROM地址 wire [15 : 0]douta;//ROM数据 //地址累加模块 addr_ctrl i_addr_ctrl( . sclk(sclk),//时钟 . rst_n(rst_n),//复位 . addra(addra)//ROM地址 ); //调用ROM IP核 ROM_16x256 i_ROM_16x256 ( .clka(sclk), // input wire clka .addra(addra), // input wire [7 : 0] addra .douta(douta) // output wire [15 : 0] douta ); assign wave= douta[7:0];//输出8位波形 endmodule

源代码

扫描文章末尾的公众号二维码

400

400

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?