名称:加法器实现60进制加减计数器设计VHDL代码ISE仿真(文末获取)

软件:ISE

语言:VHDL

代码功能:

加法器实现60进制加减计数器

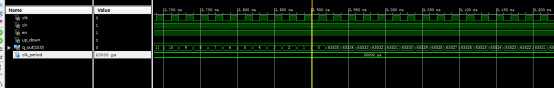

1、调用加法器模块实现加法和减法计数

1、计数范围0~59

2、具有异步清零、同步使能功能

3、可以控制递增计数和递减计数

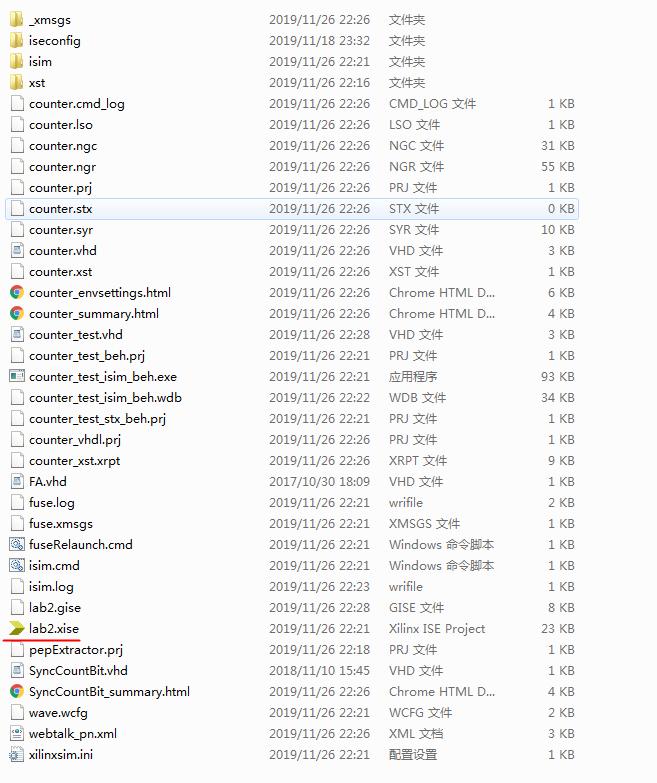

1. 工程文件

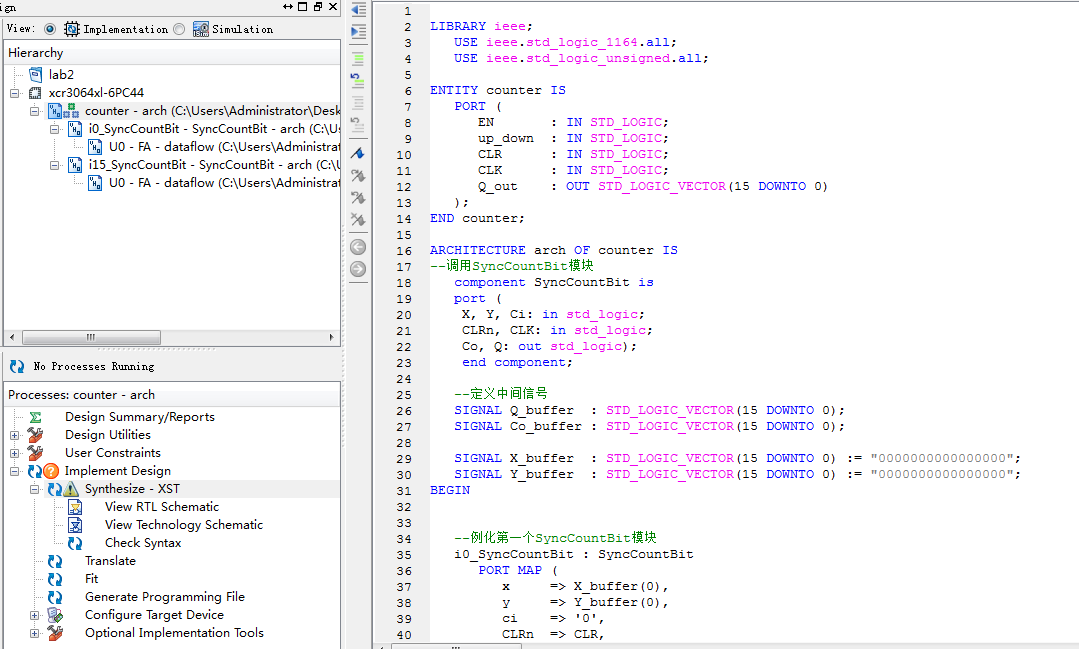

2. 程序文件

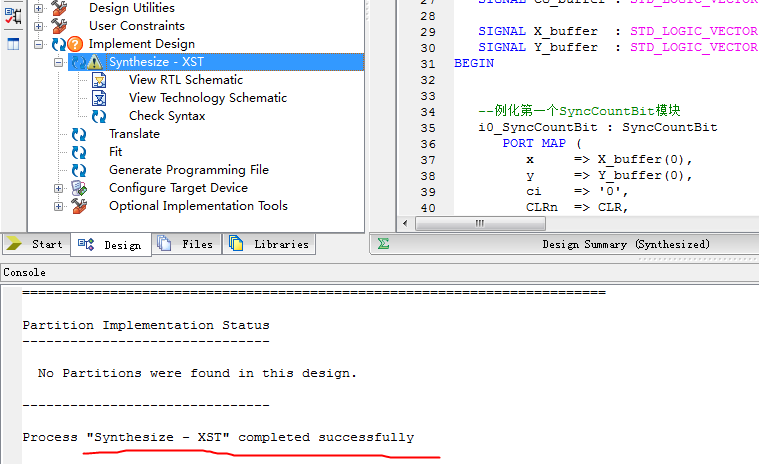

3. 程序编译

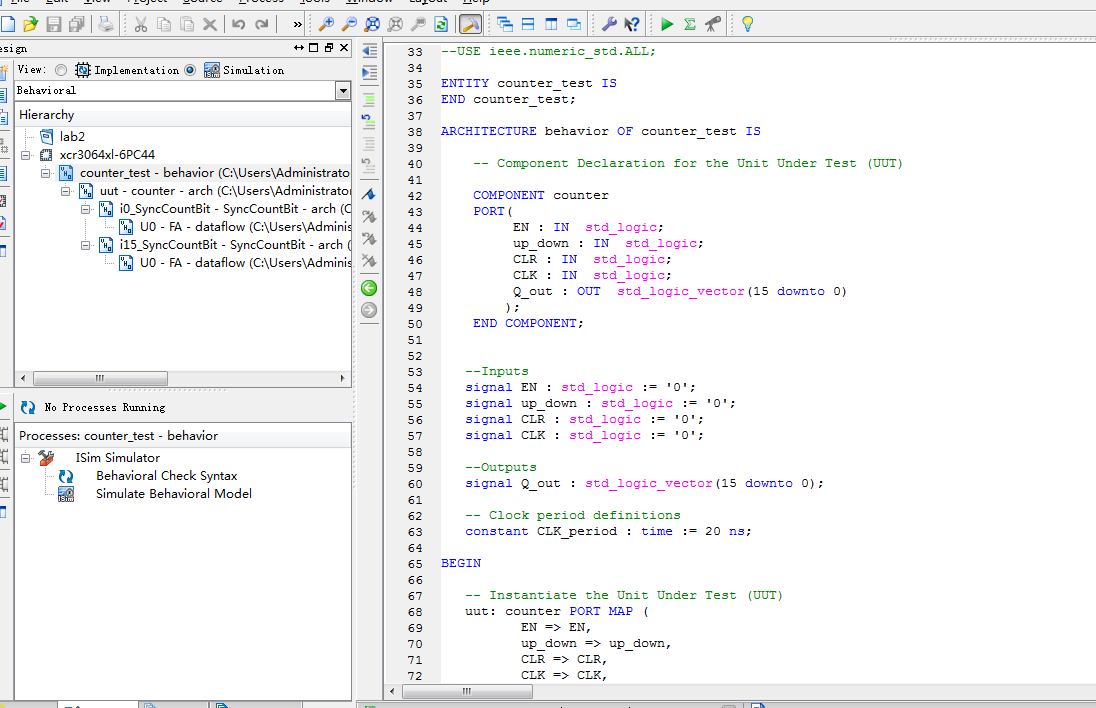

4. Testbench

5. 仿真图

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; ENTITY counter IS PORT ( EN : IN STD_LOGIC; up_down : IN STD_LOGIC; CLR : IN STD_LOGIC; CLK : IN STD_LOGIC; Q_out : OUT STD_LOGIC_VECTOR(15 DOWNTO 0) ); END counter; ARCHITECTURE arch OF counter IS --调用SyncCountBit模块 component SyncCountBit is port ( X, Y, Ci: in std_logic; CLRn, CLK: in std_logic; Co, Q: out std_logic); end component; --定义中间信号 SIGNAL Q_buffer : STD_LOGIC_VECTOR(15 DOWNTO 0); SIGNAL Co_buffer : STD_LOGIC_VECTOR(15 DOWNTO 0); SIGNAL X_buffer : STD_LOGIC_VECTOR(15 DOWNTO 0) := "0000000000000000"; SIGNAL Y_buffer : STD_LOGIC_VECTOR(15 DOWNTO 0) := "0000000000000000"; BEGIN --例化第一个SyncCountBit模块 i0_SyncCountBit : SyncCountBit PORT MAP ( x => X_buffer(0), y => Y_buffer(0), ci => '0', CLRn => CLR, CLK => CLK, co => Co_buffer(0), q => Q_buffer(0) ); --使用FOR 循环调用15个SyncCountBit模块;一共调用了16个SyncCountBit模块组合成16位全加器 lihua : FOR i IN 15 DOWNTO 1 GENERATE i15_SyncCountBit : SyncCountBit PORT MAP ( x => X_buffer(i), y => Y_buffer(i), ci => Co_buffer(i - 1), CLRn => CLR, CLK => CLK, co => Co_buffer(i), q => Q_buffer(i) ); END GENERATE;

源代码

点击下方的公众号卡片获取

1389

1389

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?