名称:基于FPGA的4位通用十进制计数器VHDL代码ISE仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

要求实现一个4位通用十进制计数器 (counter),counter的输入信号有:RST(Asynchronous Reset Input,表示异步复位,当RST为低电平时,此时不需要考虑时钟信号的状态,输出直接全0),时钟信号CLK,CLK上升沿触发,LD(Synchronous Parallel Load ,当为高电平时控制同步输入数据),D3~D0(Parallel Data Inputs ,同步输入的数值),U/D(Count direction,用于控制计数器是向上计数还是向下计数,高电平表示上计数,低电平表示下计数)输出信号为Q3~Q0(Data Outputs ,表示最终输出的计数值) 。

设计思路

首先根据框图的输入输出端口的要求,可以要求定义好代码的entity,即输入输出端口,输入信号有CLK、RST、U_D、D(3 DOWNTO 0),LD,输出端口为Q(3 DOWNTO 0)。然后根据真值表可知,RST需要实现异步清零功能,即只要RST为低电平,此时不需要考虑其他任何输入的状态,输出均为0,故RST信号的优先级最高,故使用IF语句,并将RST是否为0作为最先的判断条件,然后由于LD、U_D信号均为同步触发信号,故需要在时钟的边沿才有效,因此有第二个if条件判断CLK信号的上升沿,当满足上升沿条件时,再判断LD和U_D;根据真值表可知,当LD高电平时,此时无论U_D是什么状态,均为Synchronous Parallel Load

功能,故LD的优先级高于U_D,因此需要先判断LD是否为高电平,若为高,则将输入D(3 DOWNTO 0)赋值给Q(3 DOWNTO 0),此处定义一个中间变量cnt(3 DOWNTO 0),作为Q信号的缓存器,因为Q信号为端口输出信号,不能在进程中作为赋值语句的右侧。最后判断U_D信号的电平,当为高电平时,将cnt(3 DOWNTO 0)信号加1,若加到9,再返回0。当U_D为低电平时,将cnt(3 DOWNTO 0)信号减1,若减到0,再返回9。最后将cnt(3 DOWNTO 0)信号赋值给Q(3 DOWNTO 0)即完成设计的全部功能。

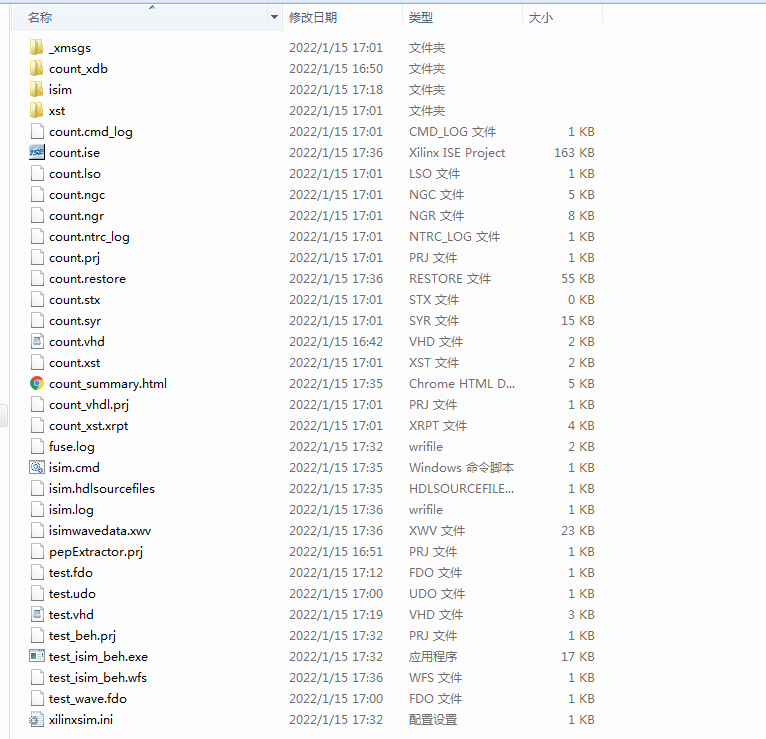

1. 工程文件

2. 程序文件

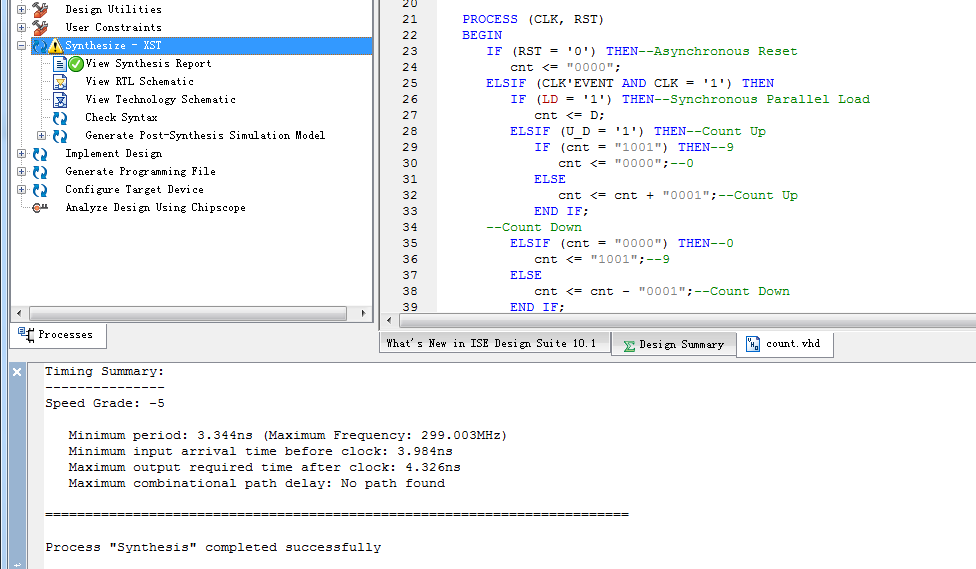

3. 程序编译

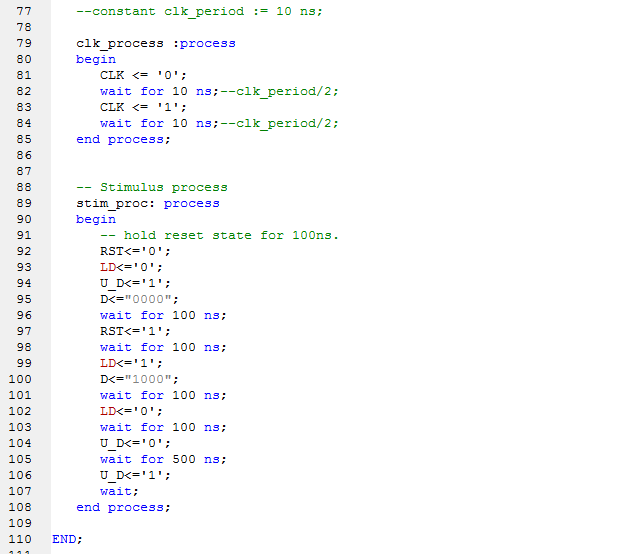

4. Testbench

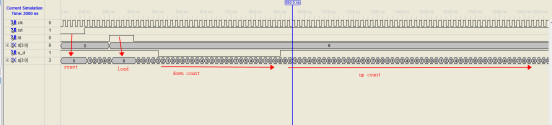

5. 仿真图

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --a 4-bit universal decimal counter ENTITY count IS PORT ( CLK : IN STD_LOGIC;--clock RST : IN STD_LOGIC;--Asynchronous Reset Input U_D : IN STD_LOGIC;--Count direction (up/down) D : IN STD_LOGIC_VECTOR(3 DOWNTO 0);-- Parallel Data Inputs LD : IN STD_LOGIC;--Synchronous Parallel Load Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)--Data Outputs ); END count; ARCHITECTURE behave OF count IS SIGNAL cnt : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000"; BEGIN PROCESS (CLK, RST) BEGIN IF (RST = '0') THEN--Asynchronous Reset cnt <= "0000"; ELSIF (CLK'EVENT AND CLK = '1') THEN IF (LD = '1') THEN--Synchronous Parallel Load cnt <= D; ELSIF (U_D = '1') THEN--Count Up IF (cnt = "1001") THEN--9 cnt <= "0000";--0 ELSE cnt <= cnt + "0001";--Count Up END IF;

源代码

扫描文章末尾的公众号二维码

415

415

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?