名称:简单基础组合逻辑设计VHDL代码ISE仿真(文末获取)

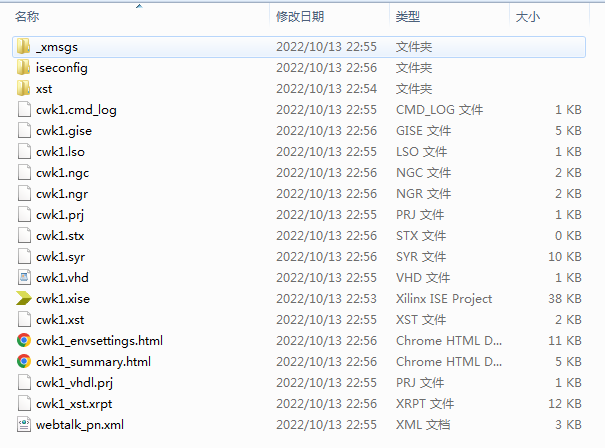

软件:ISE

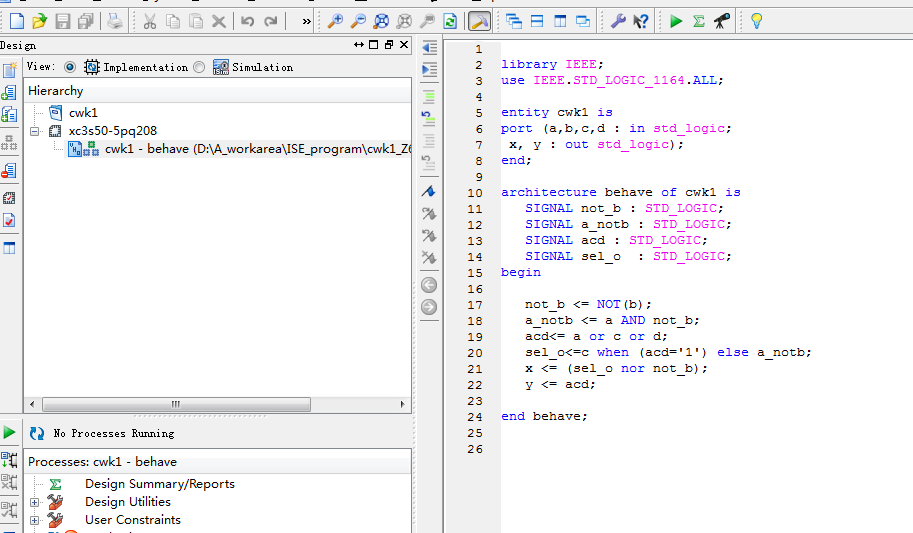

语言:VHDL

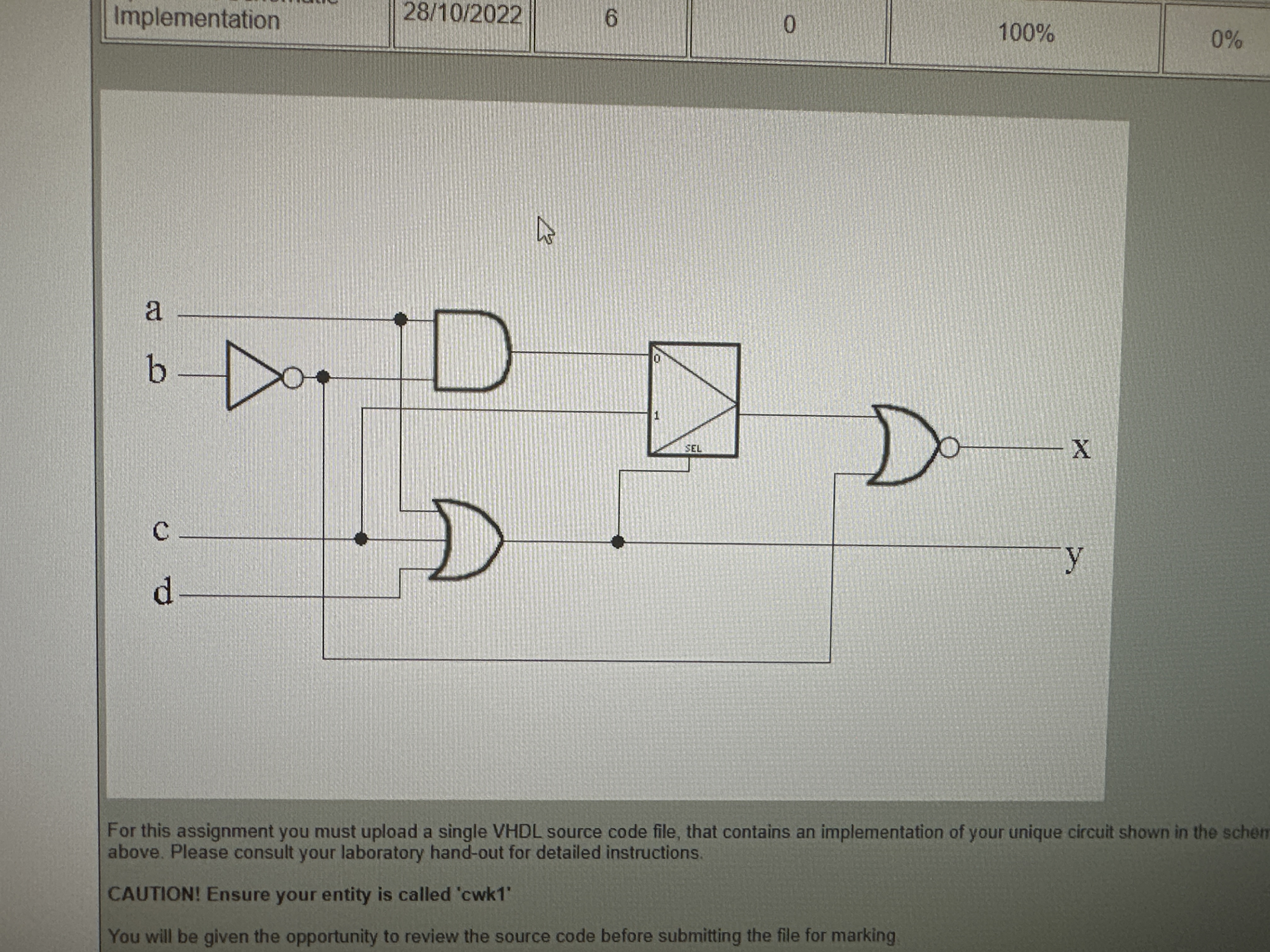

代码功能:简单基础组合逻辑

1. 工程文件

2. 程序文件

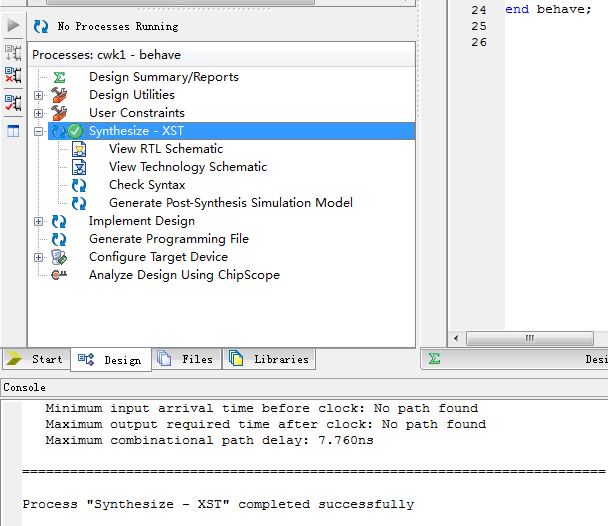

3. 程序编译

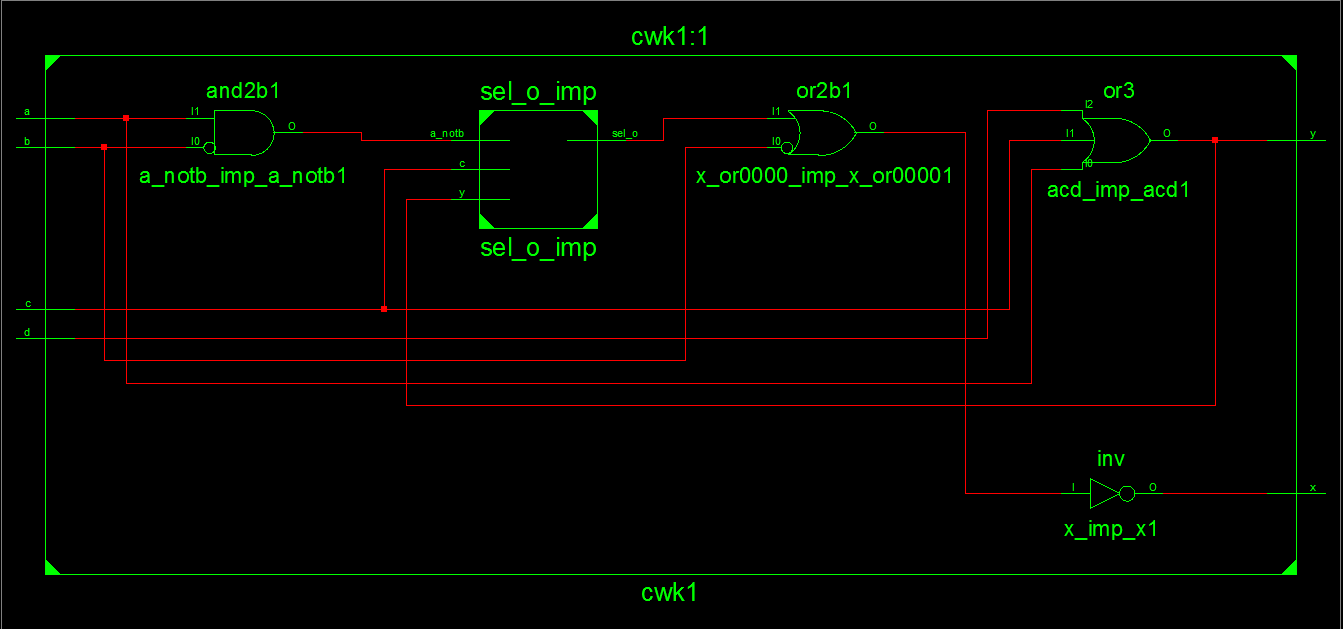

4. RTL图

真值表

| a | b | c | d | x | y |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 | 1 |

部分代码展示:

-------------------------------------------------------------------------------- -- Company: -- Engineer: -- -- Create Date: 23:01:16 10/13/2022 -- Design Name: -- Module Name: D:/A_workarea/ISE_program/cwk1_Z600/cwk1/test.vhd -- Project Name: cwk1 -- Target Device: -- Tool versions: -- Description: -- -- VHDL Test Bench Created by ISE for module: cwk1 -- -- Dependencies: -- -- Revision: -- Revision 0.01 - File Created -- Additional Comments: -- -- Notes: -- This testbench has been automatically generated using types std_logic and -- std_logic_vector for the ports of the unit under test. Xilinx recommends -- that these types always be used for the top-level I/O of a design in order -- to guarantee that the testbench will bind correctly to the post-implementation -- simulation model. -------------------------------------------------------------------------------- LIBRARY ieee; USE ieee.std_logic_1164.ALL; -- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values --USE ieee.numeric_std.ALL; ENTITY test IS END test; ARCHITECTURE behavior OF test IS -- Component Declaration for the Unit Under Test (UUT) COMPONENT cwk1 PORT( a : IN std_logic; b : IN std_logic; c : IN std_logic; d : IN std_logic; x : OUT std_logic; y : OUT std_logic ); END COMPONENT; --Inputs signal a : std_logic := '0'; signal b : std_logic := '0'; signal c : std_logic := '0'; signal d : std_logic := '0'; --Outputs signal x : std_logic; signal y : std_logic; BEGIN -- Instantiate the Unit Under Test (UUT) uut: cwk1 PORT MAP ( a => a, b => b, c => c, d => d, x => x, y => y );

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?