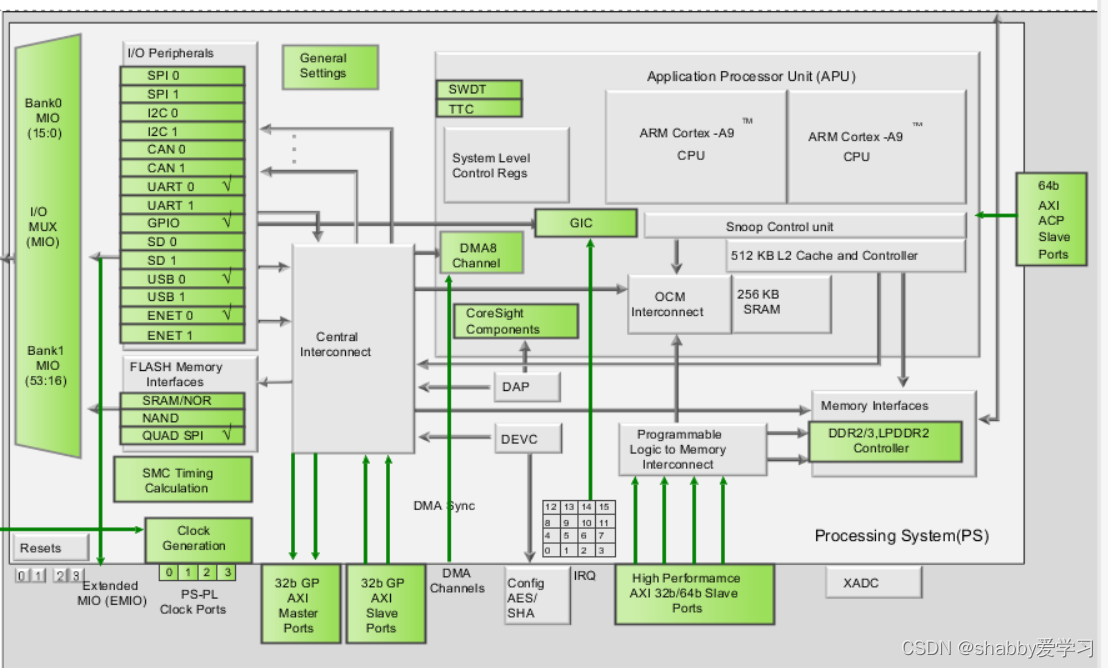

1、新建工程,配置ARM核

- 配置基本外设

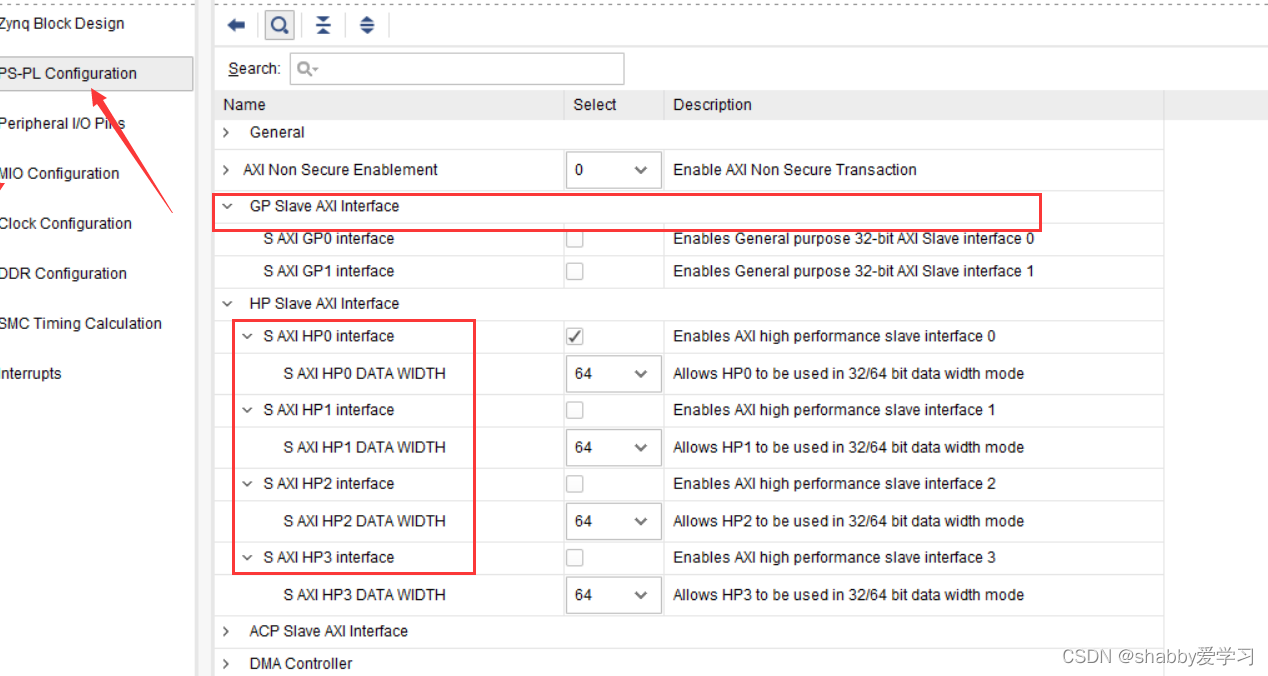

- 本实验采用HP接口,高速接口64位宽;关闭GP接口 位宽是32位

2.其他配置

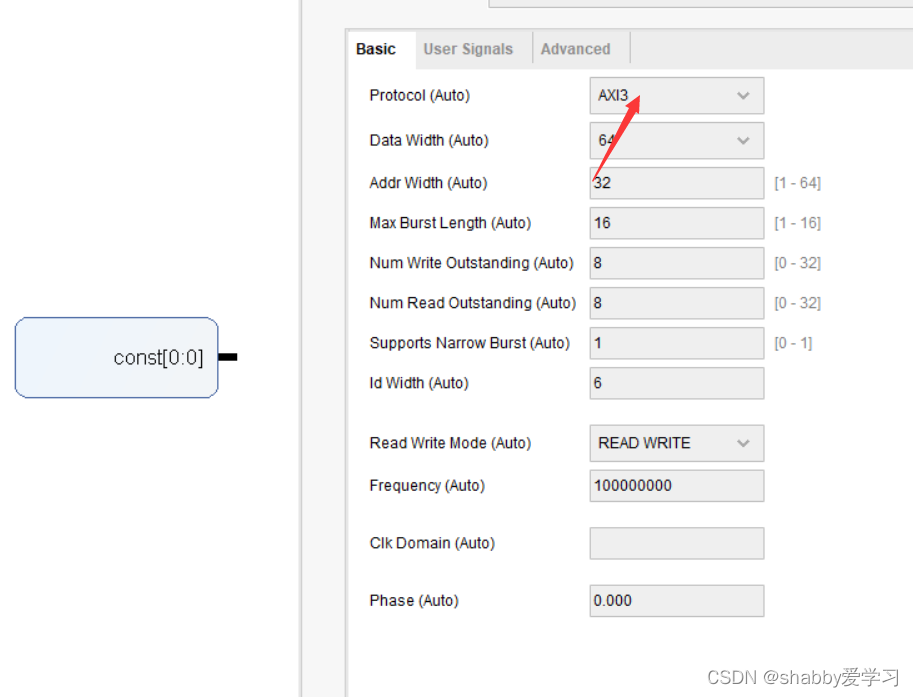

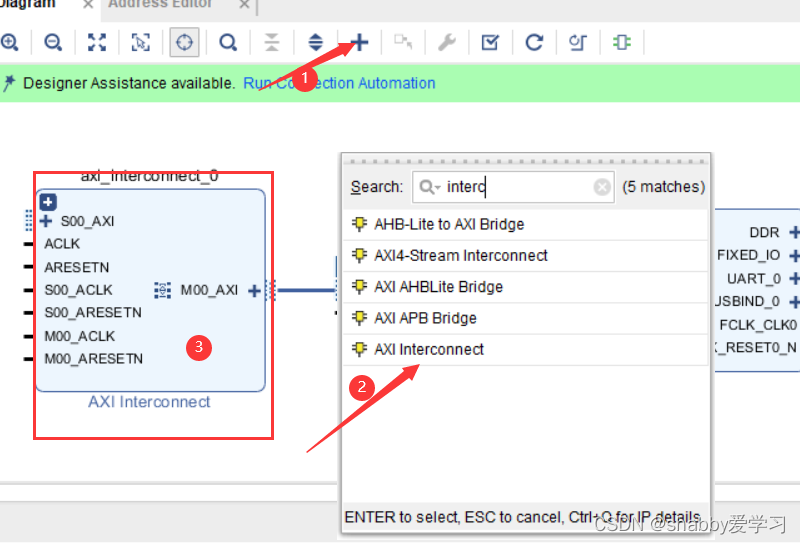

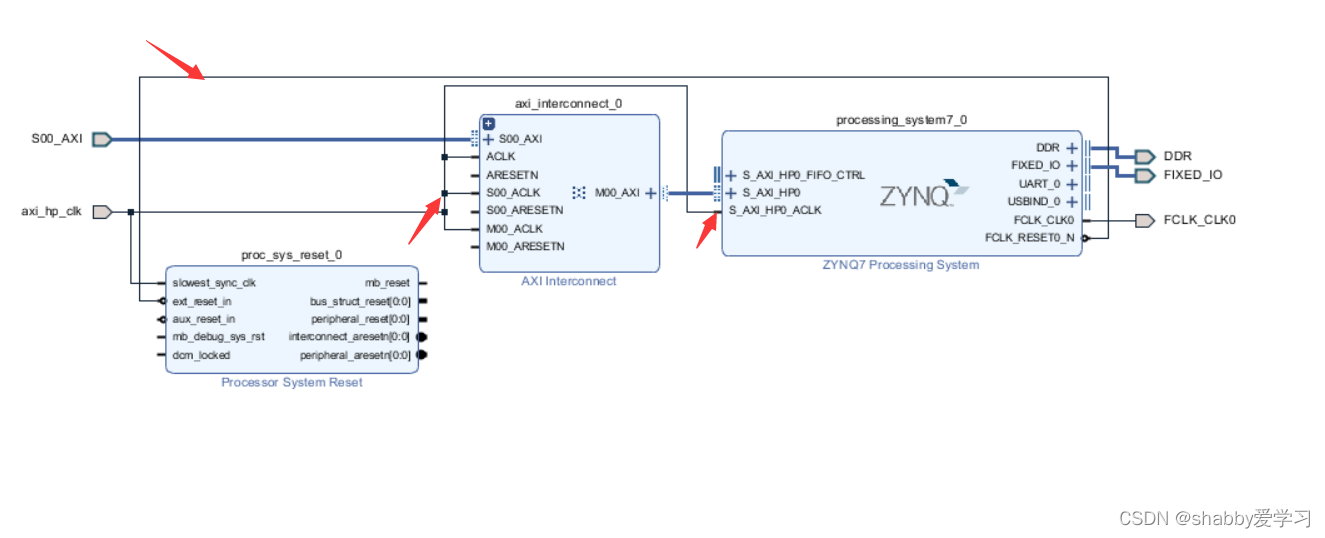

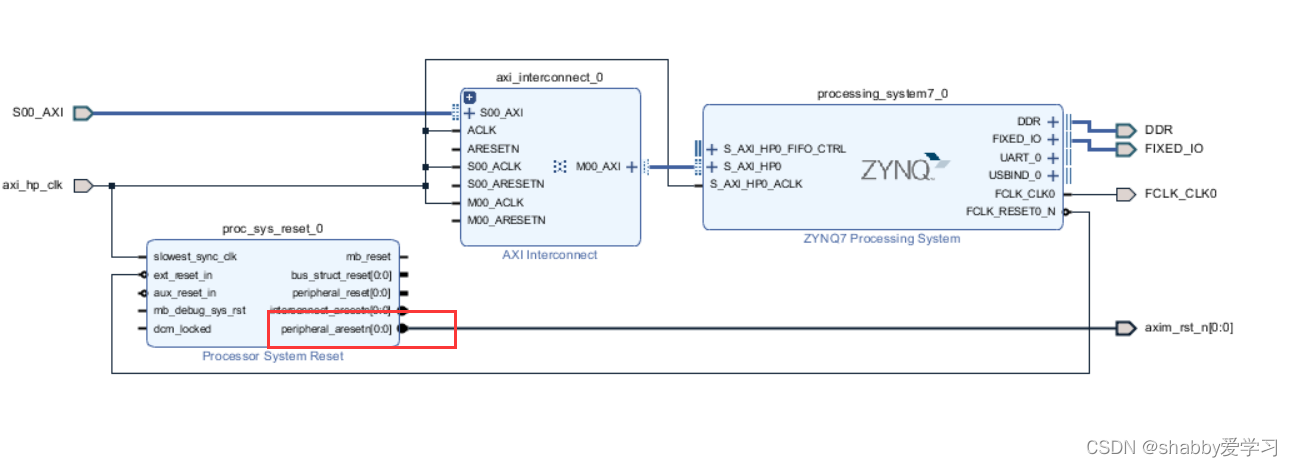

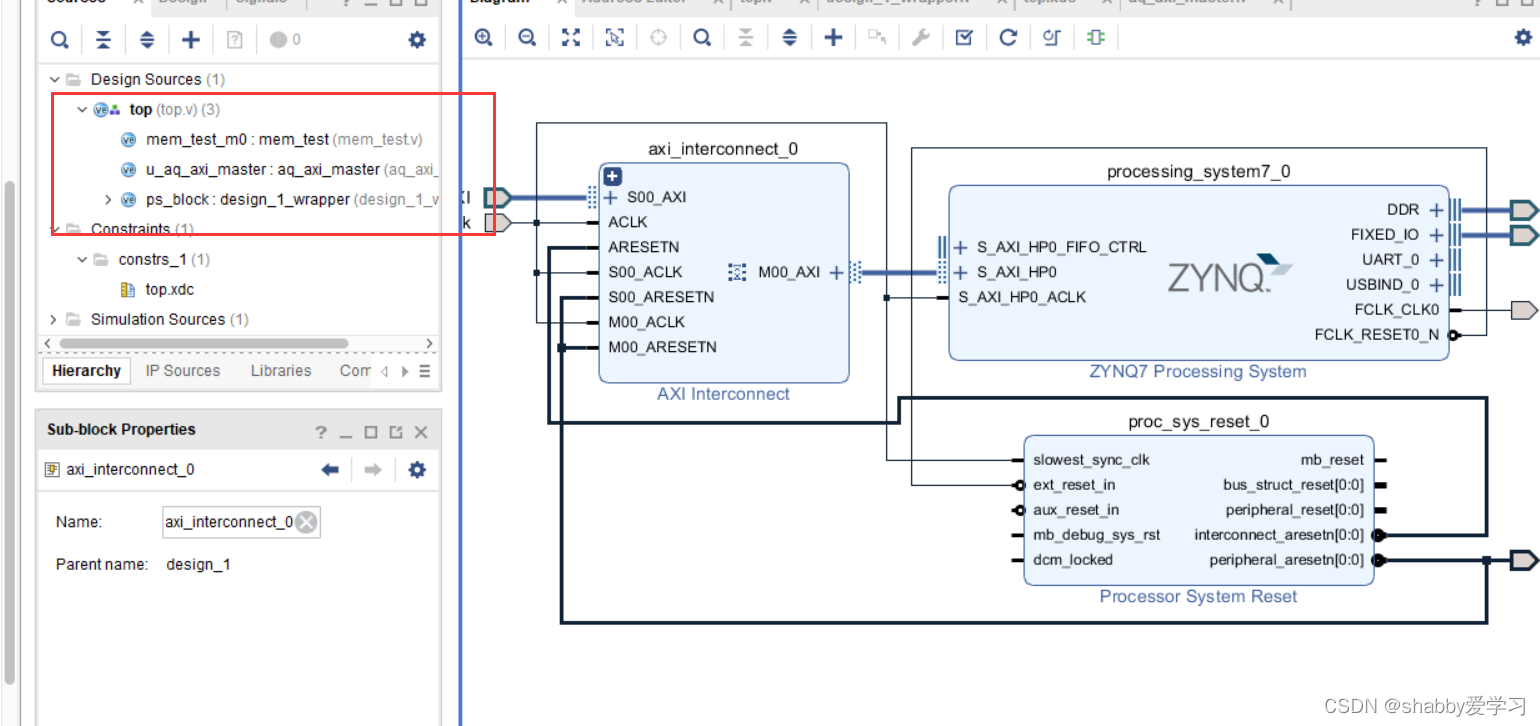

- PS和PL之间的交互是通过AXI总线协议,所以需要配置AXI总线。查看zynq核的接口总线协议是AXI3,需要转接成AXI4协议。添加一个AXI interconnect 转接口

需要配置他们的接口。

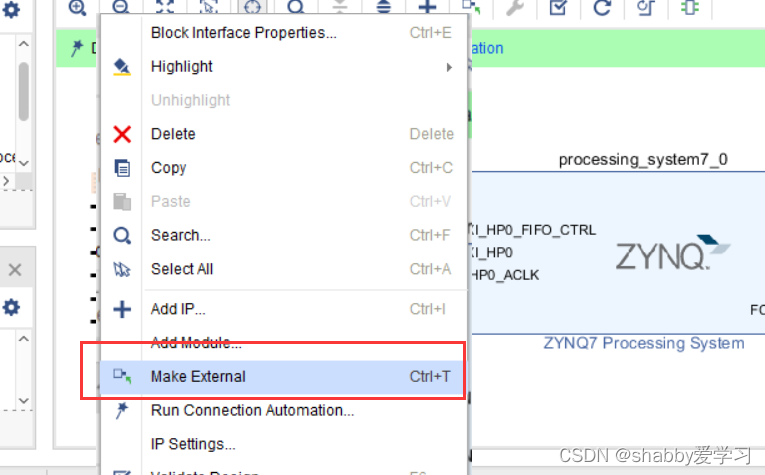

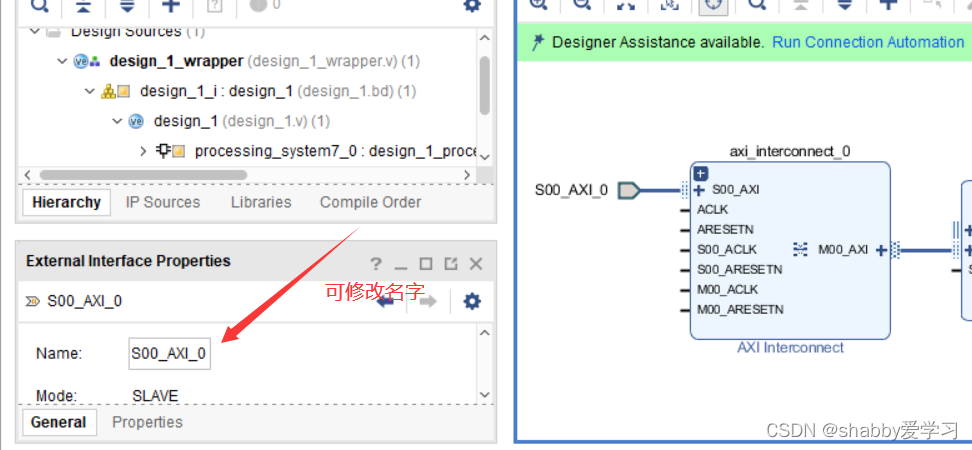

连接AXI4的master同slave接口,数据交互,导出AXI4的接口

添加一个复位模块,给逻辑提供复位。

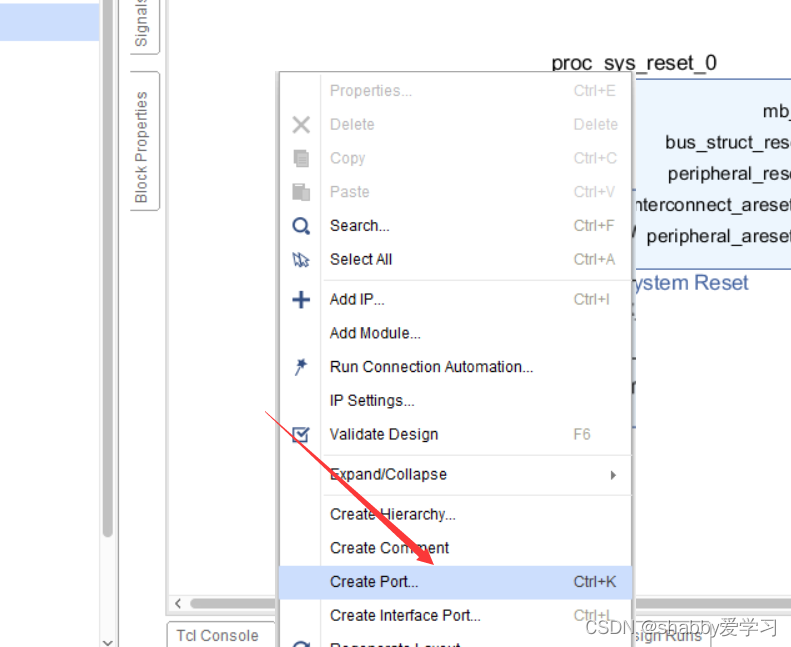

添加一个端口,给hp提供时钟。150Mhz

连接hp的所有时钟信号,复位模块的复位信号连接到zynq上。

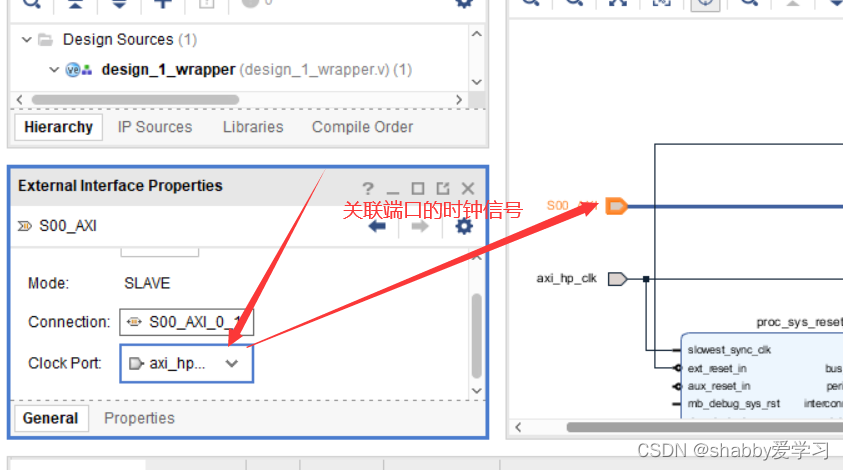

关联axi接口的时钟信号,并把axi总线配置成axi4的方式。

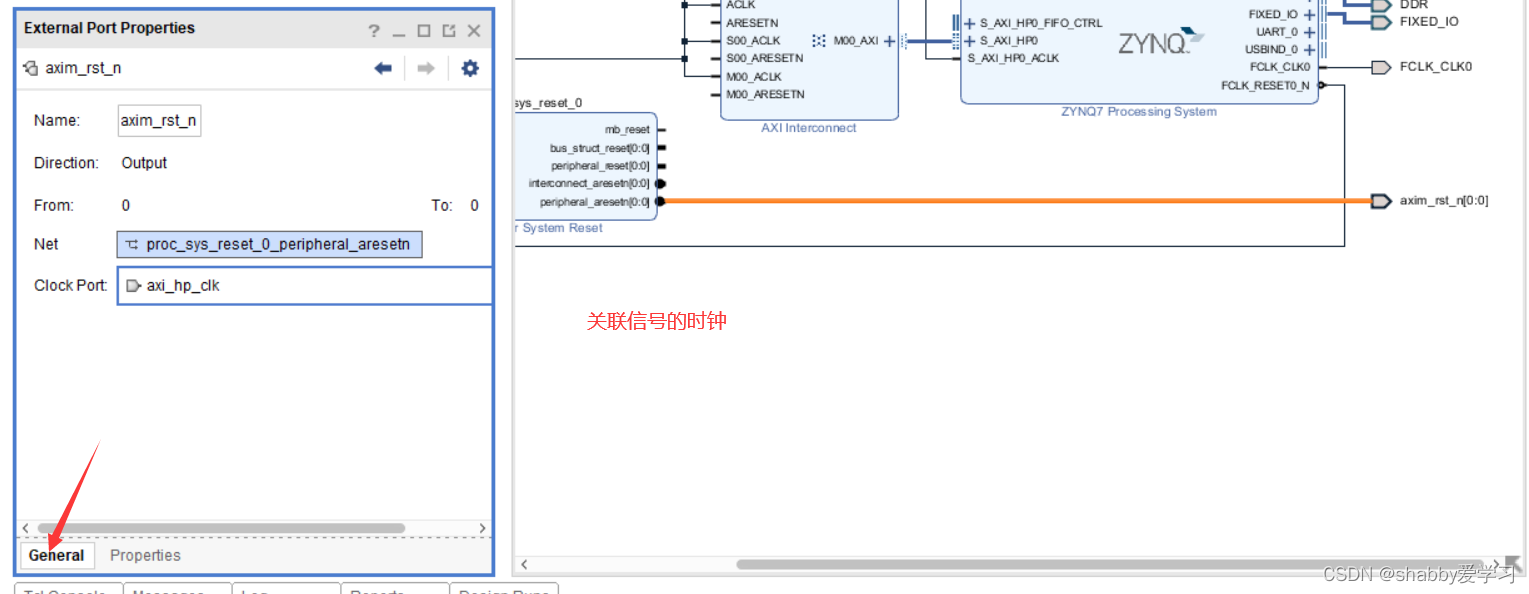

导出外部复位并修改名字。

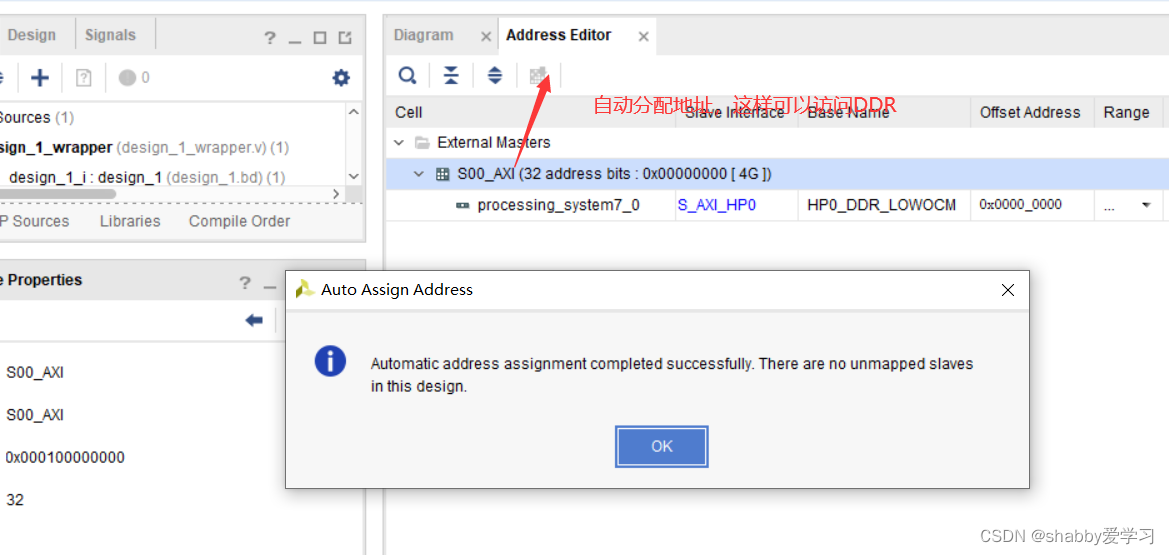

给DDR分配地址,这样就能访问DDR

例化相关文件,这是官方提供的例子。

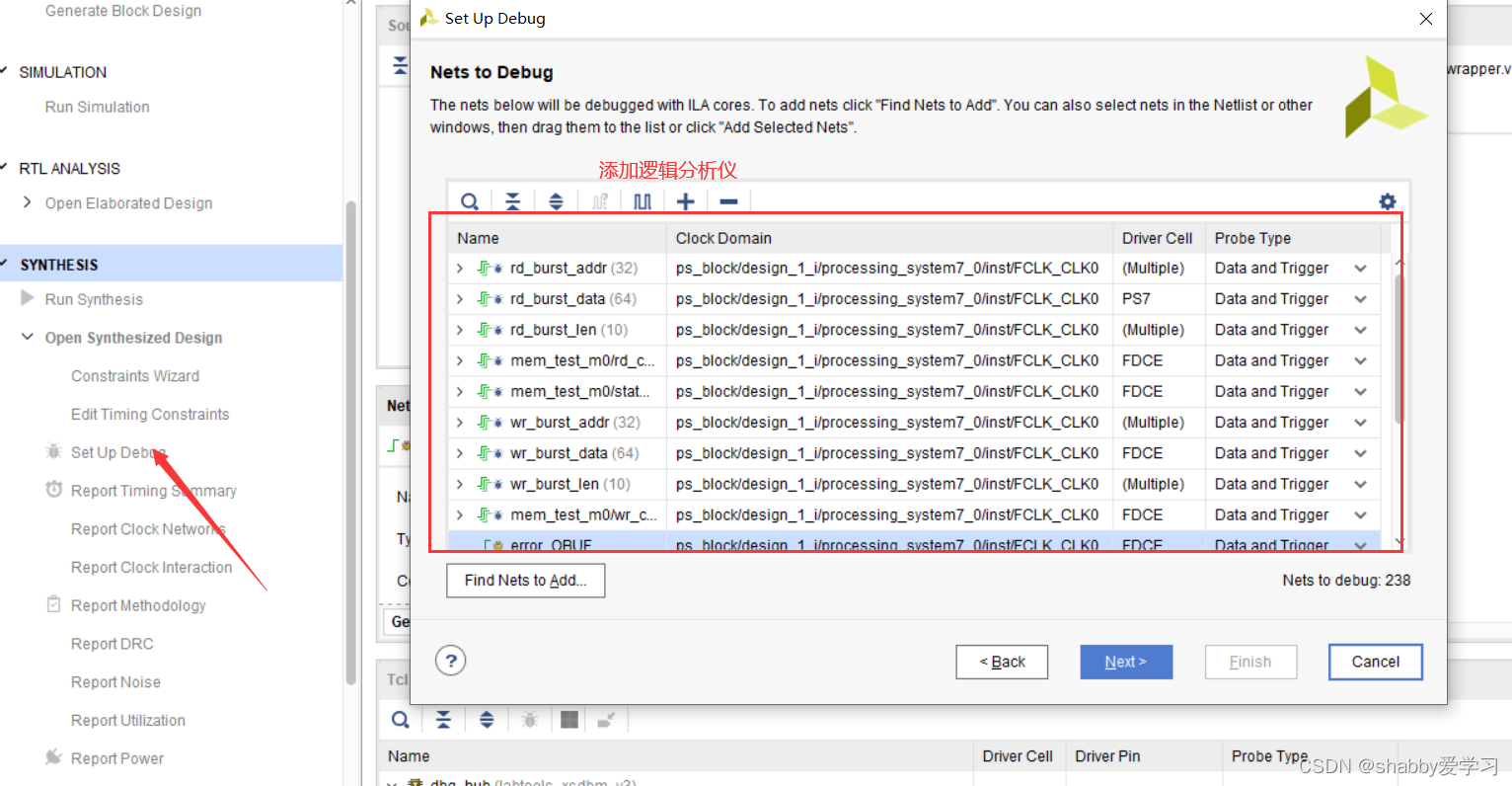

综合之后,set up debug。添加时钟域,最后生成bit流文件。需要花很长时间。

3、SDK操作

-

导出硬件信息,新建一个工程,helloword模板。

-

下载程序,编程fpga,因为使用了zynq核,所以要从这里下载程序。

-

在vivado里面看效果。

-

3375

3375

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?