目录

第一种方法(使用SignalTap II Logic Analyzer)

实验目的:

进一步熟悉QuartusⅡ及其LPM_ROM与FPGA硬件资源的使用方法。

实验预习:

定制LPM_ROM模块流程。

实验原理:

EDA是电子设计自动化,对象是数字电路设计,而正弦信号发生器的设计却是一个模拟电路设计,因此需要用到D/A转换器。

根据正弦信号发生器的波形,得知该实验的输入为时间,而输出为振幅。如果将正弦波的振幅放在存储单元为64的ROM中,根据ROM的功能得知,ROM中的数据与地址是一一对应关系,因此设计由时间和振幅的对应关系转换为时间和地址的对应关系。据此,要得到正弦信号,需要设计一个6位二进制计数器。下图为总体设计框图:

在许多实用情况下,必须使用宏功能模块才能使用一些Altera特定器件的硬件功能,例如各类片上存储器、DSP模块等等。这些可以以图形或硬件描述语言模块形式方便调用的宏功能块,使得基于EDA技术的电子设计的效率和可靠性有了很大的提高。

LPM是参数可设置模块库(Library of Parameterized Modules)的英语缩写。根据实际电路的设计需要,选择LPM库中的适当模块,并为其设定适当的参数,就能满足自己的设计需要,从而在自己的项目中十分方便的调用优秀的电子工程技术人员的硬件设计成果。

LPM功能模块内容丰富,每一模块的功能、参数含义、使用方法、硬件描述语言模块参数设置及调用方法都可以在QuartusⅡ中的help中查阅到,方法是选择helpàMegafunction/LPM命令。

定制LPM_ROM模块流程:

1、定制初始化数据文件,建立.mif格式文件

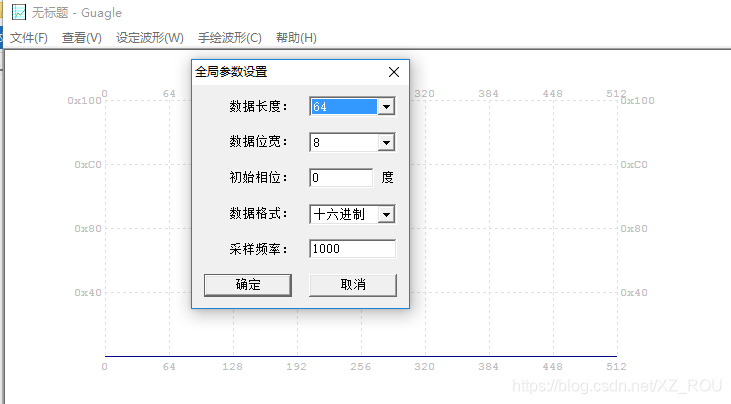

(1)打开Mif任意波编辑器Mif_Maker2010【软件已上传资源库】,选择“设定波形”-“全局参数”,修改数据长度为64,数据宽度为8,如图1所示。

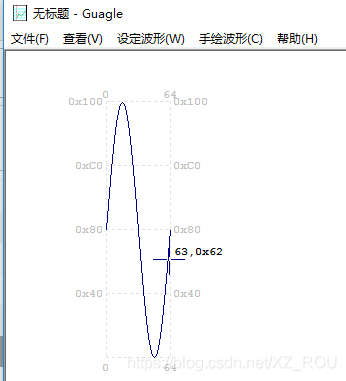

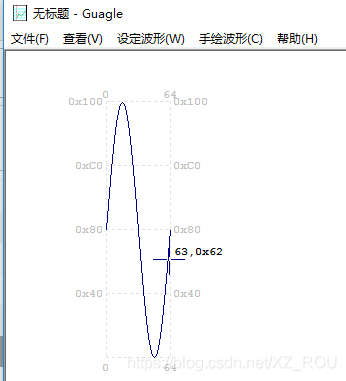

(2)选择“设定波形”-“正弦波”,如图2所示。

(3)在文件中选择保存,保存在D:/myfile/sinve文件夹【建议保存在即将使用的工程文件目录下】,注意sinve是工作库目录,如图3所示。

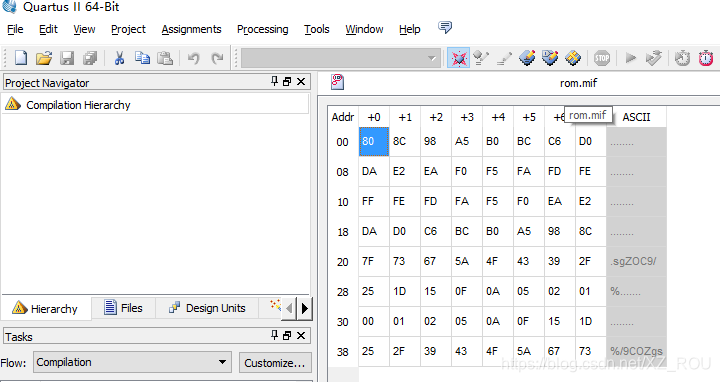

(4)在QuartusII软件中打开rom.mif文件,如图4所示。

2、定制LPM_ROM元件

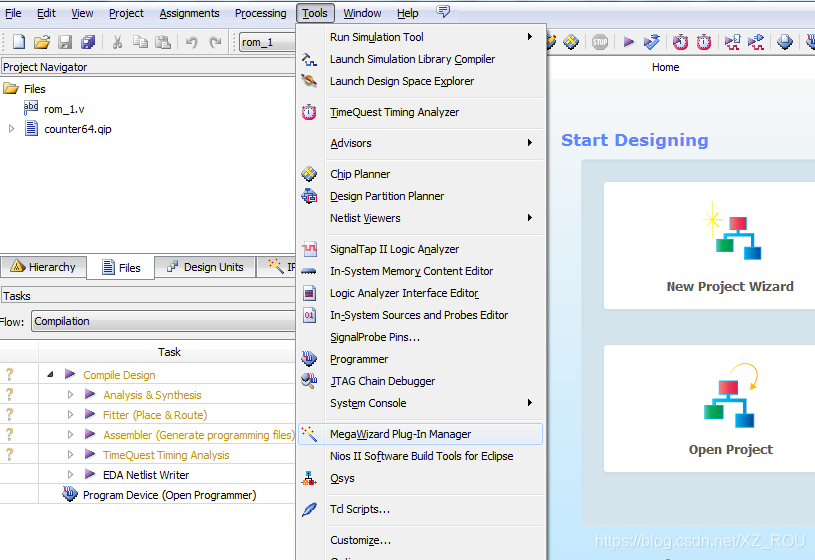

(1)打开Tools菜单,选择“MegaWizard Plug-In Manager”,如下图5所示。

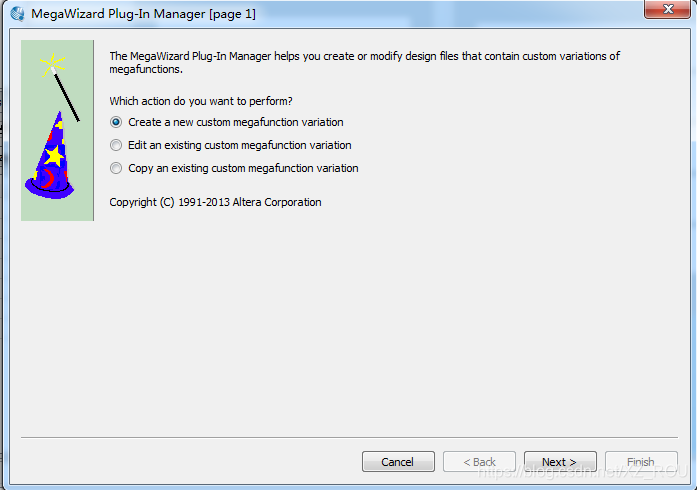

(2)点击打开MegaWizard Plug-In Manager初始对话框,选择创建新的宏功能模块,如图6所示。

(3)点击“Next”,选择选择宏功能块(

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?