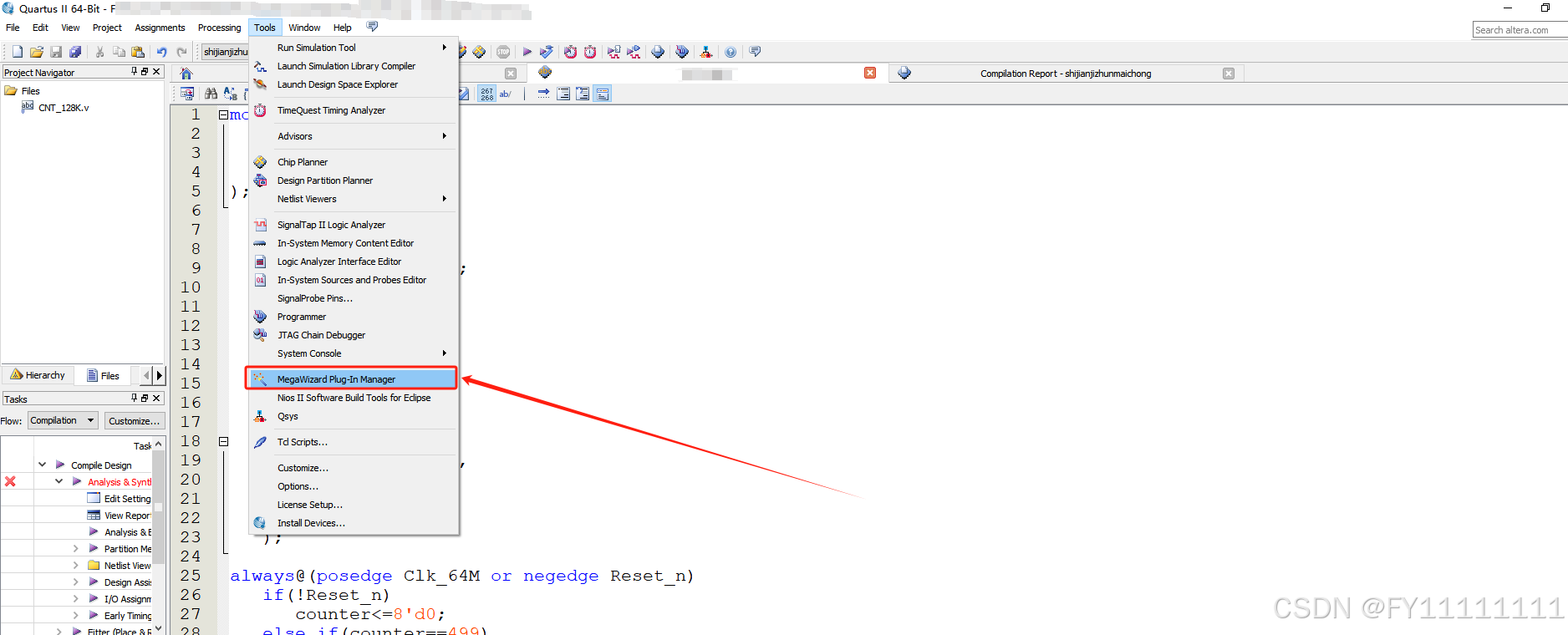

1、单击界面上方工具栏里的Tools→MegaWizard Plug-In Manager。

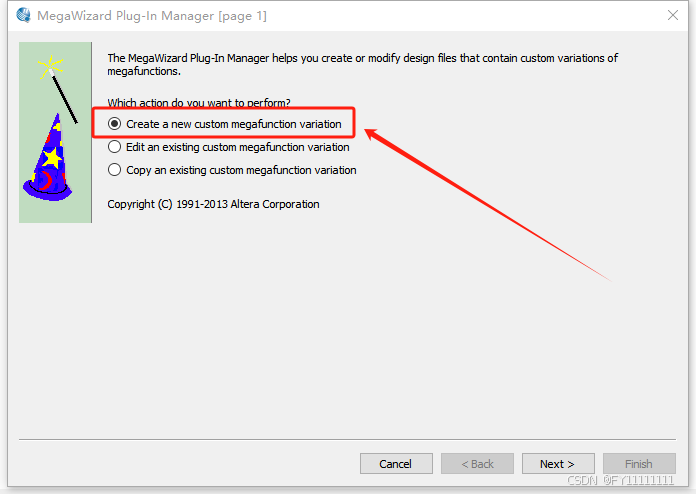

2、在弹出的对话框中选择Create a new custom megafunction variation,然后点击Next。

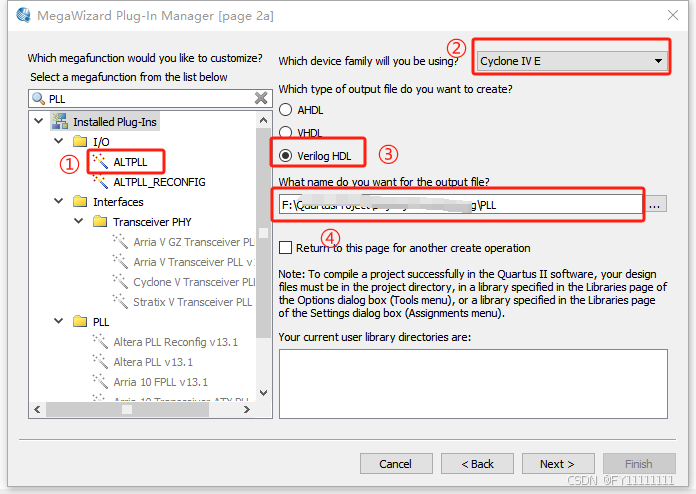

3、在这个界面,通过搜索框搜索PLL,选择ALTPLL(传统锁相环)。同时也要注意②③④这几个地方的配置,④是文件的存储位置,自主选择。然后点击Next。

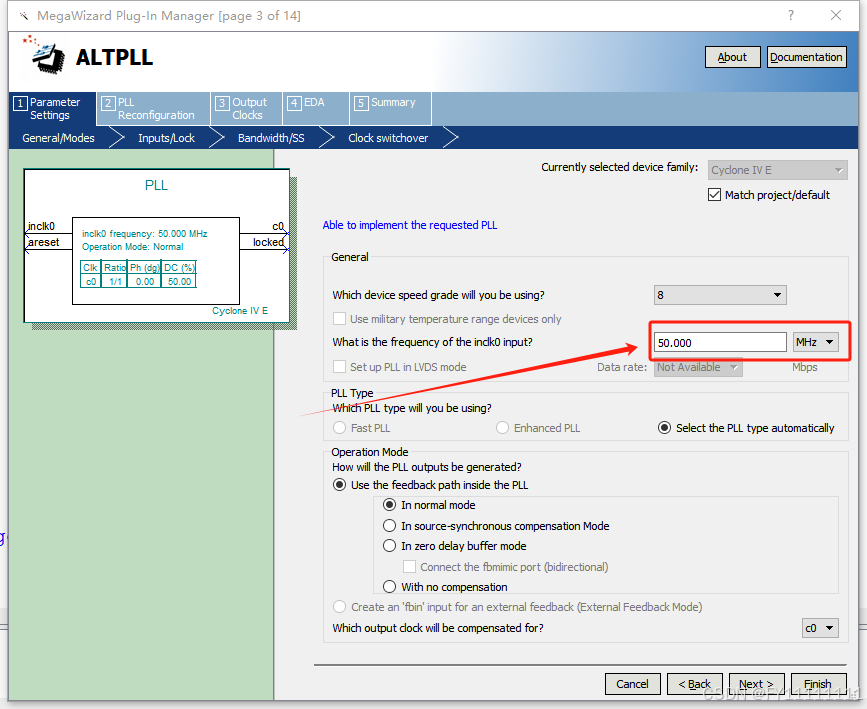

4、配置输入时钟,根据自己所使用的板子的系统时钟配置。如下图所示,其它选项保持默认。

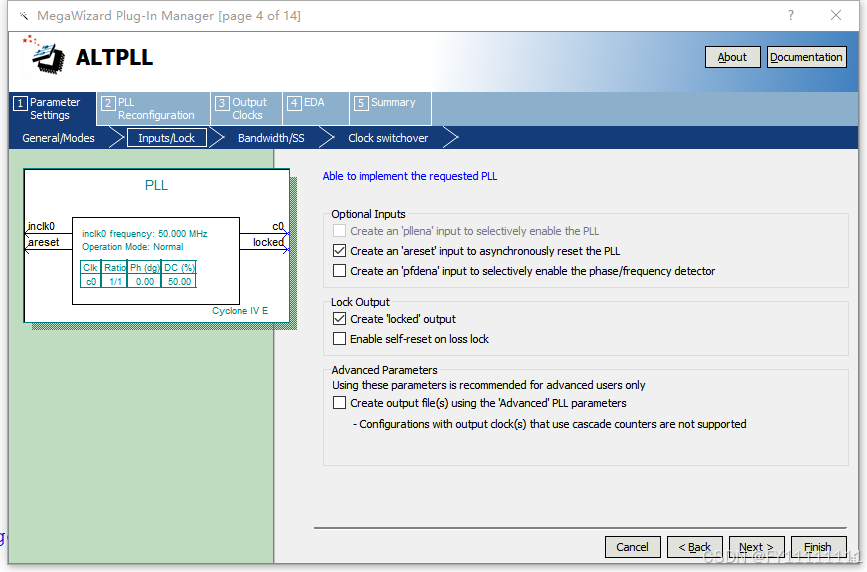

5、这一页的选项保持默认。

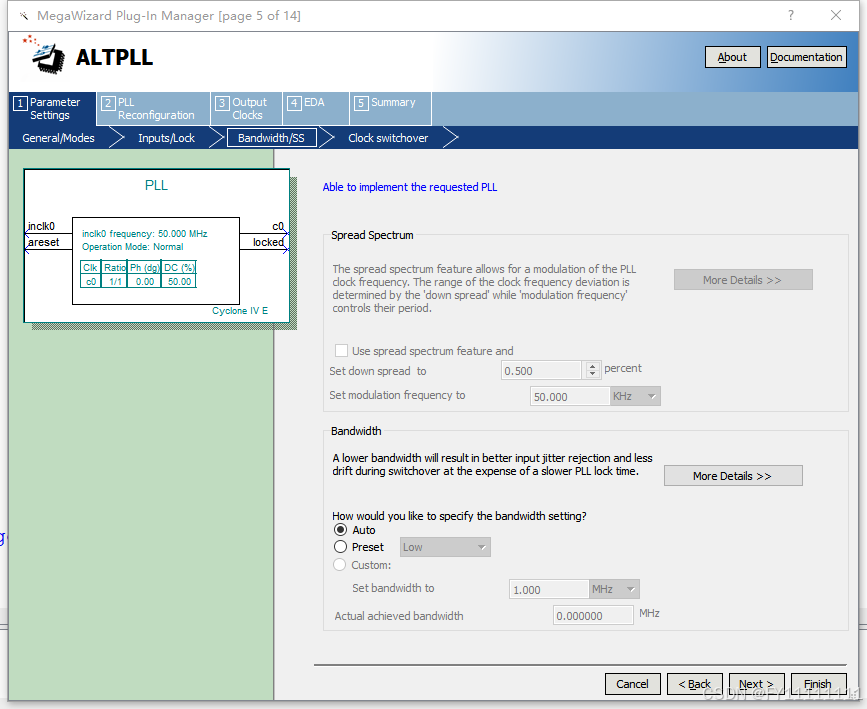

6、保持默认。

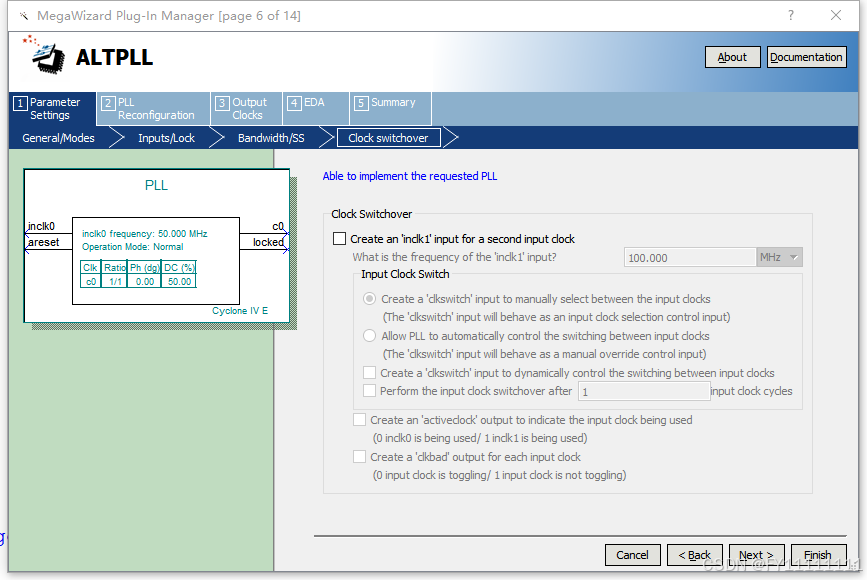

7、保持默认。

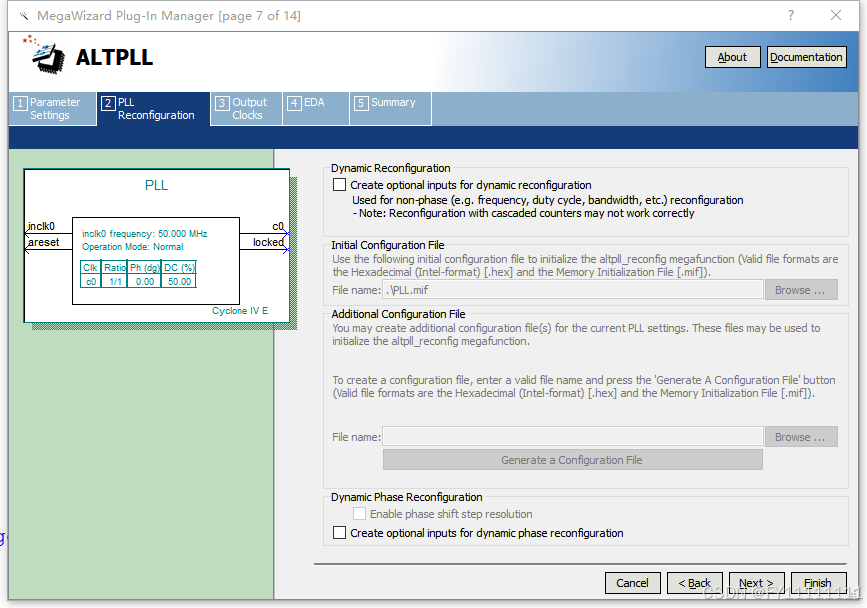

8、保持默认。

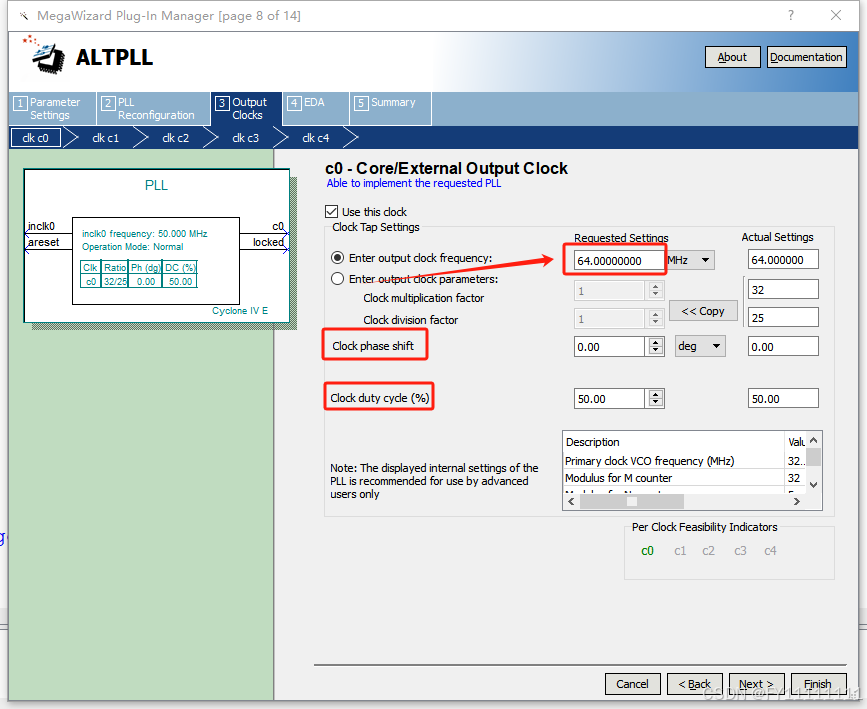

9、配置输出时钟,选择Enter output clock frequency这一选项,在后方直接输入所需输出的时钟就可以。如果选择Enter output clock parameters这一选项,就需要输入分频倍频的数据,得到最终需要输出的时钟频率。一般直接选择Enter output clock frequency这一选项就可以。

下方的Clock phase shift(相位偏移)和Clock duty cycle(占空比)都保持默认就可以。

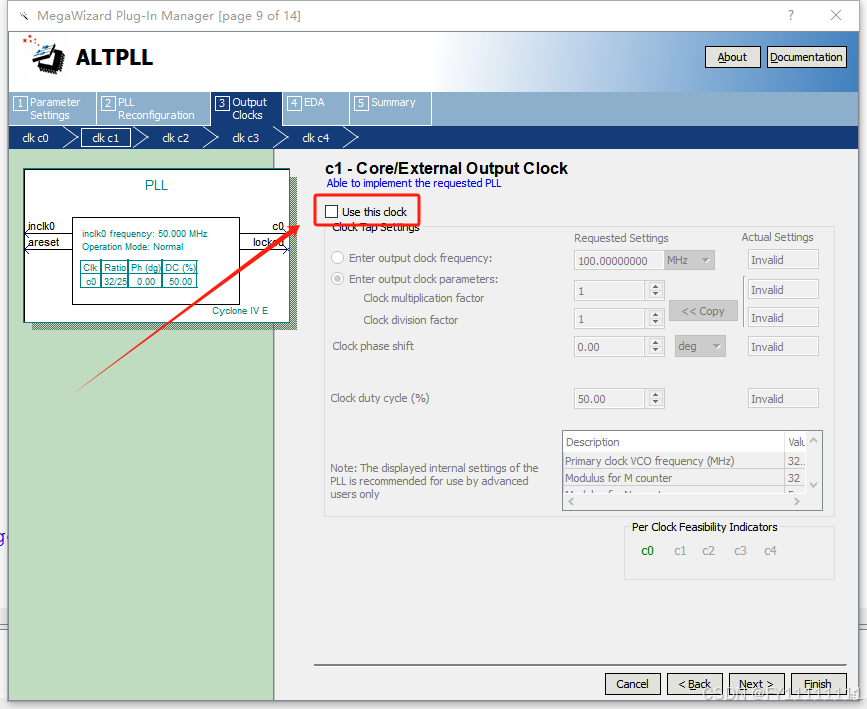

10、如果需要多个输出时钟,就勾选C1、C2、C3、C4界面选择Use this clock。

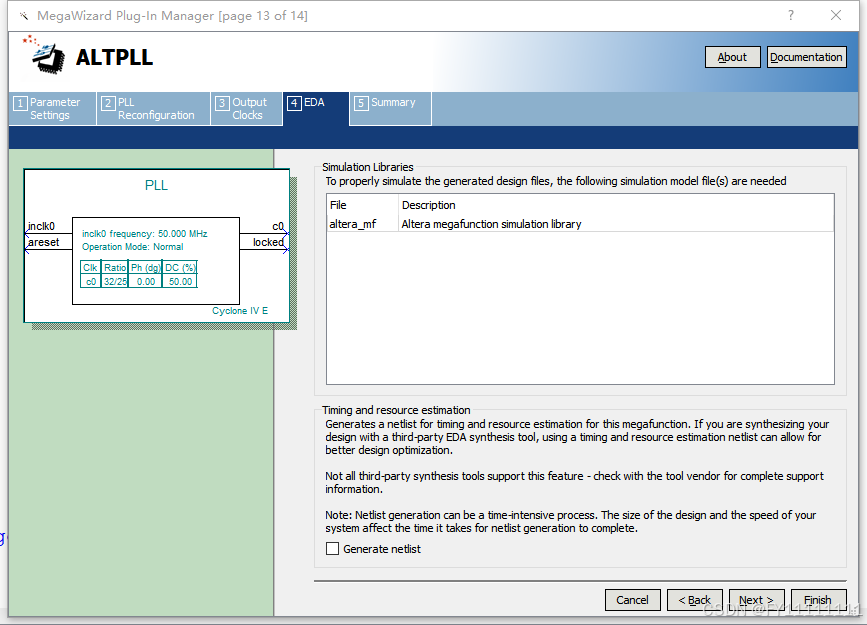

11、模拟库页面保持默认。

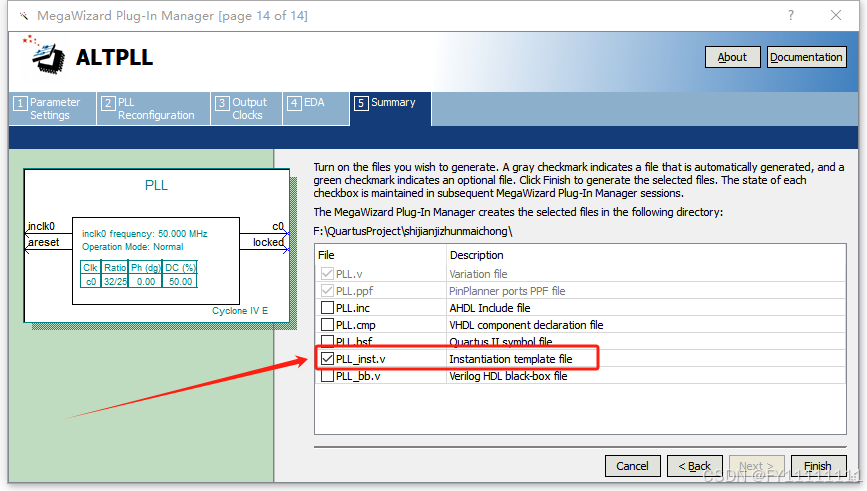

12、总结页面,勾画有例化2模板的inst文件即可,如图所示。点击Finish。

5093

5093

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?