同步复位

同步复位时,复位与时钟触发沿有关,所以在always的敏感变量中,只有时钟触发边沿,然后根据高电平或者低电平再判断复位电平。

同步低电平复位:

同步低电平复位:

always @ (posedge clk)

begin

if( ~rst )

...;

else

...;

end

同步高电平复位:

always @ (posedge clk)

begin

if( rst )

...;

else

...;

end异步复位

异步复位,说明复位是异步的,和时钟触发边沿无关,复位信号一旦来临就使得寄存器进行复位操作,复位信号出现在always块的敏感列表里。

对于异步的低电平复位,以下降沿作为触发边沿(高电平变为低电平的时刻),并且触发后判断复位是否为低电平,即

always @ (posedge clk or negedge rst)

begin

if( ~rst )

...;

else

...;

end对于异步的高电平复位,以上升沿作为触发边沿(低电平变为高电平的时刻),并且触发后判断复位是否为高电平,即:

always @ (posedge clk or posedge rst)

begin

if( rst )

...;

else

...;

end同步复位和异步复位的优缺点

同步复位:稳定,有利于进行时域分析,不易受毛刺干扰,而且有些端口只有同步复位端口。缺点是周期需要大于时钟周期,且大部分逻辑器件中的D触发器都只有异步复位端口,这样就需要插入组合逻辑满足,这样就会有一些延迟的因素。

异步复位:简单,反应快,复位电平可以小于一个时钟周期,大部分逻辑器件中的D触发器都只有异步复位端口;缺点是复位信号容易不满足建立时间和保持时间的要求,易出现亚稳态,容易有毛刺

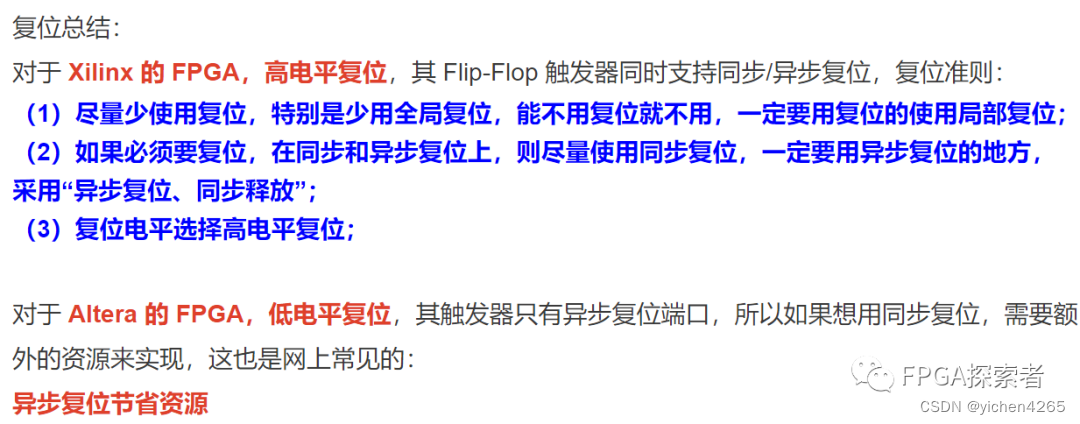

Xilinx推荐的复位策略

同步高复位

计数器和状态机必须复位

过多的复位会增加扇出,引起时序的不稳定

针对 Xilinx 的 FPGA:

(1)对于同一个触发器逻辑,因为同时支持异步和同步复位,所以异步复位并不会节省资源;

(2)对于其他的资源,比如 DSP48 等,同步复位更加节省资源。

首先,对于 DSP48,其内部还带有一些寄存器(只支持同步复位),如果使用异步复位,则会额外使用外部 Slice 中带异步复位的寄存器,而使用同步复位时,可以利用 DSP48 内部的寄存器;

Xilinx 的 FPGA,对于 DSP48、BRAM 资源,使用同步复位比异步复位更节省资源。

异步复位,同步释放(mediatec笔试题)

如果必须要复位,尽量选择同步复位,一定要用异步复位的地方,采用”异步复位。同步释放“

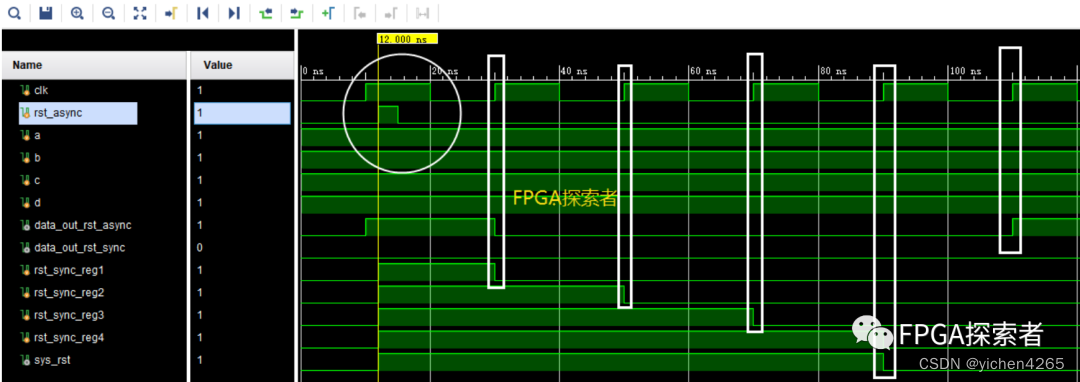

优势:经过异步复位同步释放处理后,相比于纯粹的异步复位,降低了异步复位信号释放导致亚稳态的可能性;相比同步复位,能够识别到同步复位中检测不到的复位信号(如上图所示的rst_async在同步复位是检测不到的);综合两者的优势,异步复位同步释放。

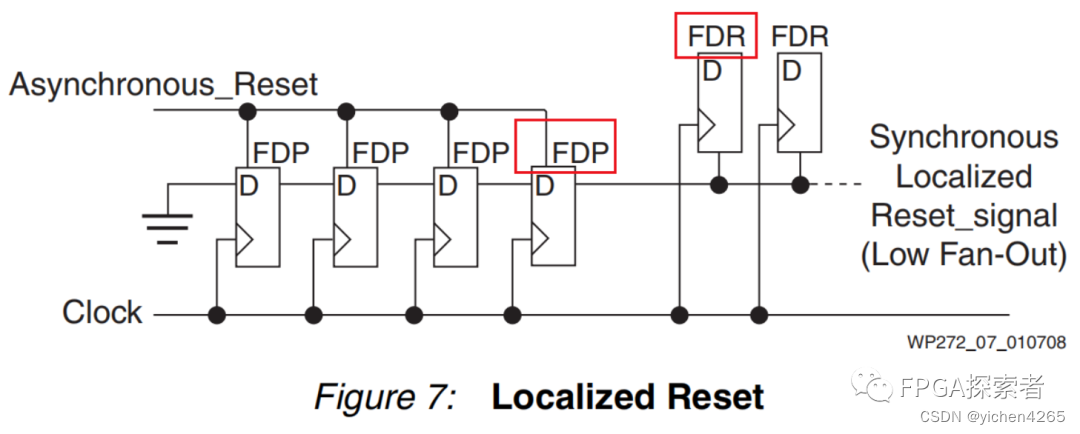

D触发器搭建电路:

对于输入的异步复位Asynchronous Reset,首先使用了4个触发器来做同步(一般用2个即可,4个出现亚稳态的概率更小),触发器类型为FDP(异步置位),同步化以后的复位信号去使用时综合出的触发器类型为FDR(同步复位),即在Xilinx中是将sys_rst按照方式2同步复位使用。

Verilog语言描述:

/******FPGA探索者******/

always @(posedge clk or posedge rst_async)

begin

if(rst_async == 1'b1) begin

rst_sync_reg1 <= 1'b1;

rst_sync_reg2 <= 1'b1;

rst_sync_reg3 <= 1'b1;

rst_sync_reg4 <= 1'b1;

end

else begin

rst_sync_reg1 <= 1'b0;

rst_sync_reg2 <= rst_sync_reg1;

rst_sync_reg3 <= rst_sync_reg2;

rst_sync_reg4 <= rst_sync_reg3;

end

end

wire sys_rst;

assign sys_rst = rst_sync_reg4;

always @(posedge clk)

begin

if(sys_rst == 1'b1) begin

data_out_rst_async <= 1'b0;

end

else begin

data_out_rst_async <= a & b & c & d;

end

end仿真结果:

异步复位过程:

rst_async异步复位一旦给出,用于同步的4个寄存器rst_sync_reg1~4立刻输出高电平“1”,在下一个时钟上升沿检测到同步复位并将输出data_out_rst_async复位;这四个D触发器是串联关系,所以会各慢一拍

同步释放过程:

异步复位信号释放后,经过同步的sys_rst经过一定周期后在时钟边沿同步释放

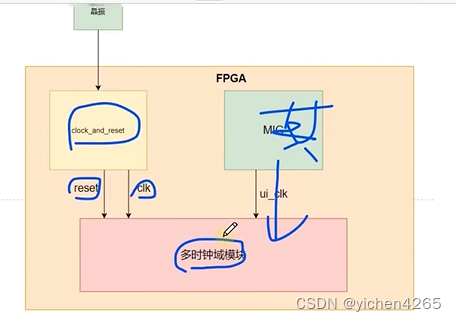

实际工程中的复位

一般单独弄一个时钟复位模块来管理不同的时钟和复位信号,锁相环pll分频

多时钟域下的同步复位设计,非常容易引起时序问题,例如读写DDR3时有不同的时钟clk和ui_clk

reset信号不能作为ui_clk的复位信号,打两拍也不够,常见的做法就是将其展宽后再打两拍。

313

313

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?