基于Quartus-II软件完成一个1位全加器的设计

1.原理图输入

1.新建工程

点击两次“next”后,如下图。

选择目标芯片:cycloneIVE系列的EP4CE115F29C7,如图:

直接next,之后到达完成界面,这里会看见关于整个工程的一些信息,核对一下是否正确,然后点击“finish”。

此时界面上会出现顶层文件名和项目名:

2…新建原理图文件

原理图编辑输入流程如下:

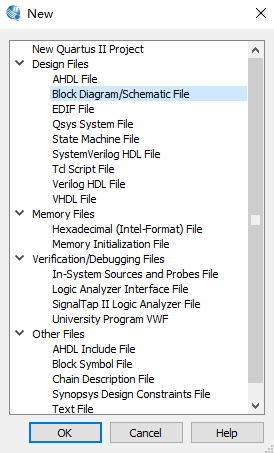

1.新建原理图文件。打开QuartusII,选菜单“File”一“New”,在弹出的“New-”对话框中选择“Design Files”的原理图文件编辑输入项“Block block diagram/schematic File"按"OK"后将打开原理图编辑窗。

2.在编辑窗中调入元件,完成半加器的原理图输入。

点击按纽或直接双击原理图空白处,从“ Symbol”窗中选择需要的符号,或者直接在“name”文本框中键入元件名,如“and2”为2输入与门,点OK按钮,即将元件调入原理图编辑窗中。例如为了设计半加器,分别调入元件and2,not,xnor和输入输出引脚input和output。并如图用点击拖动的方法连接好电路。然后分别在input和output的PIN NAME上双击使其变黑色,再用键盘分别输入各引脚名:a、b, co和s。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1108

1108

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?