ZYNQ

实际上是一个以处理器为核

心的系统,

PL

只是它的一个外设。

Zynq-7000

系列的亮点在于它包含了完整的

ARM

处理器系统,且处理器 系统中集成了内存控制器和大量的外设,使 Cortex-A9

处理器可以完全独立于可编程逻辑单元。而且实际上 在 ZYNQ

中,

PL

和

PS

两部分的供电电路是独立的,这样

PS

或

PL

部分不被使用的话就可以被断电。 在前面我们介绍 SOPC

时提到过,

FPGA

可以用来搭建嵌入式处理器,像

Xilinx

的

MicroBlaze

处理器 或者 Altera

的

Nios II

处理器。像这种使用

FPGA

的可编程逻辑资源搭建的处理器我们称之为“软核”处理 器,它的优势在于处理器的数量以及实现方式的灵活性。 而 ZYNQ 中集成的是一颗“硬核”处理器,它是硅芯片上专用且经过优化的硬件电路,硬核处理器的 优势是它可以获得相对较高的性能。另外,ZYNQ

中的硬件处理器和软核处理器并不冲突,我们完全可以 使用 PL

的逻辑资源搭建一个

Microblaze

软核处理器,来和

ARM

硬核处理器协同工作。

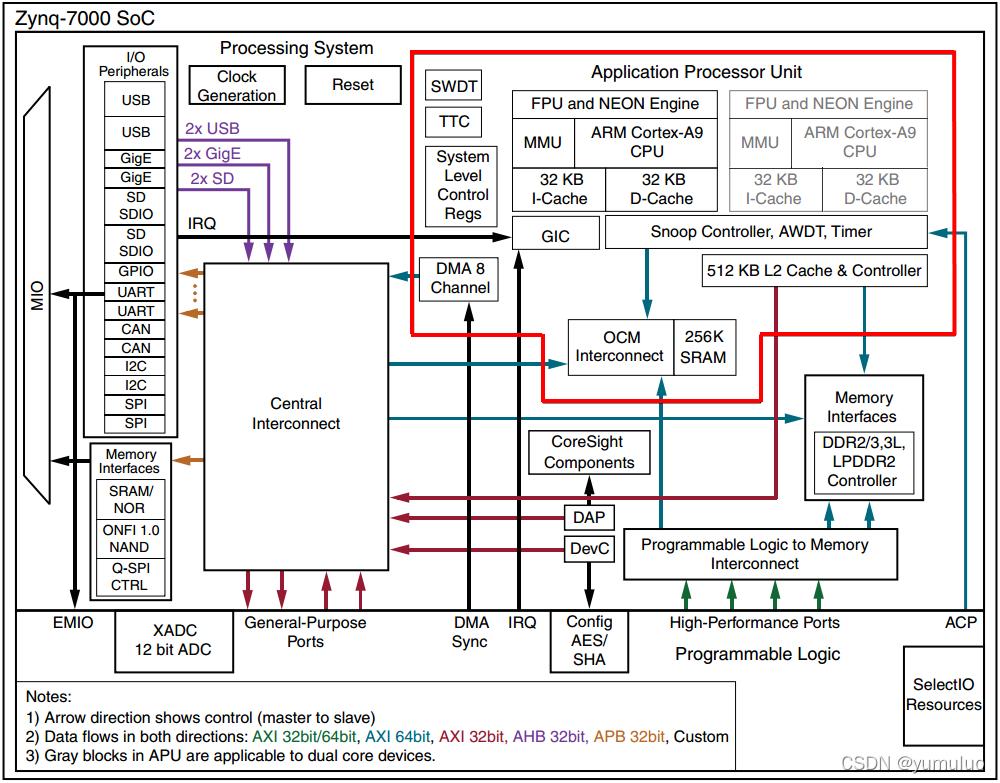

需要注意的是,

Zynq

处理器系统里并非只有

ARM

处理器,还有一组相关的处理资源,形成了一个应 用处理器单元(Application Processing Unit

,

APU

),另外还有扩展外设接口、

cache

存储器、存储器接口、 互联接口和时钟发生电路等。 ZYNQ 处理器系统(PS

)示意图如下所示,其中红色高亮区域为

APU

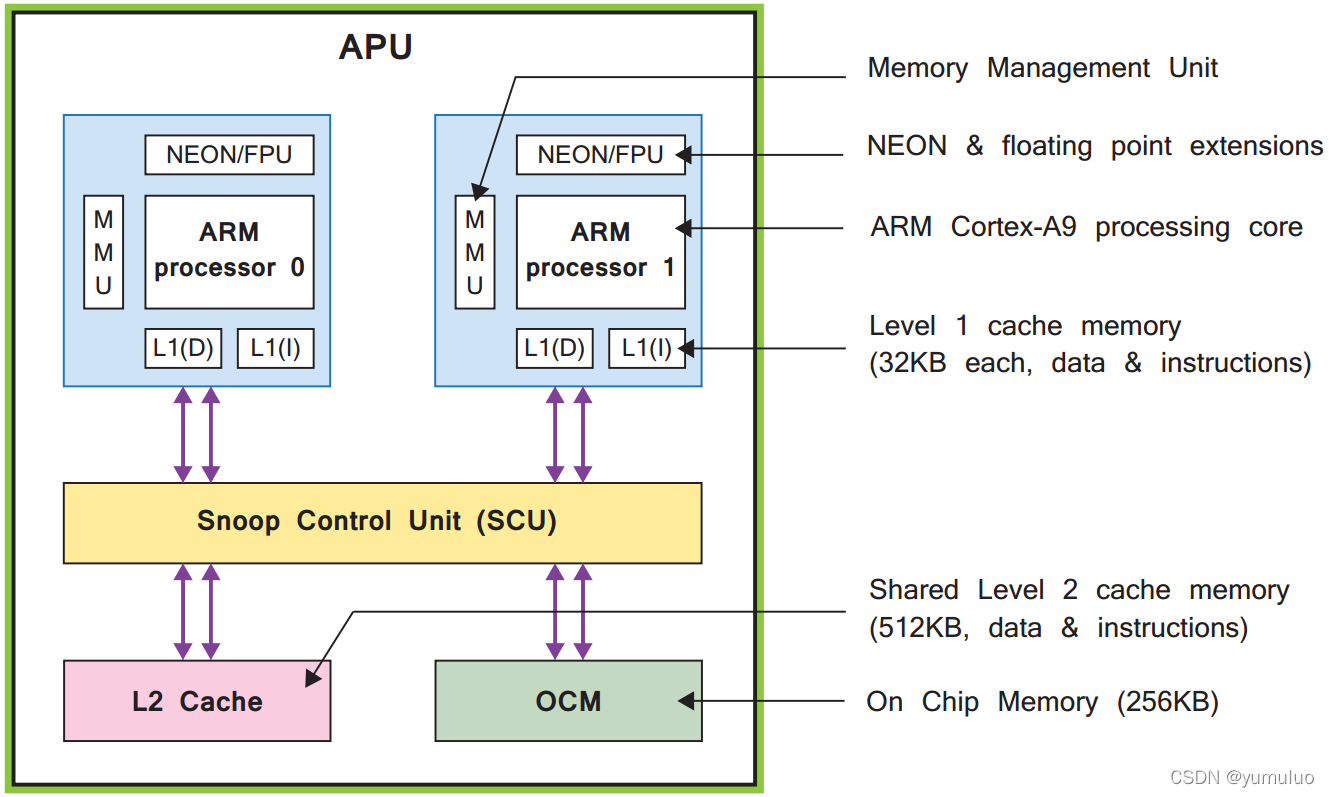

1) APU

如上图所示是

APU

的简化框图。

APU

主要是由两个

ARM

处理器核组成的,每个都关联了一些可计算 的单元:一个 NEONTM

媒体处理引擎(

Media Processing Engine

,

MPE

)和浮点单元(

Floating Point Unit

, FPU);一个内存管理单元(

Memory Management Unit

,

MMU

);和一个一级

cache

存储器(分为指令和 数据两个部分)。APU

里还有一个二级

cache

存储器,再往下还有片上存储器(

On Chip Memory

,

OCM

), 这些是两个 ARM

处理器共用的。最后,由一个一致性控制单元(

Snoop Control Unit

,

SCU

)在

ARM

核和 二级 cache

及

OCM

存储器之间形成了桥连接。

SCU

还部分负责与

PL

对接,图中没有标出这个接口

2)

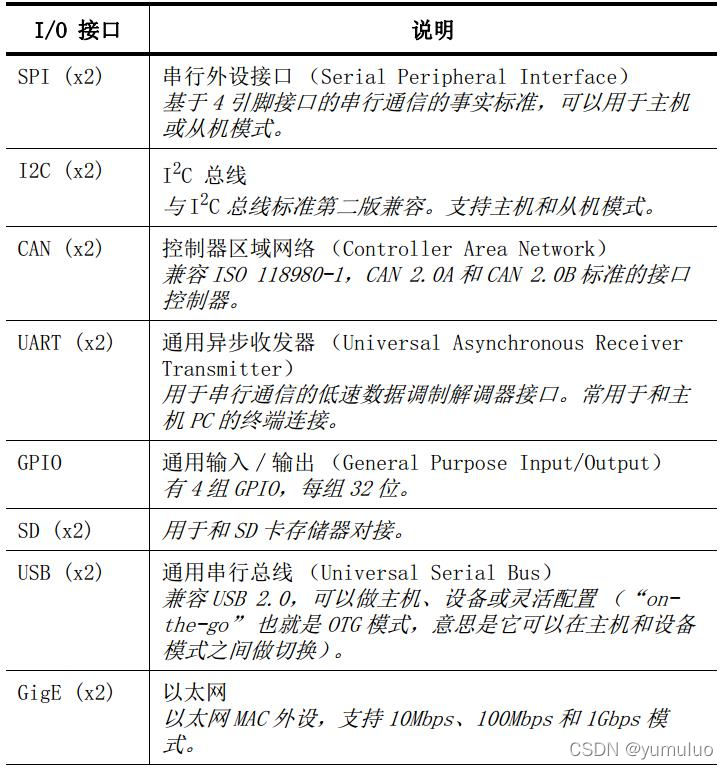

外部接口

如

图

1.4.1

所示,Zynq PS 实现了众多接口,既有 PS 和 PL 之间的,也有 PS 和外部部件之间的。 PS 和外部接口之间的通信主要是通过复用的输入/输出(Multiplexed Input/Output,MIO)实现的, 它提供了可以灵活配置的 54 个引脚,这表明外部设备和引脚之间的映射是可以按需定义的。当需要扩 展超过 54 个引脚的时候可以通过扩展 MIO(Extended MIO,EMIO)来实现,EMIO 并不是 PS 和外部连 接之间的直接通路,而是通过共用了 PL 的 I/O 资源来实现的。

PS 中可用的 I/O 包括标准通信接口和通用输入/输出(General Purpose Input/Output,GPIO),

GPIO 可以用做各种用途,包括简单的按钮、开关和 LED。如下图所示

4)

片上存储器

片上存储器包括

256kB

的

RAM

(

OCM

)和

128kB

的

ROM

(

BootROM

)。

OCM

支持两个

64

位

AXI

从 机接口端口,一个端口专用于通过 APU SCU

的

CPU/ACP

访问,而另一个是由

PS

和

PL

内其他所有的总线 主机所共享的。BootROM

是

ZYNQ

芯片上的一块非易失性存储器,它包含了

ZYNQ

所支持的配置器件的 驱动。BootROM

对于用户是不可见的,专门保留且只用于引导的过程。

5) AXI

接口

ZYNQ

将高性能

ARM Cotex-A

系列处理器与高性能

FPGA

在单芯片内紧密结合,为设计带来了如减小 体积和功耗、降低设计风险,增加设计灵活性等诸多优点。在将不同工艺特征的处理器与 FPGA

融合在一 个芯片上之后,片内处理器与 FPGA

之间的互联通路就成了

ZYNQ

芯片设计的重中之重。如果

Cotex-A9

与 FPGA 之间的数据交互成为瓶颈,那么处理器与

FPGA

结合的性能优势就不能发挥出来。 Xilinx 从

Spartan-6

和

Virtex-6

系列开始使用

AXI

协议来连接

IP

核。在

7

系列和

ZYNQ-7000 AP SoC

器 件中,Xilinx

在

IP

核中继续使用

AXI

协议。

AXI

的英文全称是

Advanced eXtensible Interface

,即高级可扩 展接口,它是 ARM

公司所提出的

AMBA

(

Advanced Microcontroller Bus Architecture

)协议的一部分。 AXI 协议是一种高性能、高带宽、低延迟的片内总线。

973

973

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?