学习目标:

- 一周掌握FPGA的GTX收发器使用及仿真

学习内容:

- GTX基本结构

- GTX参考时钟

- GTX接收、发送端口

- GTX IP 核调用

学习时间:

- 周一至周二上午完成GTX基本结构和GTX参考时钟的学习

- 周二下午 至 周四 学习GTX接收、发送端口

- 周五学习 GTX IP 核调用

- 周六完成GTX 收发测试

GTX基本结构:

-

GTX基本结构

7系列fpga GTX和GTH收发器是节能收发器,GTX收发器支持500 Mb/s至12.5 Gb/s的线路速率,GTH收发器支持13.1 Gb/s的线路速率。GTX/GTH收发器具有高度可配置性,并与FPGA的可编程逻辑资源紧密集成。CPLL最高支持线速6.x G,而QPLL则可超过10G;在通道线速较大(超过6.xGbps)时,IP会自动使用QPLL。GTXE2_COMMON、GTXE2_CHANNEL :是Xilinx的器件原语(primitive),原语是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数;原语类似最底层的描述方法。

PLL(Phase-Locked Loop,锁相环)是一种电路和控制系统中常见的反馈系统,用于产生一个输出信号,其相位和频率与一个参考信号相锁定。

SERDES(Serializer/Deserializer): 这是一种用于将并行数据转换为串行数据(串行化)或将串行数据转换为并行数据(反串行化)的技术。

PISO(Parallel-In, Serial-Out): 这是一类移位寄存器的结构,用于将并行输入数据按位顺序转换为串行输出。 -

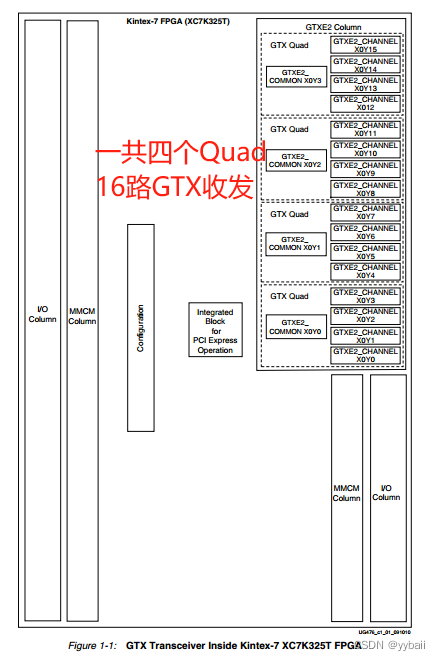

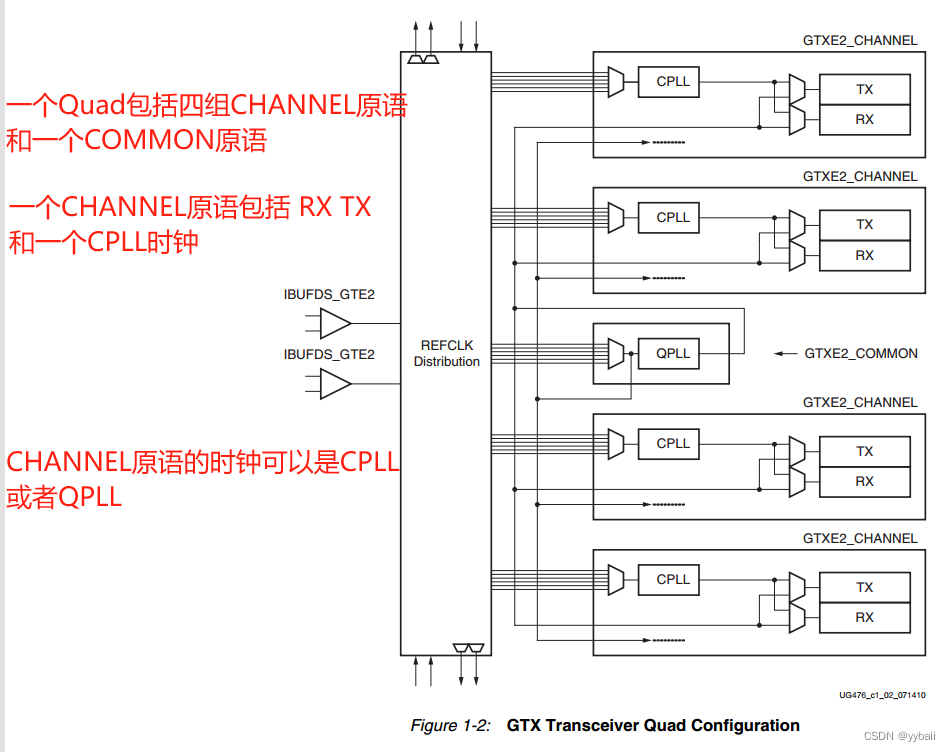

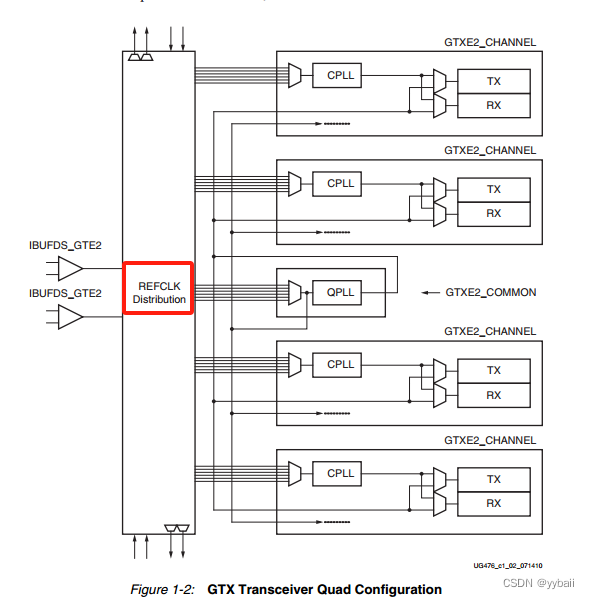

Xilinx 以 Quad 来对串行高速收发器进行分组,四个串行高速收发器和一个 COMMOM(QPLL)组成一个 Quad,每一个串行高速收发器称为一个 Channel(通道),每个Quad包含四个GTXE2_CHANNEL原语(每个CHANNEL包含一个GTX),一个GTXE2_COMMON原语,两个专用外部参考时钟引脚对和专用参考时钟路由的分组;QPLL :也就是一个Quad共用的PLL,属于GTXE2_COMMON;Channel:每个channel就是一个GTX,包含一个CPLL和一对收发器;CPLL : 每个Channel独有的PLL,属于GTXE2_CHANNEL。下图为四路 GTX 收发器在Kintex7 FPGA 芯片中的示意图

-

GTX 的具体内部逻辑框图如下所示,它由四个收发器通道 GTXE2_CHANNEL原语 和一个GTXE2_COMMON 原语组成。每路GTXE2_CHANNEL包含发送电路 TX 、接收电路 RX和CPLL时钟,GTXE2_CHANNEL的时钟可以来自于CPLL或者QPLL,可在IP配置界面里配置

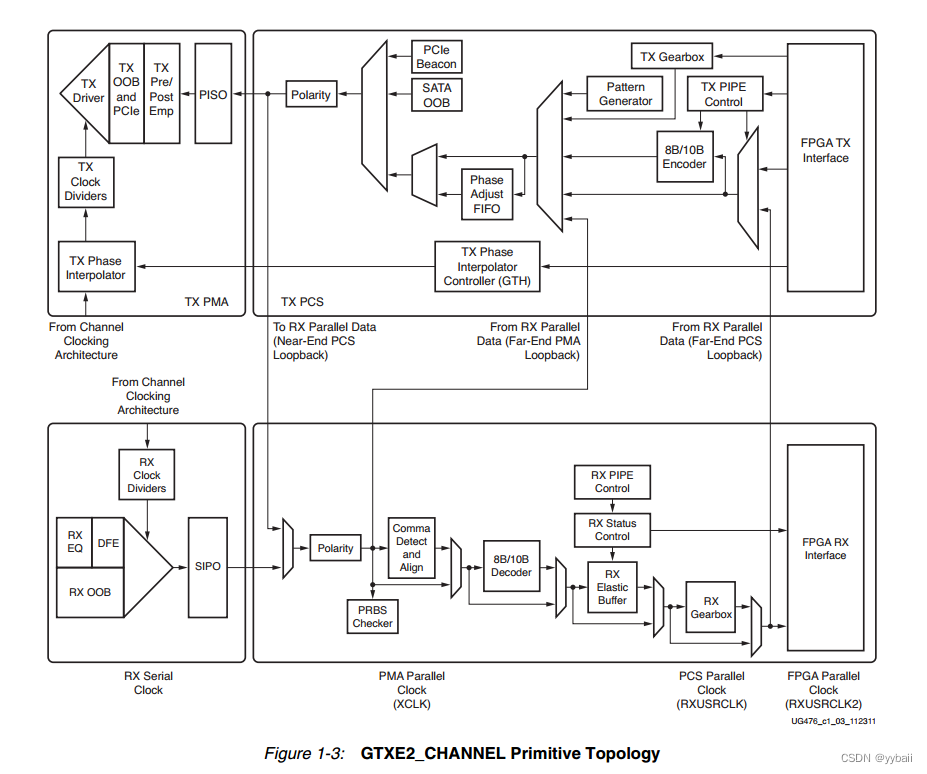

4. 每个GTXE2_CHANNEL的逻辑电路图如下所示:

GTXE2_CHANNEL 的发送端和接收端功能是独立的,均由 PMA(Physical Media Attachment,物理媒介适配层)和 PCS(Physical Coding Sublayer,物理编码子层)两个子层组成。其中 PMA 子层包含高速串并转换(PISO)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS 子层包含8B/10B 编解码、缓冲区、通道绑定和时钟修正等电路。PMA是最基本的单位,负责模拟部分,而PCS主要负责并行的数字电路处理,理论上来说PCS完全可以由逻辑设计完成;但是硬核专用电路实现肯定功能更强大更稳定。 5. GTXE2_CHANNEL 的发送端和接收端功能是独立的,均由 PMA(Physical Media Attachment,物理媒介适配层)和 PCS(Physical Coding Sublayer,物理编码子层)两个子层组成。其中 PMA 子层包含高速串并转换(Serdes)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS 子层包含8B/10B 编解码、缓冲区、通道绑定和时钟修正等电路。

5. GTXE2_CHANNEL 的发送端和接收端功能是独立的,均由 PMA(Physical Media Attachment,物理媒介适配层)和 PCS(Physical Coding Sublayer,物理编码子层)两个子层组成。其中 PMA 子层包含高速串并转换(Serdes)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS 子层包含8B/10B 编解码、缓冲区、通道绑定和时钟修正等电路。

6. GTXE2_COMMON 具有仅用于仿真的属性,以SIM_开头

- 每个GTX/GTH收发器通道和公共原语的位置由XY坐标系指定,该坐标系描述列号和列内的相对位置。

- GTX 模块有两个差分参考时钟输入管脚(MGTREFCLK0P/N 和 MGTREFCLK1P/N),作为 GTX 模块的参考时钟源,用户可以自行选择。一般的A7系列开发板上,都有一路 148.5Mhz 的 GTX 参考时钟连接到 MGTREFCLK0上,作为 GTX 的参考时钟。差分参考时钟通过IBUFDS 模块转换成单端时钟信号进入到 GTXE2_COMMOM 的QPLL或CPLL中,产生 TX 和 RX 电路中所需的时钟频率。TX 和 RX 收发器速度相同的话,TX 电路和 RX 电路可以使用同一个 PLL 产生的时钟,如果 TX 和 RX收发器速度不相同的话,需要使用不同的 PLL 时钟产生的时钟。参考时钟这里Xilinx给出的GT参考例程已经做得很好了,我们调用时其实不用修改;GTX 的参考时钟结构图如下:

GTX参考时钟:

- 参考时钟

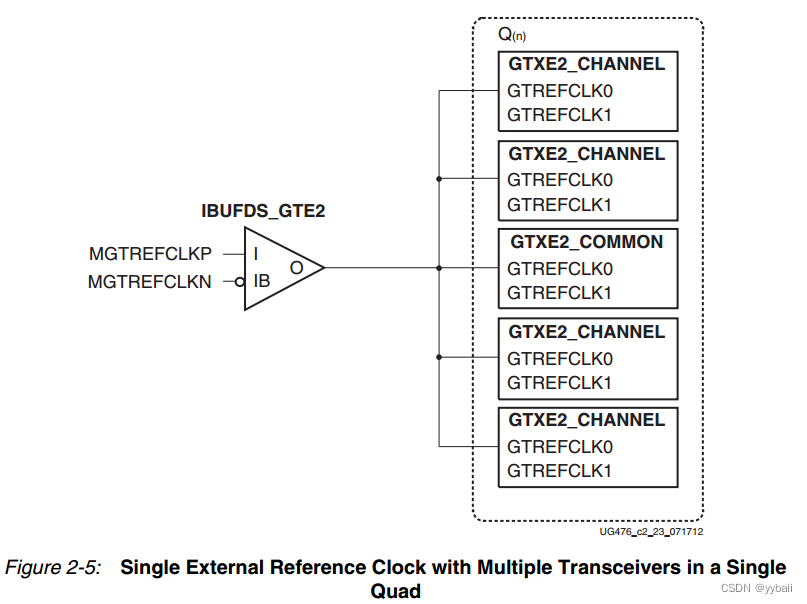

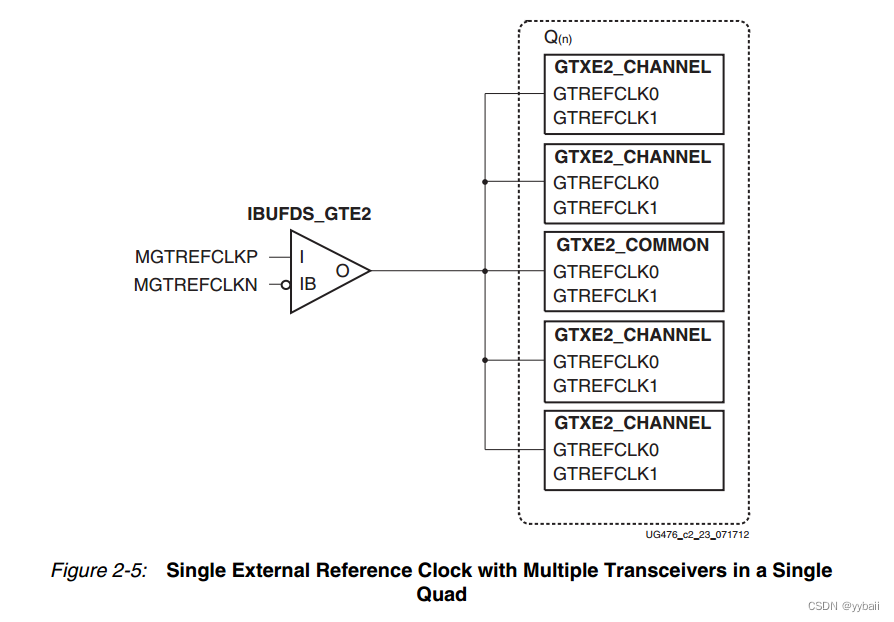

一个Q 含有两个IBUFDS_GTE2原语,其中输入可选,可以是MGTREFCLKP/N0,也可以是MGTREFCLKP/N1(此时钟一般为板子上的时钟),原语使用如下:

IBUFDS_GTE2 ibufds_instQ0_CLK1

(

.O (gtrefclk0), // gtrefclk1

.ODIV2 (),

.CEB ('b0),

.I (MGTREFCLKP0), // MGTREFCLKP1

.IB (MGTREFCLKN0) //MGTREFCLKN1

);

这样就能得到参考时钟gtrefclk0分别作为CPLL和QPLL的输入,当然CPLL和QPLL的输入时钟也可以来自其他相邻Q的时钟源。这里通过QPLLREFCLKSEL和CPLLREFCLKSEL进行选取。

每个Quad中的GTX通道有6个可用的参考时钟输入:

两个外部输入参考差分时钟,经过IBUFDS后就是GTREFCLK0和GTREFCLK1;

来自于Quad上面的两个参考时钟引脚对,GTSOUTHREFCLK0和GTSOUTHREFCLK1;

来自于Quad下面的两个参考时钟引脚对,GTNORTHREFCLK0和GTNORTHREFCLK1;

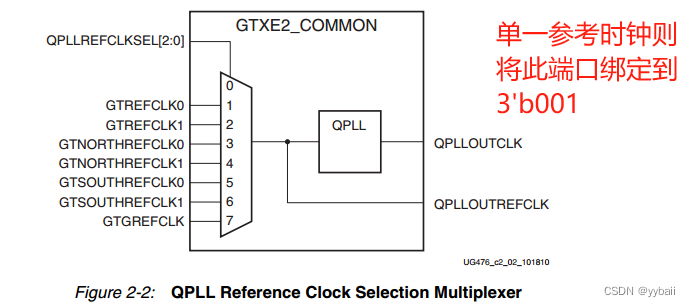

下图多了一个GTGREFCLK,这个时钟是由内部逻辑产生的参考时钟。貌似只用于内部测试。

a. 下图为单个GTXE2_COMMON/GTHE2_COMMON原语中的参考时钟多路复用器结构的详细视图。当多个参考时钟源连接到该多路复用器时,需要QPLLREFCLKSEL端口。单一参考时钟是最常用的。在这种情况下,QPLLREFCLKSEL端口可以绑定到3’b001。

b. 下图为 显示了单个GTXE2_CHANNEL/GTHE2_CHANNEL原语中的参考时钟多路复用器结构的详细视图。当有多个参考时钟源连接到该复用器时,需要使用CPLLREFCLKSEL端口。单一参考时钟是最常用的。在这种情况下,CPLLREFCLKSEL端口可以绑定到3’b001。

注意到红框的REFCLK Distribution了吗?专用参考时钟布线。

REFCLK Distribution的上下参考时钟引脚分别为南北时钟输入引脚。用于Quad之间共享参考时钟;也就是说,并不一定每一个Quad都需要外部参考时钟,有的Quad可以和其他Quad共享参考时钟,而共享的来源就是南北时钟输入引脚。Quad的南北参考时钟称为GTSOUTHREFCLK以及GTNORTHREFCLK。

- 外部参考时钟

QPLL或者CPLL的时钟输出分别可以供给TX和RX端选用作为输入时钟源,这里涉及到TXOUTCLK和RXOUTCLK,这两个时钟也是可以选择输入源的,可以来自GTXE2_CHANNEL也可以来自GTHE2_COMMON。

a. 用户设计将IBUFDS_GTE2输出(O)连接到GTXE2_COMMON/ GTHE2_COMMON或GTXE2_CHANNEL/GTHE2_CHANNEL原语的GTREFCLK0或GTREFCLK1端口,其中包含参考时钟选择多路复用器。根据线路速率要求,用户设计可以灵活地使用QPLL或CPLL的不同组合来驱动TX和/或RX数据路径。

b. 单个外部参考时钟连接到单个Quad内的多个收发器。用户设计将IBUFDS_GTE2输出(O)连接到GTX收发器的GTXE2_COMMON和GTXE2_CHANNEL原语的GTREFCLK0端口,以及GTH收发器的GTHE2_COMMON和GTHE2_CHANNEL原语。

c. 单个时钟引脚对可以获取的最大收发器数为12。1个外部参考时钟所驱动的Quad总数不超过3个,或驱动的Transceiver不超过12个。超过12个收发器的设计需要使用多个外部时钟引脚,以确保遵循控制抖动的规则.

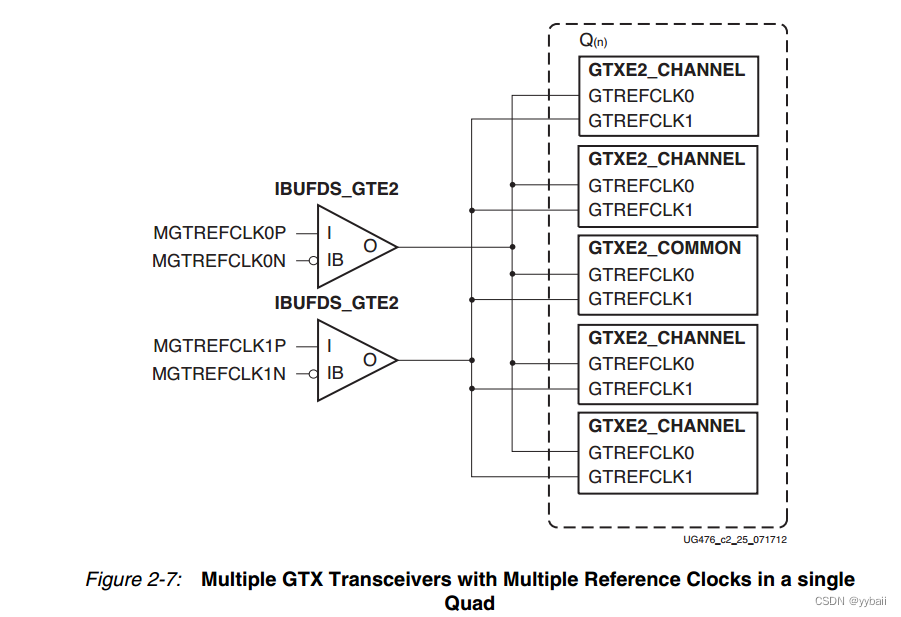

(1)同一个QUAD中,多个GTX Transceiver使用多个参考时钟

每个Quad有两个专用的差分时钟输入引脚(MGTREFCLK0[P/N]或 MGTREFCLK1[P/N]) ,可以连接到外部时钟源。 每个专用的参考时钟引脚对输入进来后必须例化IBUFDS_GTE2,再给到GTX使用。

MGTREFCLK0[P/N]连接到GTREFCLK0,将MGTREFCLK1[P/N]连接到GTREFCLK1管脚。

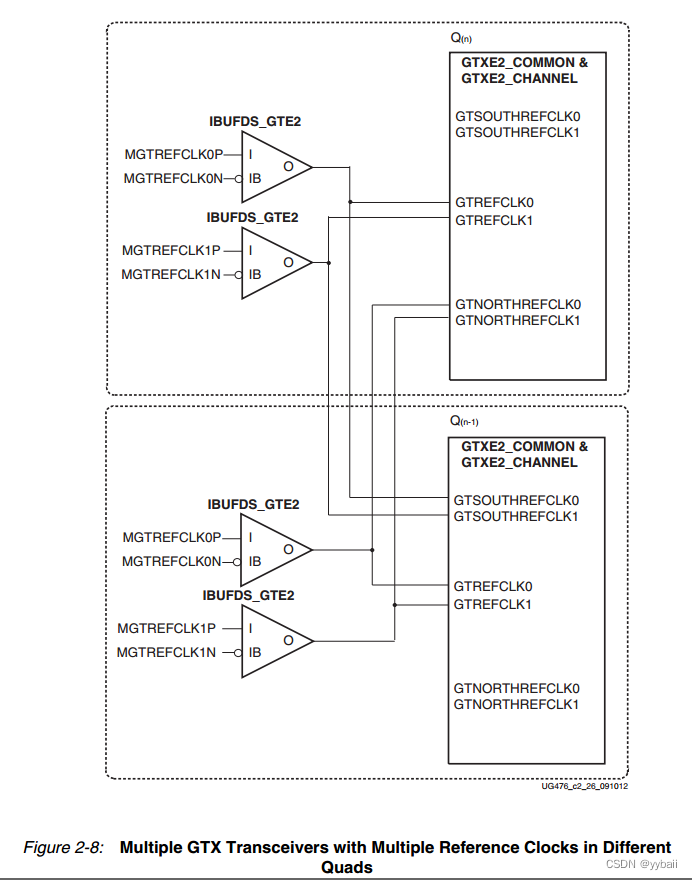

d. 下图显示了一个属于一个Quad的收发器如何通过使用NORTHREFCLK和SOUTHREFCLK端口访问另一个Quad的专用参考时钟的示例。在每个GTX或GTH收发器锁相环有多个参考时钟选项的情况下,用户设计时需要根据设计要求设置QPLLREFCLKSEL[2:0]和CPLLREFCLKSEL[2:0]。

(2)不同QUAD中,多个GTX Transceiver 使用多个参考时钟

参考时钟选择结构的灵活性允许Quad中的每个Transceiver都可以访问上下Quad中的专用参考时钟。

在每个GTX有多个参考时钟选项的情况下,设计的时候根据需求设置 QPLLREFCLKSEL[2:0]和CPLLREFCLKSEL[2:0]。该遵守的规则还是要遵守的:1个外部参考时钟所驱动的Quad总数不超过3个,或驱动的Transceiver不超过12个。

d. Channel PLL

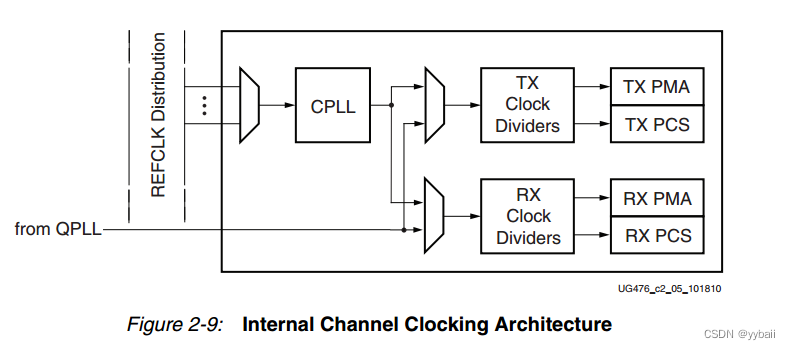

通道内部时钟架构如下图所示。TX和RX时钟分频器可以分别从QPLL或CPLL中选择时钟,以允许TX和RX数据路径使用不同的参考时钟输入在异步频率下工作。

CPLL输出给TX和RX时钟分频模块,它们控制PMA和PCS模块使用的串行和并行时钟的生成。CPLL可以在TX和RX数据路径之间共享,如果它们以相同VCO频率的整数倍的线速率工作。

e. 动态从CPLL切换到QPLL:

①:通过取消QPLLPD和QPLLRESET端口上电QPLL。等待端口QPLLLOCK = 1。

注意:QPLLPD要么在配置后处于下电模式,要么假定QPLLPD之前已经正确断言,按照要求,QPLLPD应该在配置完成后等待至少500 ns后才断言为高电平。

②断言端口GTTXRESET和/或GTRXRESET。设置端口TXSYSCLKSEL[0] = 1’b1和RXSYSCLKSEL[0] = 1’b1。断言端口[TX/RX]USERRDY。

③取消GTTXRESET和/或GTRXRESET。等待TXRESETDONE = 1’b1和RXRESETDONE = 1’b1。

④通过断言CPLLRESET和CPLLPD将CPLL下电,节省电源。

⑤继续收发器操作。

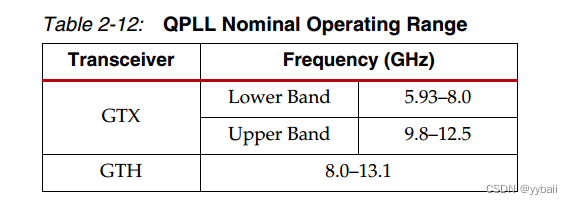

4. Quad PLL(上图中所示)

a. QPLL可以在同一个Quad里共享,但不能与其他Quad的CHANNEL原语共享。当以高于CPLL工作范围的线路速率操作通道时,需要使用QPLL。GTXE2_COMMON原语封装了GTX QPLL,并且必须在使用GTX QPLL时实例化。

b. QPLL输出在同一Quad内为每个串行收发器通道的TX和RX时钟分频块提供馈电,这些分频块控制PMA和PCS块使用的串行和并行时钟的生成。

c. 动态改变QPLL设置

①当准备好(所有有效的数据传输或接收),通过端口QPLLREFCLKSEL和/或DRP提供更改表2-10中列出的属性。

②请按照第64页QPLL reset中详细的复位指南进行操作。

③当QPLL锁定时,断言GTTXRESET和/或GTRXRESET,并遵循第68页GTX/GTH收发器TX复位响应GTTXRESET脉冲和第80页GTX/GTH收发器RX复位响应GTRXRESET脉冲中的详细指导方针。

④继续收发机操作。

d. 动态从QPLL转换到CPLL

①通过取消CPLLPD和CPLLRESET端口使CPLL上电。等待端口CPLLLOCK = 1。

②断言端口GTTXRESET和/或GTRXRESET。设置端口TXSYSCLKSEL[0] = 1’b0和RXSYSCLKSEL[0] = 1’b0。断言端口[TX/RX]USERRDY。

③取消GTTXRESET和/或GTRXRESET。等待TXRESETDONE = 1’b1和RXRESETDONE = 1’b1。

④通过断言QPLLRESET和QPLLPD将QPLL下电以节省电源。

⑤继续收发机操作。

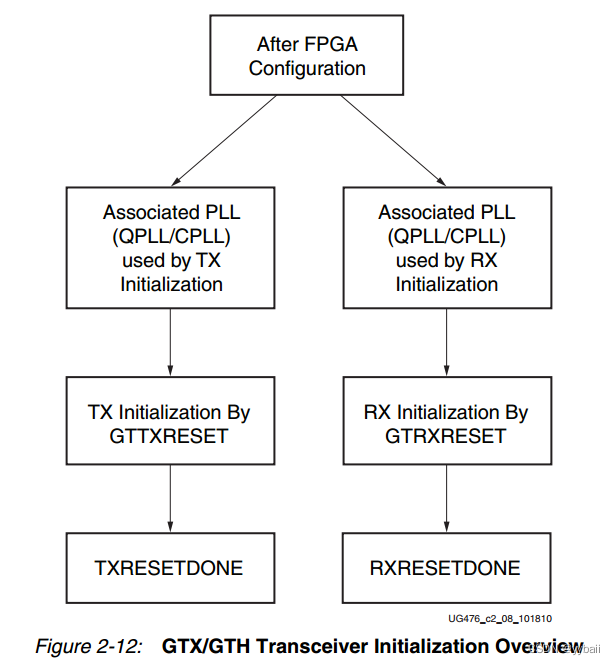

- GTX的复位和初始化

a. 如下图所示,GTX/GTH收发器TX和RX初始化包括两个步骤:①初始化驱动TX/ rx2的关联锁相环。②初始化TX和RX数据路径(PMA + PCS) 。GTX/GTH收发器TX和RX可以接收来自QPLL或CPLL的时钟。在初始化TX和RX之前,必须先初始化TX和RX使用的关联PLL (QPLL/CPLL)。TX和RX使用的任何锁相环都是单独复位的,其复位操作完全独立于所有TX和RX复位。只有当关联的锁相环被锁定后,才能初始化TX和RX数据路径

b. 复位

GTX/GTH收发器提供两种类型的复位:初始化和组件。

所有复位端口在被驱动为High时启动内部复位状态机,保持复位状态直到这些端口驱动为低,都是异步的。

•初始化复位:此复位用于完成GTX/GTH收发器初始化。必须在设备上电配置后使用。在正常工作时,必要时,GTTXRESET和GTRXRESET也可用于重新初始化GTX/GTH收发器TX和RX。GTTXRESET是GTX/GTH收发器TX的初始化复位端口,GTRXRESET是GTX/GTH收发器RX的初始化复位端口。

•组件复位:此复位用于GTX/GTH收发器正常工作时的特殊情况和特定分段复位。TX组件复位端口包括TXPMARESET和TXPCSRESET。RX组件复位接口包括RXPMARESET、RXDFELPMRESET、EYESCANRESET、RXPCSRESET、RXBUFRESET和RXOOBRESET。

c. 复位模式:GTRESETSEL选择模式,RESETOVRD必须为低

GTX的RX端复位:顺序模式和单模式;TX端复位只支持顺序复位。

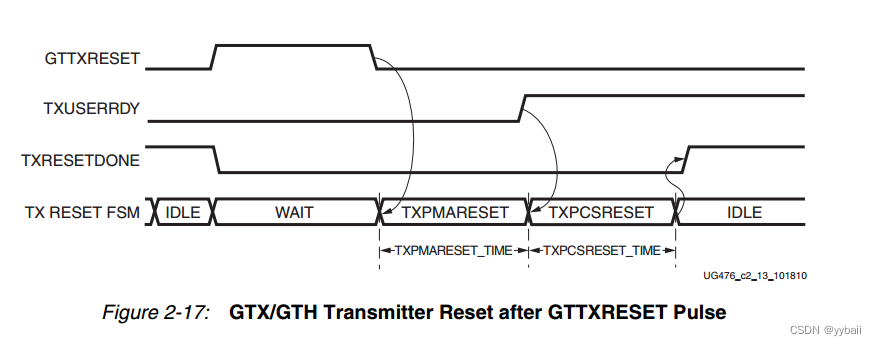

①顺序模式:复位状态机从初始化或组件复位输入驱动High开始,在复位状态机请求复位状态后依次进行所有状态,如图2-15 (GTX/GTH收发器TX)或图2-20 (GTX/GTH收发器RX)所示,直到完成。当(TX/RX)RESETDONE从Low转换到High时,顺序模式复位流完成。

②重置状态机仅在由其属性设置的预定时间内独立执行所请求的组件重置。GTX/GTH收发器RX在请求状态之后不处理任何状态,如图2-20所示。请求的复位可以是任何组件复位,以复位PMA、PCS或它们内部的功能块。当RXRESETDONE从Low转换到High时,单模复位完成。

d. CPLL复位

必须通过CPLLPD端口将CPLL下电,直到在fabric中检测到参考时钟边。CPLLPD去断言后,需要复位CPLL才能使用。

每个GTX/GTH收发通道有3个专用端口用于CPLL复位。

①CPLLRESET:是复位CPLL的输入。

②CPLLLOCK:是复位过程完成的输出。

③CPLLLOCKEN:输入信号,该active-High信号使能CPLL锁检测器。

e. QPLL复位

QPLL必须复位才能使用。

每个GTX/GTH收发器Quad有三个专用端口用于QPLL复位。

①QPLLRESET是复位QPLL的输入。

②QPLLLOCK是指示重置过程完成的输出。

③QPLLLOCKEN:

f. GTX收发器的TX端初始化和复位

TX分为两个复位区域:TX PMA和TX PCS。

该分区只允许按顺序进行TX初始化和复位操作。

激活GTTXRESET输入可以自动触发一个完整的异步TX重置。复位状态机执行复位顺序,如图2-15所示,复位顺序覆盖整个TX PMA和TX pc。在正常操作期间,当需要时,顺序模式允许用户从激活TXPMARESET复位TX,并继续复位状态机,直到TXRESETDONE从Low转换到High。

在检测到TXUSERRDY为High之前,TX复位状态机不会复位PCS。满足以下条件后,用户应驱动TXUSERRDY High:①当使用PLL或MMCM时,包括TXUSRCLK/TXUSRCLK2在内的应用程序使用的所有时钟都显示为稳定或锁定。②户界面准备好将数据传输到GTX/GTH收发器。

在检测到TXUSERRDY为High之前,TX复位状态机不会复位PCS。满足以下条件后,用户应驱动TXUSERRDY High:①当使用PLL或MMCM时,包括TXUSRCLK/TXUSRCLK2在内的应用程序使用的所有时钟都显示为稳定或锁定。②户界面准备好将数据传输到GTX/GTH收发器。

TX复位顺序不会跟随全局GSR自动启动。它必须满足以下条件:①GTRESETSEL必须为Low才能使用顺序模式。②必须使用GTTXRESET。③在整个复位过程中,TXPMARESET和TXPCSRESET必须一直被驱动为Low,直到TXRESETDONE被检测到High。④关联锁相环锁定之前,GTTXRESET不能被驱动为Low。

GTX/GTH收发器允许用户在任何时候通过向GTTXRESET发送一个active-High脉冲来完全重置整个TX。

TXPMARESET_TIME和TXPCSRESET_TIME可以静态设置,也可以通过DRP端口重新编程,在应用GTTXRESET之前调整所需的复位时间。

TX PMA和TX PCS可以单独复位。在TXPMARESET或TXPCSRESET进程完成之前,GTTXRESET必须一直被驱动为Low。TXPCSRESET必须在TXPMARESET过程中持续低电平驱动。

g. GTX收发器的RX端初始化和复位

GTX/GTH收发器允许用户完全重置整个GTX/GTH收发器RX在任何时候需要通过发送GTRXRESET一个有效的高脉冲

RXOUT_DIV = 2, 4, 8, or 16 and

RX internal data width is 20- or 40-bit (RX_DATA_WIDTH = 20, 40, or 80)

-

下电

一共有四种:

CPLLPD :CHANNEL PLL power down

QPLLPD :Quad PLL power down

TXPD

RXPD -

回环测试模式:近端模式和远端模式

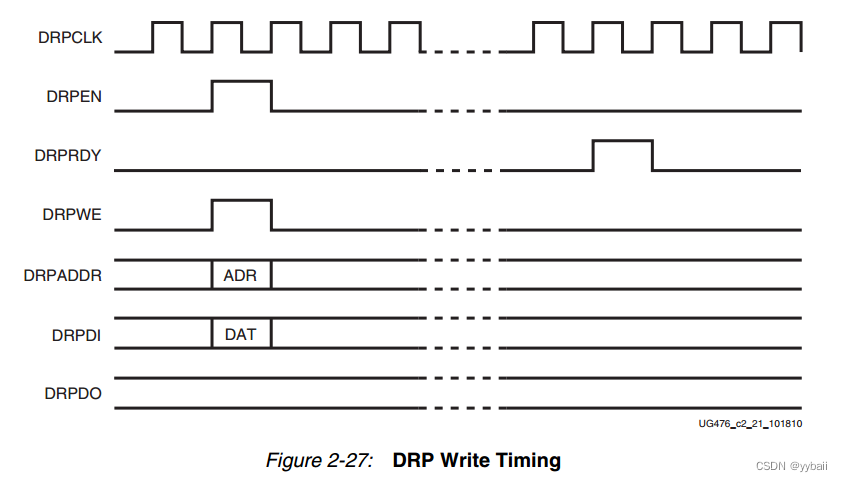

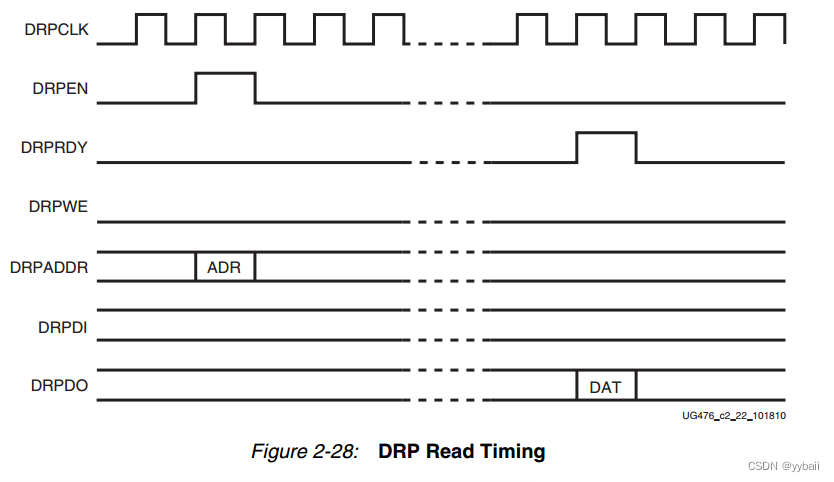

8. 动态重配置(DRP)

动态重配置端口(DRP)允许动态更改GTXE2_CHANNEL/GTHE2_CHANNEL和GTXE2_COMMON/ GTHE2_COMMON原语的参数。DRP接口是一个处理器友好的同步接口,具有地址总线(DRPADDR)和用于向原语读取(DRPDO)和写入(DRPDI)配置数据的分离数据总线。使能信号(DRPEN)、读写信号(DRPWE)和就绪/有效信号(DRPRDY)是实现读写操作、指示操作完成或指示数据可用的控制信号

写时序:

读时序:

9. 数据监控器

自适应算法优化链路的两种接收模式:LPM 和 DFE

数字监视器提供了这些适应回路的当前状态的可见性。

数字监视器需要一个自由运行的时钟; DRPCLK或RXUSRCLK2可用于此。

具体端口见P96 97,捕获代码见P101-106.

GTX发送接口:

GTX接收接口:

- GTX基本结构

- GTX参考时钟

- GTX接收、发送端口

- GTX IP 核调用

GTX IP 核调用:

- GTX基本结构

- GTX参考时钟

- GTX接收、发送端口

- GTX IP 核调用

GTX收发测试:

- GTX基本结构

- GTX参考时钟

- GTX接收、发送端口

- GTX IP 核调用

2797

2797

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?