并行语句

主要包括

- 连续赋值语句—assign语句

- Verilog程序块语句—initial与always块

- Verilog实例化语句----单独实例化与数组实例化

- verilog生成语句

- verilog函数调用语句

- Verilog模块说明语句

verilog生成语句

生成语句的关键字为generate,按照形式分为循环生成和条件生成。

(1)循环生成

基本语法如下:

genvar <var>;

generate

for(<var>=0 ; <var> < <limit> ; <var> = <var> + 1'b1)

begin:<label>

<statement>

end

endgenerate

注意:

a、for语句中的变量必须用关键字genvar定义,genvar关键字可以写在generate

语句外面,也可写在generate语句里面,只要先于for语句声明即可。

b、必须给循环段起一个名字。即

input [3:0] a,b;

outpt[3:0] c,d;

generate

genvar i

for (i=0 ; i < 4; i = i + 1)

begin: genExample

myAnd instance(.a(a) , .b(b), .c(c));

assign d[i] = a[i];

end

endgenerate

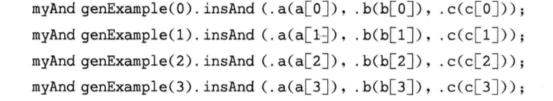

结果为

(2)条件生成

generate-if语句

generate

if(<condition>) begin:<label_1>

<code>;

end else if(<cindition>)begin:<label_2>

<code>;

end else begin:<label_3>

<code>;

end

endgenerate

注:

a、必须为常量比较。

b、if语句中,begin-end只有在有多条语句时才是必须的。

c、每一条分支的名称是可选的。与循环语句不同。

*生成打的电路一旦连通,要想更改必需重新编译——即生成的电路不是动态的没有

用到多路选择器。如果需要动态选择,直接用assign写多路选择器。

(3)generate-case语句

generate

case(<constant_expession>)

<value>:begin:<label_1>

<code>;

end

<value>:begin:<label_2>

<code>;

end

......

default:begin:<label_n>

<code>

end

endcase

endgenerate

注:与generate-if相同

Verilog函数调用语句

函数的定义可以放在模块实现部分的声明部分,function语法定义如下:

function[<lower>:<upper>]<output_name>;

input <name>;

<other inputs>

<variable declaration>

begin

<statement>

end

endfunction

注:

a、<output_name>既是是输出的变量名也是函数调用名,位宽由function

关键字后面的范围指定。

b、中,只能够声明寄存器类型的变量。

c、函数体中语句只能使用阻塞赋值符号;

d、函数调用的时候只能使用位置赋值,需要按照input的顺序罗列变量

e、函数调用可以在并行语句中也可以在串行语句中。

f、函数中可以调用别的函数;

g、函数支持递归,不过一般用于仿真;

h、函数不能调用任务,主要由于任务中可以有定时相关语句,而函数中不能有

例1:

moudule tft(

input clk,a,b,c,

output reg d,e,g

);

function andFunc;

input a;

input b;

begin

andFunc = a&b;

end

endfunction

always@(posedge clk)begin

e <= andFunc(a,b); //非阻塞赋值

end

always@(*)begin

d = andFunc(a,b);

end

assign g = andFunc(a,b);

endmodule

625

625

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?