系列文章目录

前言

之前学习了一些基本时序约束的类别,包括主时钟约束、虚拟时钟约束、输入输出约束、多周期约束等等,但大多都是纸上谈兵,目前打算在这个学期结束前,阅读大量文献,学习他们的时序约束经验,并且在数据采集板上完成实验验证。

文献1:时钟移位

参考文献:[1]刘垚,王维,巩玉振等.在Altera的FPGA中实现高速Link口的时序约束方法[J].测控技术,2012,31(01):

看了一篇12年的老文章了,发现自己真的很多东西不懂,简单记录一下我的总结和疑问,也许后面能够解决

文献说简单的时序约束虽然能够满足设计要求,但是在I/O端口上可能会出现错误,这我确实在一块1.8GSPS的数据采集板中进行过测试,当我只保留下ADC传给FPGA的数据同步时钟的虚拟时钟约束,确实在部分采集点出现了噪点,(虽然没有加入输入延迟约束,但可能FPGA自动加入了输入延迟约束,因为当我在将输入延迟约束放宽的时候,噪点会比不加输入延迟约束还要多),而加入输入延迟约束(set input delay)的时候,并且将约束设置参数设置较小的时候,那些采集点就正确了,但目前没搞清楚这个约束的参数是如何得出的。

文献在实现逻辑功能的时候,经常设置移位时钟,通过不同相位的同频时钟,完成数据的接收等功能。在实际测试中,对数据叠加和数据输出…

文章还提出,对于300MHz的DDR信号,相当于用600MHz的SDR触发,也是一种变通吧。我之前是将数据采集模块复制了一次,一次上升沿捕获处理,一次下降沿捕获处理,只能说特别低级冗余的方法。

文章说到ADC提供给FPGA数据及数据同步时钟,指出如果直接对该数据和时钟进行约束,不理想,数据到FPGA,时钟到FPGA都有延迟,最好将时钟进行虚拟时钟约束,约束后再进行数据延迟约束,调试更容易。我不太理解这里的第一种方法,因为当我去除虚拟时钟约束的时候,FPGA无法识别到这个时钟(450MHz),整个模块工作异常。

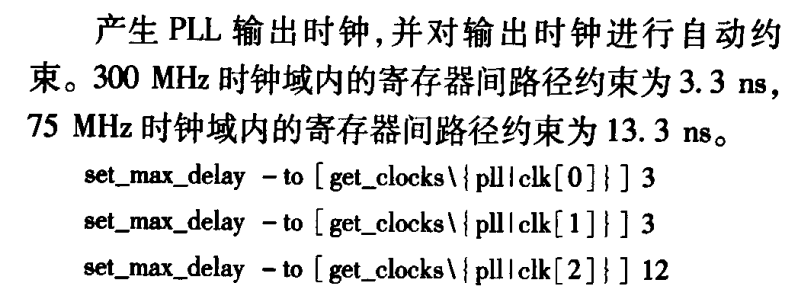

文献中有些奇怪的约束:

没看懂这个约束

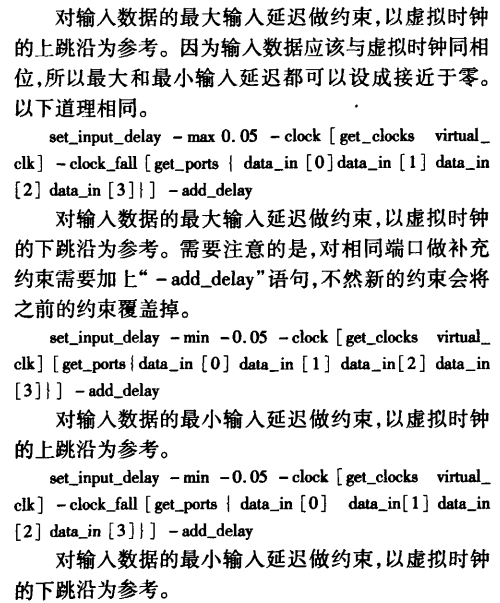

这里是DDR方式,所以上下边沿都设置了约束,这里好像是因为没有PCB延时和芯片延时Tco。

对输入输出延迟约束,我试了试高速数据采集板这样约束,发现这个参数设置范围很宽泛,没有什么固定值,基本0.05-1.2什么的都可以

Logiclock

文中提到了编译消耗过多时间的时候,可以使用LogicLock的功能,我查了一下还挺有用的:

参考:如何在quartus下做逻辑锁定(quartus,逻辑锁定)

参考:定义逻辑锁定区域(Logic Lock Region)

先说别人的经验,再给项目代码添加一个SPI模块的时候,添加进去后,综合后有时候正常有时候不正常,所以判断是综合器问题。(感觉FPGA就像一个自动乱布线的PCB一样)

当逻辑锁定后,它能保证被锁定的模块在下一次综合不被改变。当我们编译了一个可以运行的正常项目的时候,对一些不变的模块可以进行锁定,这样在项目整合的时候,防止一些共用资源导致重新布局布线,使得出现时序不收敛的问题等等。

相当于物理分区,但是坏处是时序分析后的Fmax都要更低一些,如果没有使用LogicLock,编译器可以自动从全局出发去做出做大的优化,而我们人为地进行了物理分区限定,那即使可能每个小模块做到了很好的优化,但是由于各个区域之间的布局布线受到了限制。

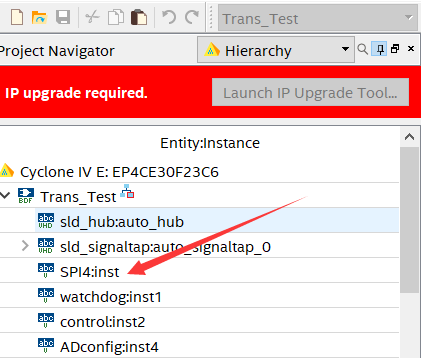

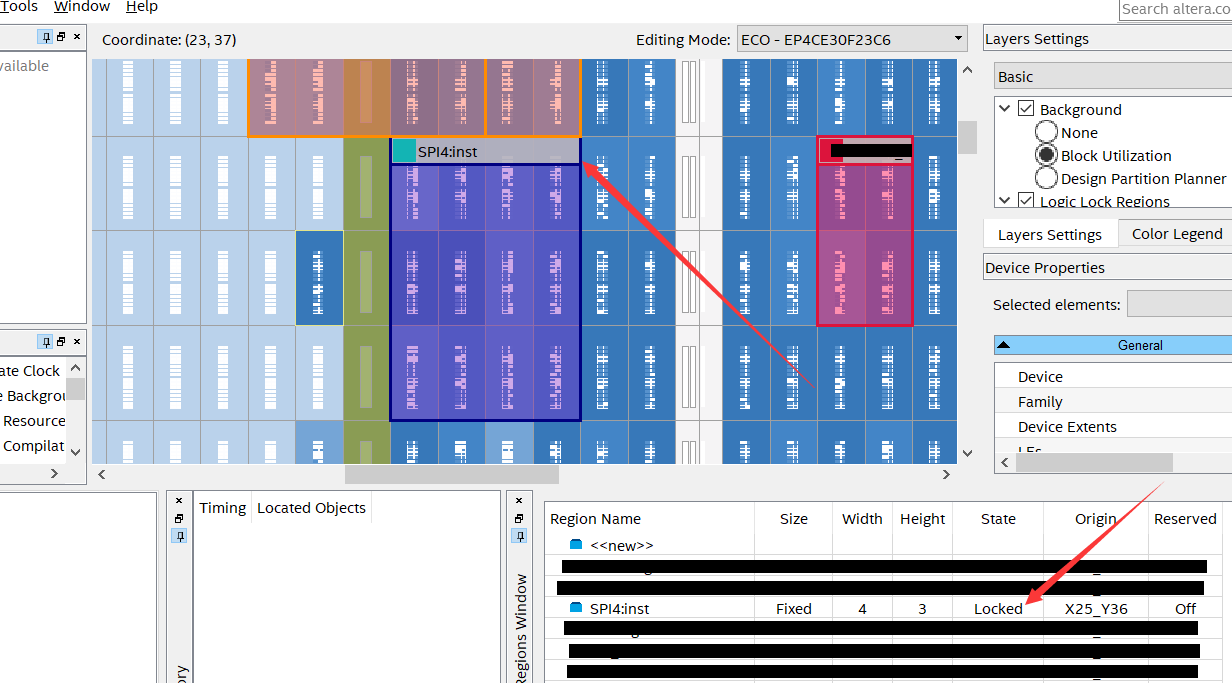

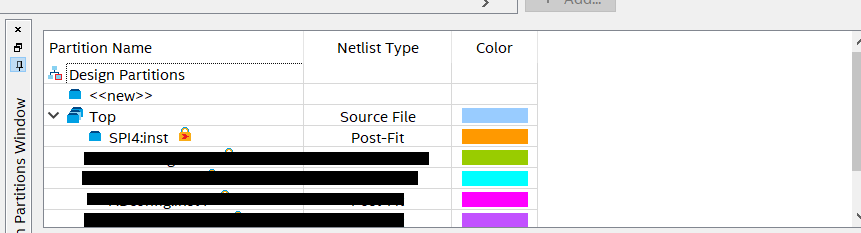

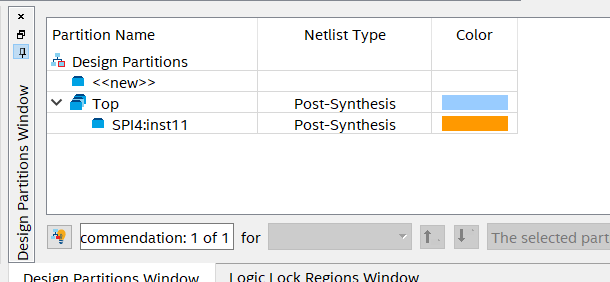

例如对SPI4模块进行约束:(设置完会有一个黄色锁的小标志)

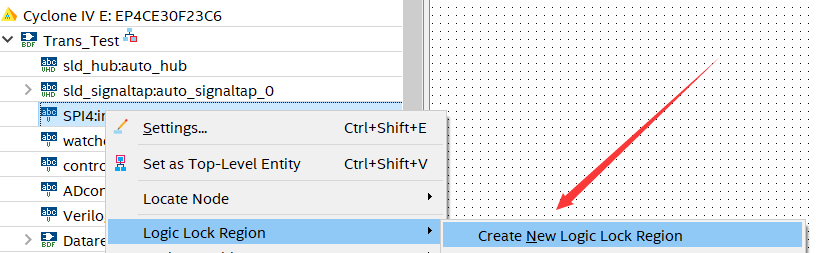

对该模块右键进行新建逻辑锁定区域

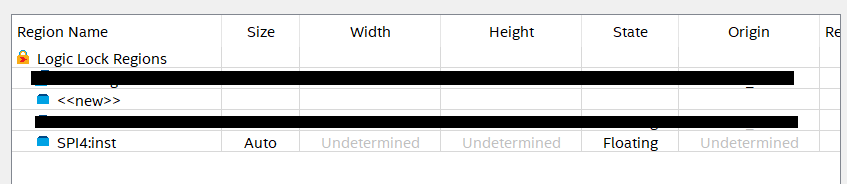

可以看到有锁定区域生成

打开chip planner

对部分区域进行锁定,没有锁定的是红色

下面对设置的参数进行说明:

state:Floating 区域由Quartus 软件自动选择区域合适的大小和位置,Locked区域由用户指定区域的大小和位置。

width:宽度

Height:高度

Reserved:该属性表示是香保留区域内部的逻辑资源,off表示可以使用区域中未被指定的逻辑资源,on表示只有与区域相关联的单元才能被布局布线到该区域

Origin:该属性表示了区域的位置标注

实验测试发现并没有提高编译速度,而且设置太多模块会提醒RAM空间不够,离谱。

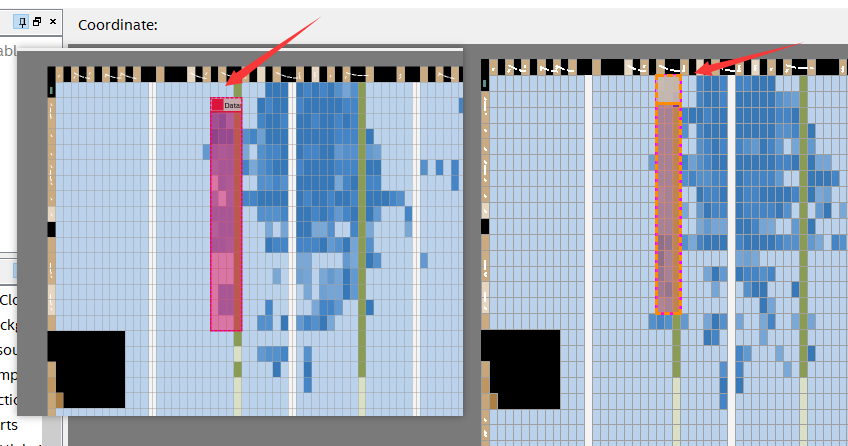

多次测试虽然不能提高编译速度,但是确实能够实现锁定:(下图是未设置锁定)

不要锁定的时候调时序

Design Partition

所以又在网上查找了一些手段:(编译过程)

分析综合、布局布线、汇编、汇编(.sof)、时序分析、生成网表

大部分时间都是分析综合和布局布线占用掉了。

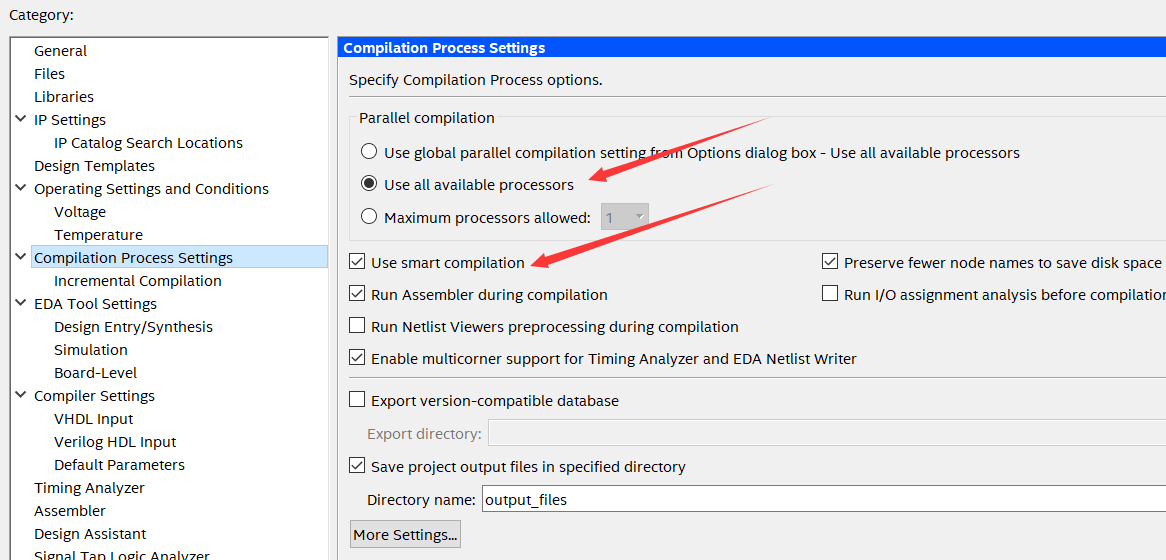

自动增量式编译设置:

1.使用多核处理器(没啥提升效果)2.使用智能编译方式(在没有修改源文件的时候瞬间完成,但没啥用)

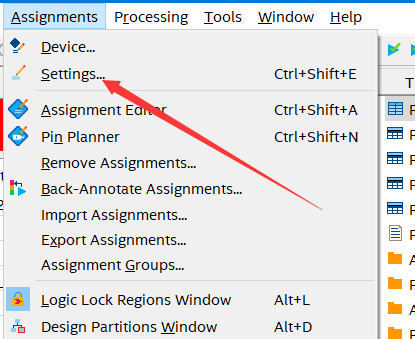

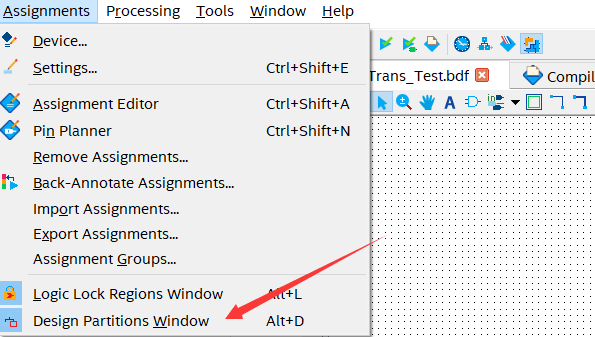

2. Design Partition:设计分区(设置完会有一个蓝色小标志)

Source File:如果源代码未修改,则仅不重新Analysis,还需进行Synthesis和Fitter;

Post-Synthesis:如果源代码未修改,不需重新Analysis、Synthesis,结果只进行Fitter;

Post-Fit:如果源代码未修改,保留前次Analysis、Synthesis、Fitter结果;

Empty:标志为空分区,编译时将忽略此分区。

用户可通过设定A、B分区的属性类型来告诉编译器,哪部分已经不需要重新综合、布局布线了;哪部分已经修改了,需要重新进行综合等等。

一般把没有修改的模块设置为Post-Fit,同时顶层模块也要这样设置,而修改过的模块设定为Source File。

我又试了试,没啥效果,反而编译时间变长了,离谱

最后查到intel官网了:

2.3. 缩短总编译时间的策略

提到了几点方法:

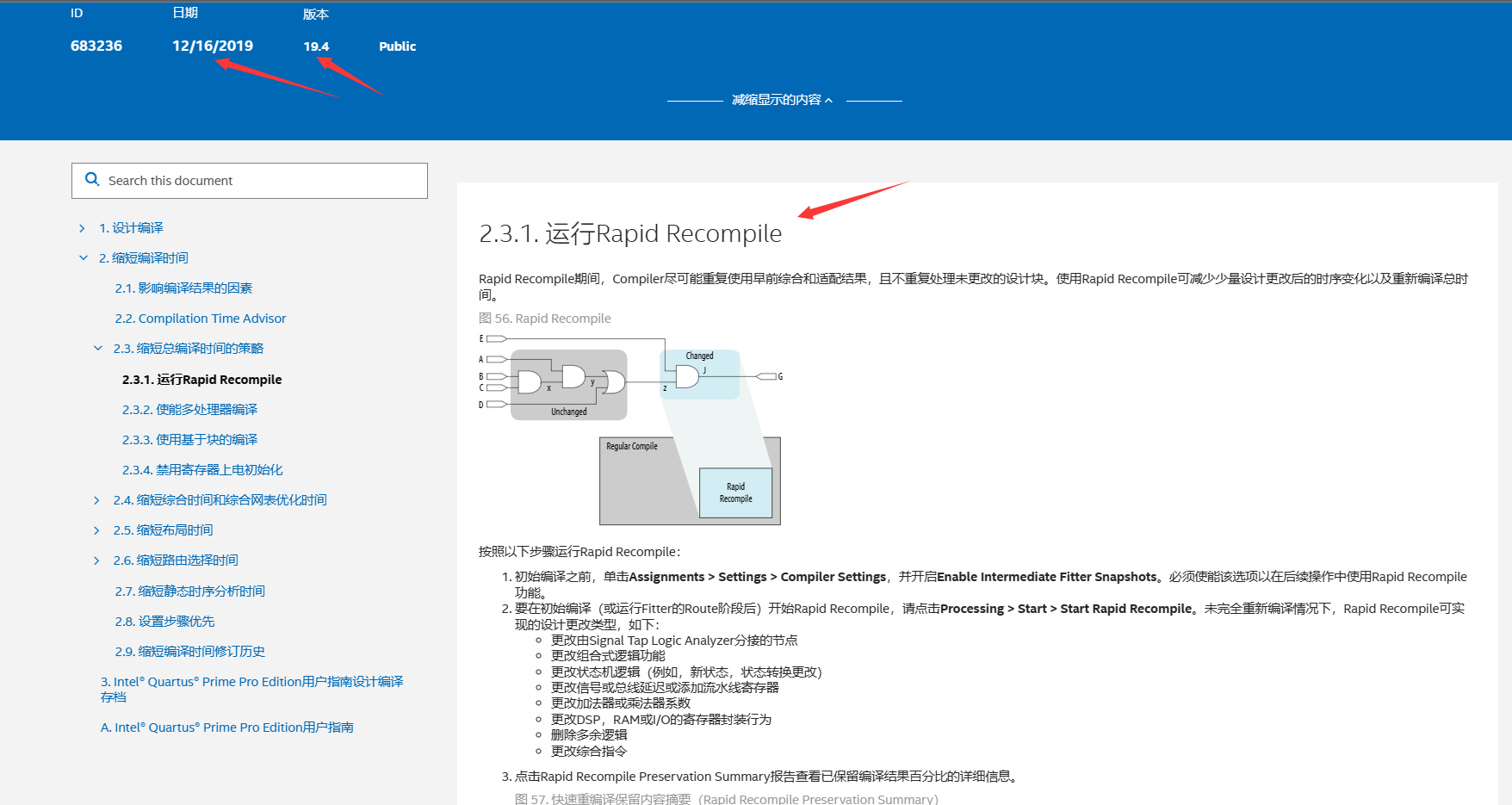

运行Rapid Recompile

使能多处理器编译

使用基于块的编译

禁用寄存器上电初始化

发现有一个rapid recompile模式,但我选EP4CE30F23C6的时候发现不支持:

Error (12750): The currently selected device family does not support Rapid Recompile.

查到是因为: rapid recompile only supported in the following devices: Stratix V, Arria V, Cyclone V,还需要许可正好像,有13年的intel网页说所有设备都禁用了,但是19年却说明了使用方法,但是18.0标准版我没找到

Intel® Quartus® PrimeDesign Software

所有器件系列的快速重新编译功能均已禁用

我推测有可能是因为这个东西禁止了导致Design Partition和LogicLock没加快编译的效果了。

封装用户编写的程序

没学会怎么加速编译,反而学会如何将用户编写的模块进行封装了,就像我们调用系统IP核那样,这样别人看不到我们的程序,但可以拿来使用。

首先,我们之前学会如何set a design partition,在那个基础上进行

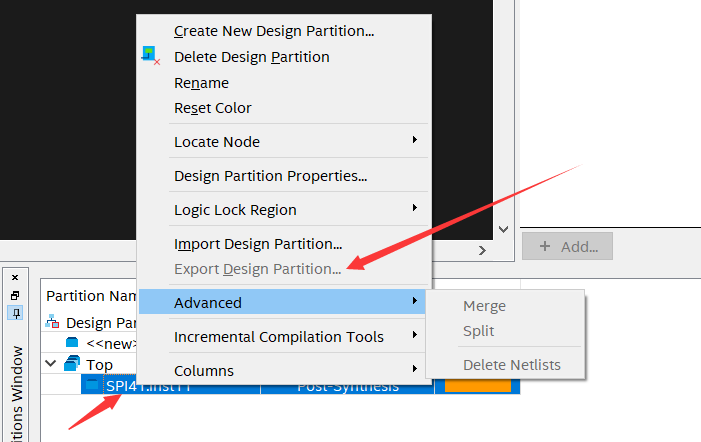

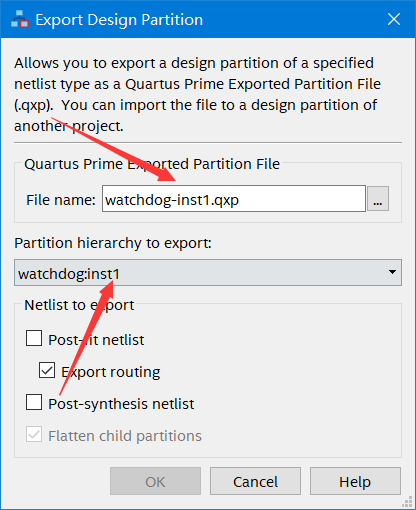

可以直接封装整个顶层,也可以封装一个模块:(对该模块点击鼠标右键,选择Export Design Partition)

这里不可选是因为这个模块里面我已经使用了封装好的用户程序,正常情况在下图设置名字和模块,设置完成后就会生成.qxp文件。

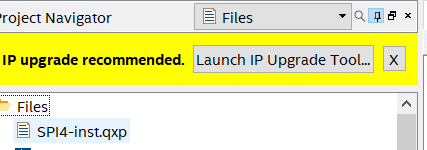

这个时候就可以把.qxp文件发送给别人了,使用的时候很简单,只要将该文件导入项目中,然后设置为顶层或者进行例化后就可以使用了。

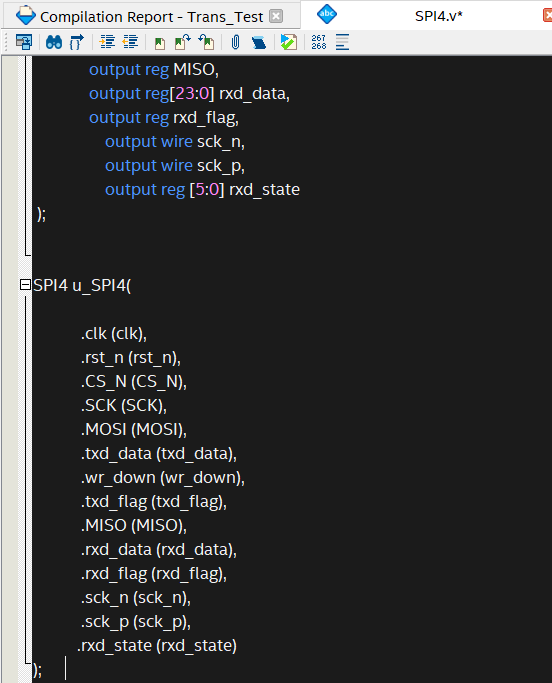

例如:例化一个SPI的程序,这样我看了看编译速度也没加快。

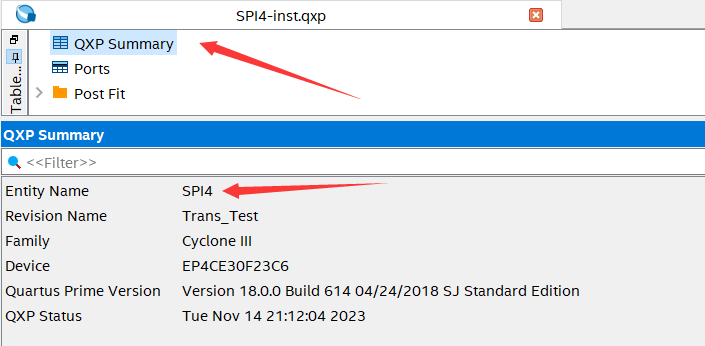

名字:

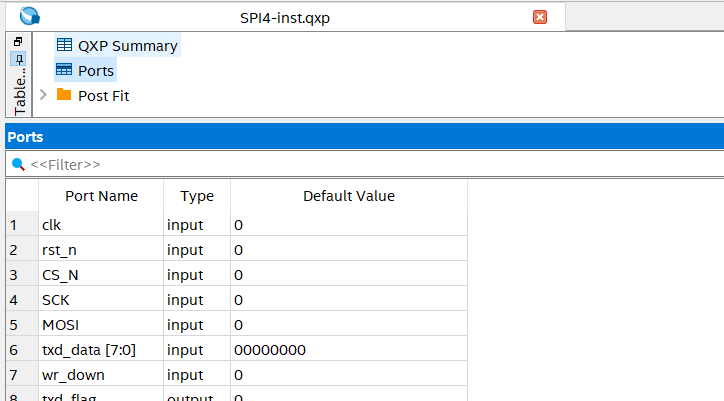

端口信息:

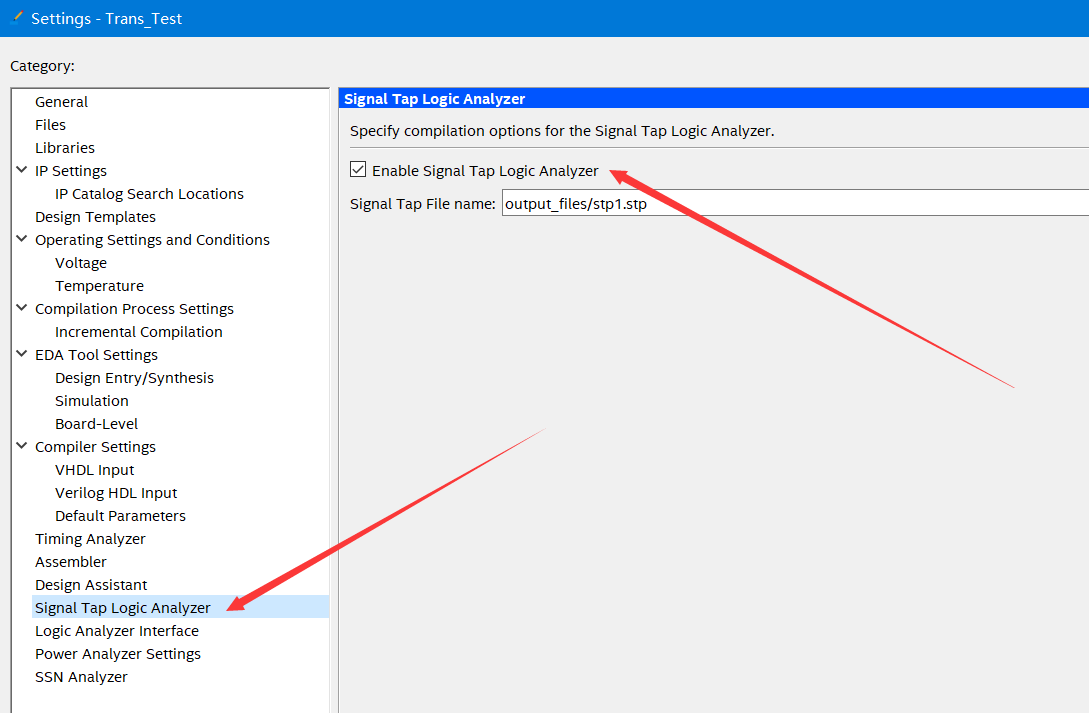

停掉signal tap

这里选择是否加入signal tap编译,占用的资源会减少,会影响综合器布局布线。

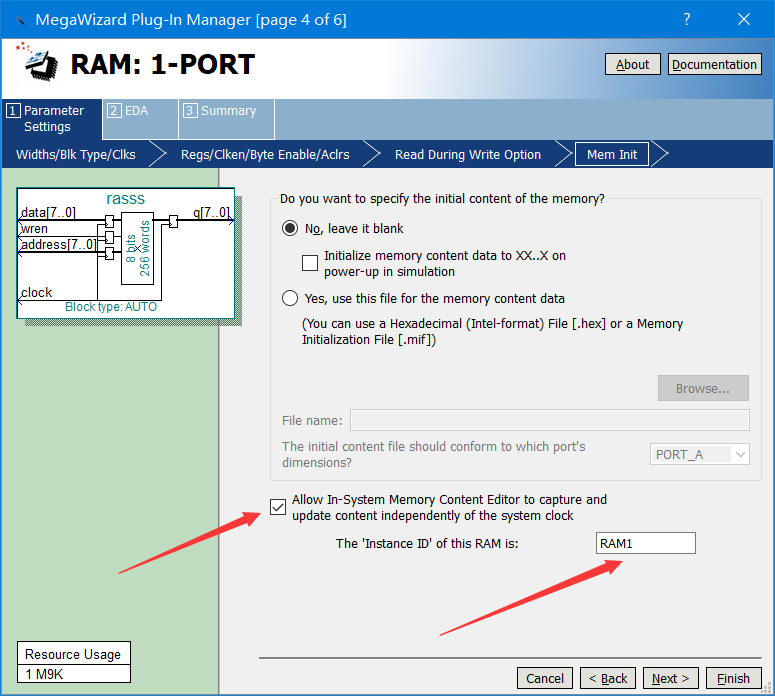

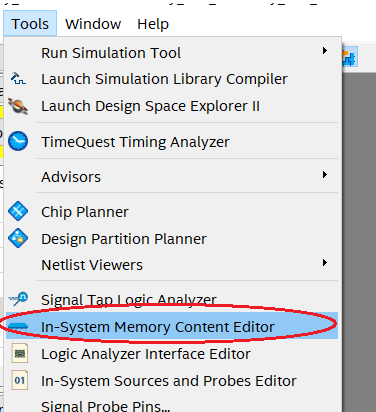

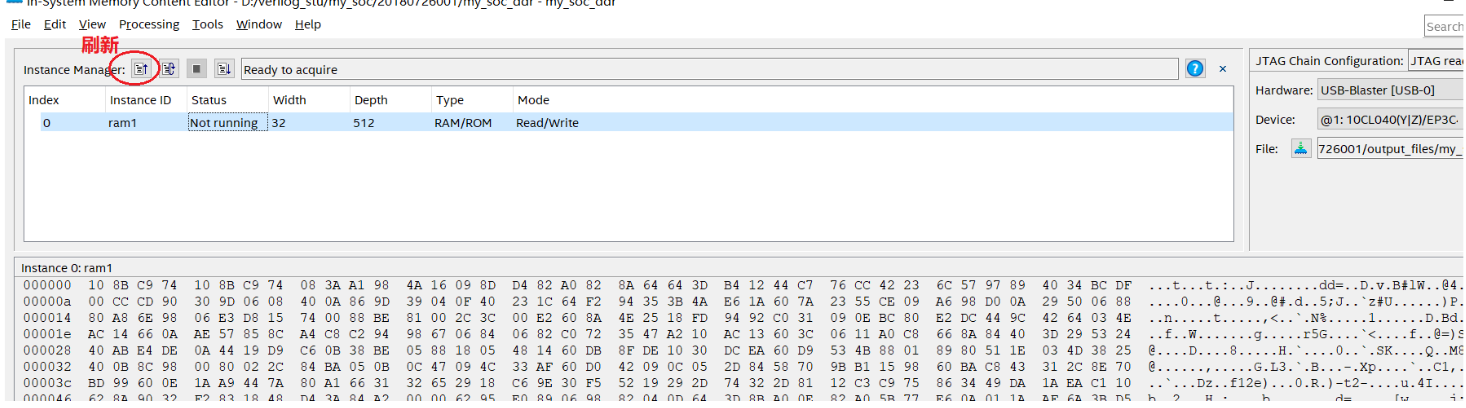

抓取单端口RAM的数据

可以像SIngleTap一样,通过USB Blaster抓取RAM 1_port的数据

勾选命名后,将程序sof下载进去

RAM 2-PORT没有这个功能。

文献2:SRAM约束

参考文献:[1]左丽丽,刘国斌,吴维林等.基于反馈约束的SRAM接口时序分析方法[J].计算机测量与控制,2020,28(01):

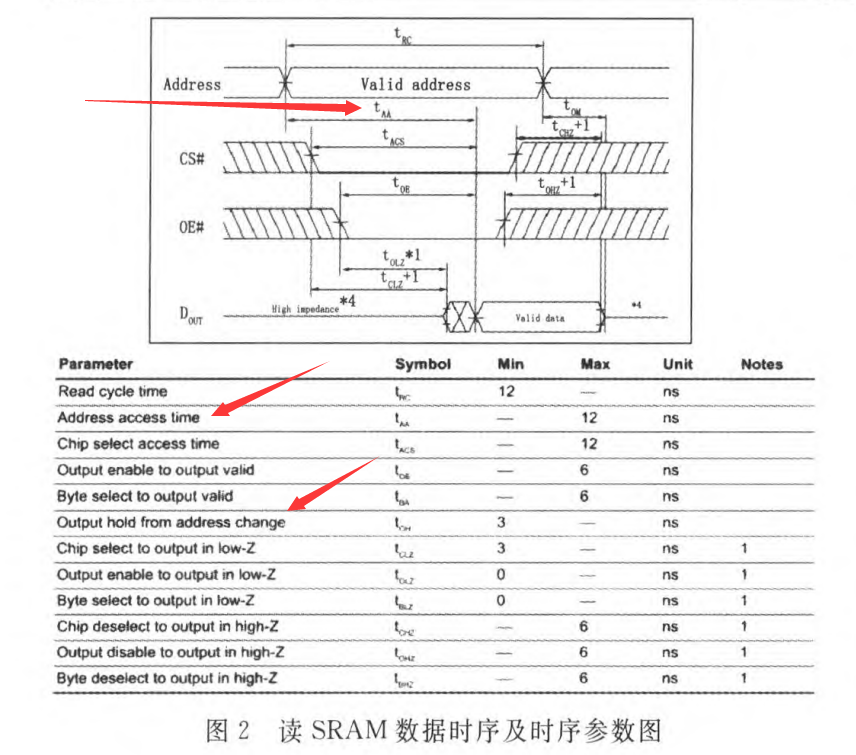

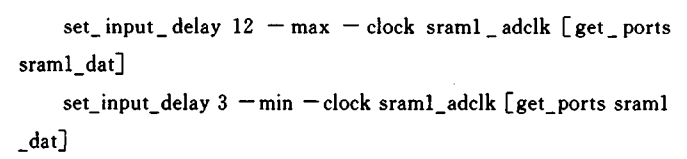

FPGA读取SRAM的数据的时候,采取的是地址驱动数据输出的方式,片选和读使能引脚全部固定使能,因此要对数据和地址进行时序约束。

可以看到数据相对地址延迟最大12ns,最小3ns

589

589

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?