1.编写技巧

- 片选:reg [2 +: 3] a; 表示片选2 ,

等价于 reg [4 : 2 ] a; - reg [7 -: 3] a; 等价于 reg [7 : 5] a;

注意符号和冒号之间不要有间隔。 - 寄存器多打一拍代码编写

代码

always @(posedge sys_clk )begin

if(!rst_n)begin

cek_en_dl1 <= 1'b0;

cek_en_dl0 <= 1'b0;

end

else begin

cek_en_dl1 <= 1'b1;

cek_en_dl0 <= cek_en_dl1 ;

end

end

assign divider_temp_start = cek_en_dl0 ^ cek_en_dl1;

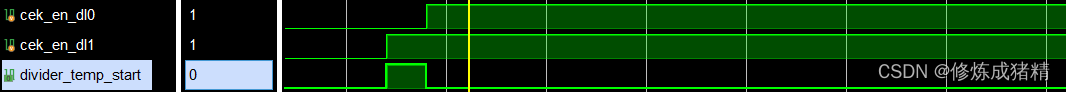

仿真结果

- 数据类型:

wor,表示线或。

tri,三态总线 。tri [7:0] tribus //定义一个8位的三态总线;

2.问题整理

-

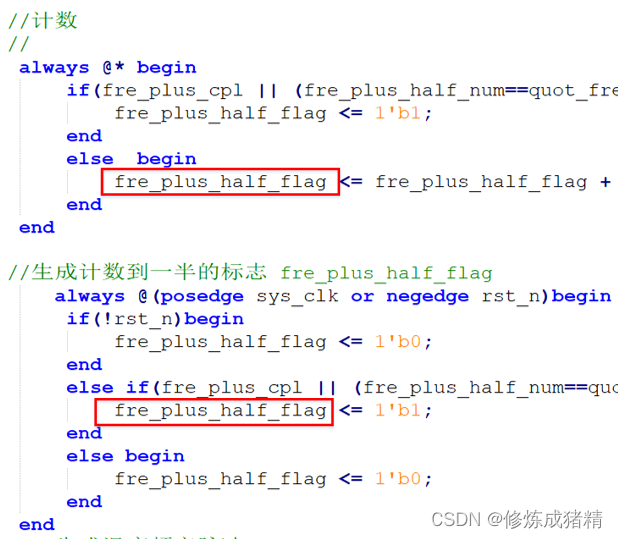

问题1::Iteration limit 10000 is reached. Possible zero delay oscillation detected where simulation time can not advance. Please check your source code. Note that the iteration limit can be changed using switch -maxdeltaid.

: 达到 10000 次迭代极限。可能检测到零延迟振荡,模拟时间无法前进。请检查源代码。请注意,可以使用开关 -maxdeltaid 更改迭代限制。

解决方法

我写的代码如下,错误原因,用两个always 给同一个寄存器赋值,一个寄存器不能多处赋值,删掉一个always就好了。

-

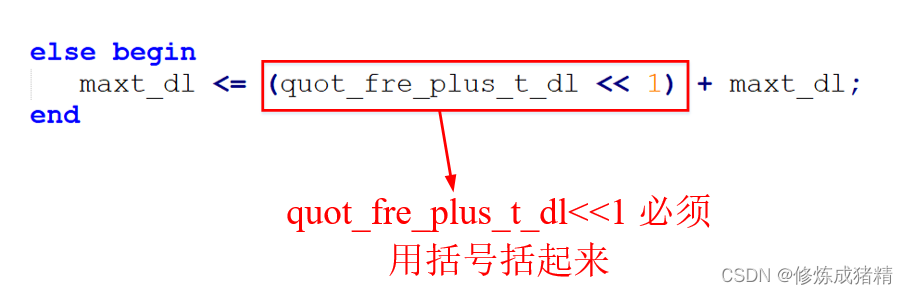

问题2:在写算术的时候记得加括号

正确示范

-

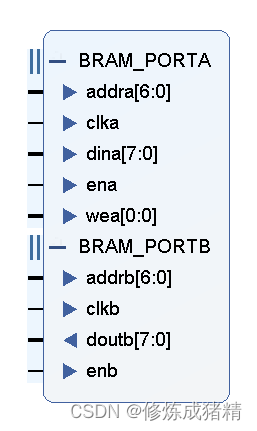

问题3 :简单双口ram 不能读出数据

-

-

解决方法

wea为a端口写入使能信号,必须为’1‘。

注:若dina的位宽为8,doutb的位宽为16,那么doutb输出的数据并不是在高位补零,而是dina按输入顺序存储的拼接数据。

- 问题4:always块里面嵌入if, 不能识别if里的判决条件。

解决方法

是由于代码中的“en”拉高的起始时刻是由“start”决定的(在“start”后面),代码如下,所以“always”块里面的“ if ”判决识别不到。

若是换成" en " 和“start”在同一时刻拉高,便可以实现,如下图所示。

3042

3042

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?