Power分析

在综合时,我们需要做power分析,那么怎么保证综合阶段的power和做完place&route后的netlist的power一致呢?

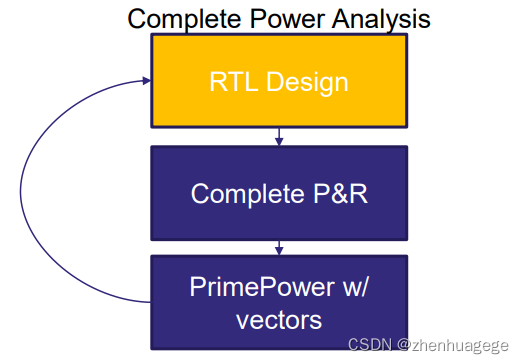

完整的power分析流程,如下图所示

这个流程的特点是:

1、Time-consuming,很耗费时间

2、Multiple iterations,需要多次迭代

3、High maintenance,耗费资源大

4、Very accurate,很精确

这个power分析,要从RTL到PR netlist,往往这需要很长的时间,这样分析power并不实际!

而RTL到netlist的时间往往花的时间较短,迭代时间很快,有没有可能在综合阶段就做好power分析呢?

Fusion Compiler Power Analysis

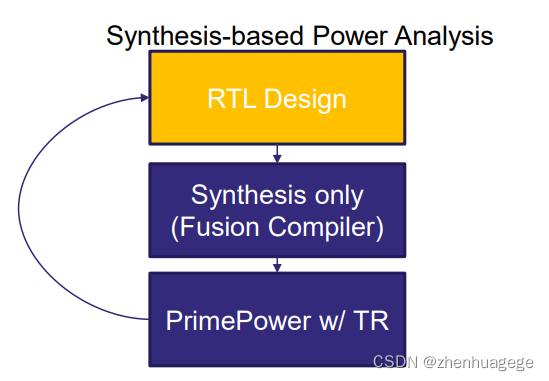

下面介绍fusion compiler的powe 分析flow,如下图

这里我们不再需要做完place&route的netlist,只需要synthesis only的netlist即可,其特点如下:

1、Fast runtimes,节省runtime

2、Quick iterations ,快速迭代

3、Easy to maintain,耗费资源少

4、Not accurate,但是不是很准确

How can we make synthesis-based power analysis accurate?

怎么让综合阶段的power分析更准确呢,这是个问题!

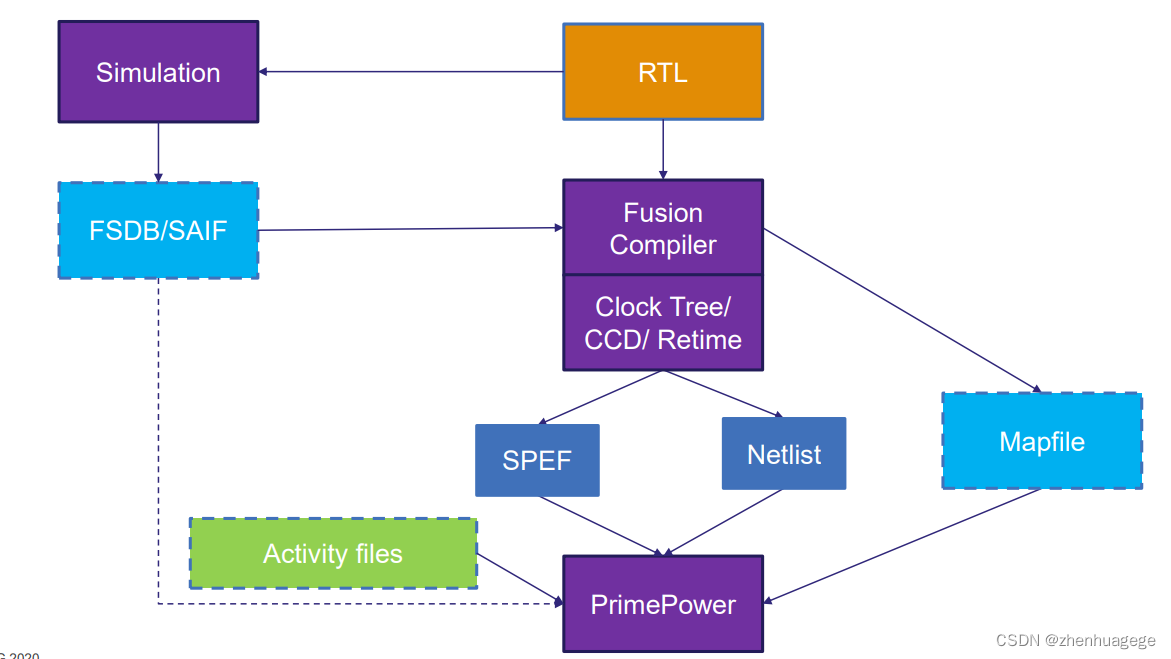

Proposed Methodology

本文探讨了在集成电路设计中,如何在综合阶段进行有效的功率分析,以减少与Place & Route后的功率不一致。传统的功率分析流程耗时、迭代多且维护成本高,但精度高。FusionCompiler提供了一种更快的综合阶段功率分析方法,虽然不那么精确,但能大幅减少运行时间和资源消耗。为提高综合阶段功率分析的准确性,文章提出了新的方法论。

本文探讨了在集成电路设计中,如何在综合阶段进行有效的功率分析,以减少与Place & Route后的功率不一致。传统的功率分析流程耗时、迭代多且维护成本高,但精度高。FusionCompiler提供了一种更快的综合阶段功率分析方法,虽然不那么精确,但能大幅减少运行时间和资源消耗。为提高综合阶段功率分析的准确性,文章提出了新的方法论。

2262

2262

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?