Double pattern technology

什么是double pattern technology?

首先要了解一下mask的概念,什么是mask?

Mask

mask就是掩模,通过刻蚀后,在掩模上留下了金属线的走线图形,把mask放于metal layer上,让光线透过mask,mask上有走线的部分不透光,这样在metal layer上形成了金属走线;

通常情况下,一层metal只需要一张mask;

但是在20nm以下的工艺中,如果只使用一张mask,并且mask上相邻的metal wire之间的间距过小,使得相邻的光线间距过小****(最小间距),光线相互之间发生干涉,最终导致metal wire的边缘模糊,出现瑕疵;

另外一个解释(转载):

因为在先进工艺节点下,光刻的分辨率也是有一定极限的,比如互相平行的两段金属线,他们之间的间距必须大于10纳米才可以被刻出来,但是我们在其他刻蚀步骤时可以支持到比如3纳米,如果全部都按照10纳米的间距来制造,就会有一定的面积被浪费掉;

也就是说,刻蚀机是可以刻蚀处3nm的mask的,但是光刻并不能直接光刻出来3nm的,如果两条金属走线的间距是3nm,我们的光刻机只支持10nm,这样就无法光刻处我们想要的走线;

因此人们想了个办法,我们可以同时制作两个mask,两个mask互相偏移5nm,而每个mask还是按10nm的规则来做。这样的话,我们就可以在第0nm、第10nm、第20nm的位置用mask1来刻金属线,而在第5nm、第15nm、第25nm的位置用mask2来刻金属线。这样子,最终的结果就是我们可以得到间距最小为5nm的金属层,比只用一个mask足足省下了一半的面积,这就能省下更多成本

————————————————

版权声明:本文为CSDN博主「伟酱的芯片后端之路」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/weixin_52636726/article/details/122012056

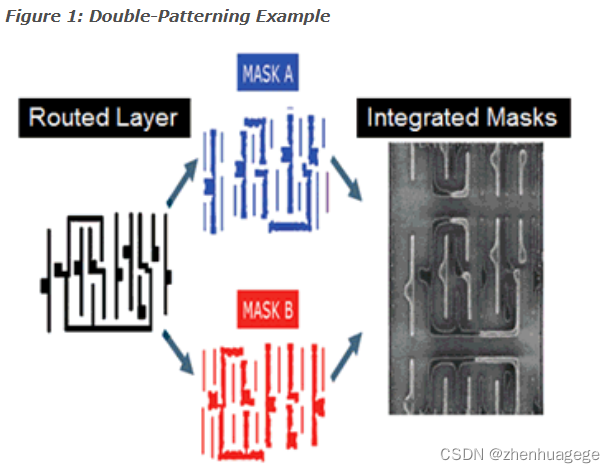

double pattern

为了解决这个问题,先进工艺下,开始采用DPT,也称为double mask,就是将原来的一层mask拆分为两个mask,在每一个mask上都不会出现最小间距问题,就避免了metal wire的瑕疵问题,其代价就是成本增加,原来只需要一层光罩的费用,现在需要双倍费用;

首先看下图

那么,一层mask一定可以分为两层吗,会不会遇到无法拆分的情况?

如果遇到无法拆分的情况,就会报odd cycle drc的问题!

odd cycle violation

顾名思义,odd cycle指的就是奇数环,如下图所示

如上图所示,一共有5个wire(A、B、C、D、E),并且出现个5个wire之间间距小于DPT规定的最小间距的情况,因为是奇数个,就会出现无法拆分成两个mask的情况;

例如,我们将其拆分为:A、D一组,B、C、E一组,这样拆分后,B和C之间的间距还是小于DPT规定的最小间距;

有人说,拆分为:ACE一组,BD一组不就好了,但是这样还是不行的,应为AE之间的间距也是小于DPT规定的最小间距的;

怎么解决?

很简单,拉开spacing即可,如下图所示

拉开B和C之间的间距之后,使其大于DPT规定的最小间距,可以拆分为AD和BCE两组。实现拆分;

怎么判断odd cycle?

工具是怎么判断是否存在odd cycle drc问题的呢?

答:

工具随机选取一根metal并作为第一根,如果第一个和第二个metal之间的间距小于最小间距,如果小于的话,就要接着检查第三根和第二根metal之间的最小间距,如果还是小于的话,就去找第四根metal,并比较第三个和第四个metal之间的间距是否小于最小间距,如果还是小于,就接着继续寻找…,再找到第N个metal后,如果第N个metal和第一个metal的间距小于最小间距,这样就形成了一个闭合环路,此时,如果N是奇数,就会出现odd cycle drc问题;

工具会找出这些最小间距环,然后检查是否为奇数,如果检测到话,工具会去fix;

哪层metal要做DPT?

通常情况下,DPT一般用于底层metal,比如M2、M3,因为先进工艺cell出pin更密集,需要更多的底层绕线资源,底层metal更适合连接cell pin;

另外,底层metal的绕线利用率不宜太高,一般设定在60%左右,因为密度越大,出现odd cycle的几率越高;

DPT的最小spacing可以在tech file中查到,比如某厂商的10nm工艺中,M2是DPT layer,规定了DPTminSpacing为0.072um!

同一层的一个wire尽量不要出现拐弯,这意味着这个wire要占据两个track,容易导致odd cycle!

RC Corner

下面是在其他文章上看到的DPT和RC corner之间关系的Summary;

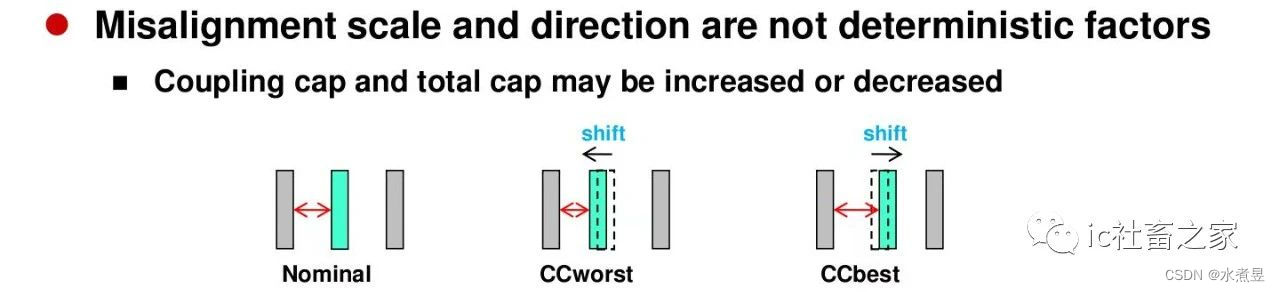

在14nm以下的工艺中,RC corner变得复杂了,而其中一部分和DPT有关,如下图所示

如上图所示,两次曝光不一定那么准确,相近的耦合电容增加,相远的耦合电容降低,那么RC Corner就变为:

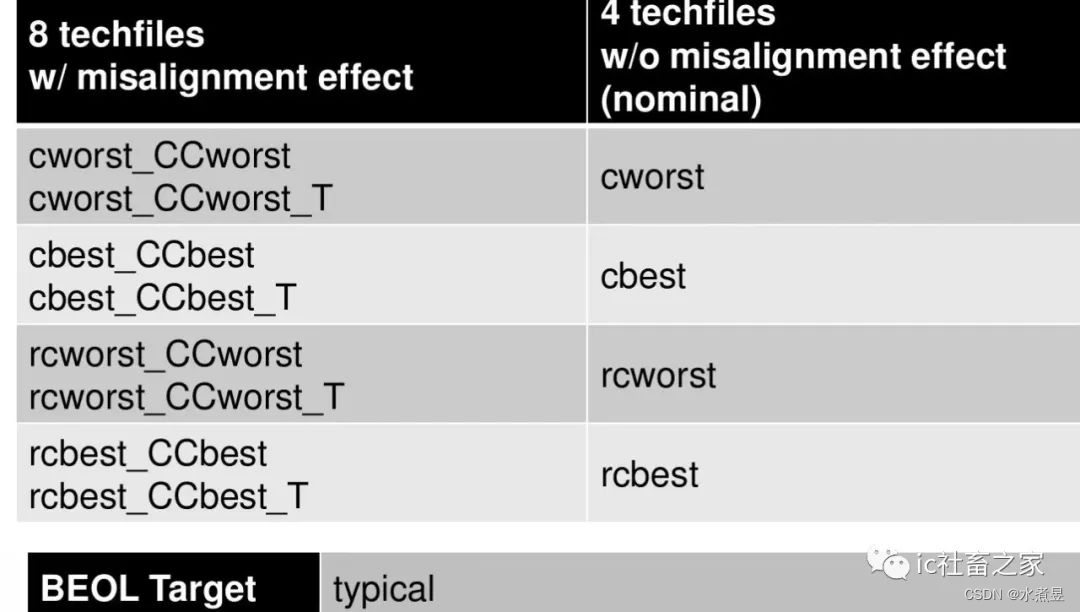

ccbest和ccworst是在RC corner基础上,更悲观了一点;那么_T是什么意思?

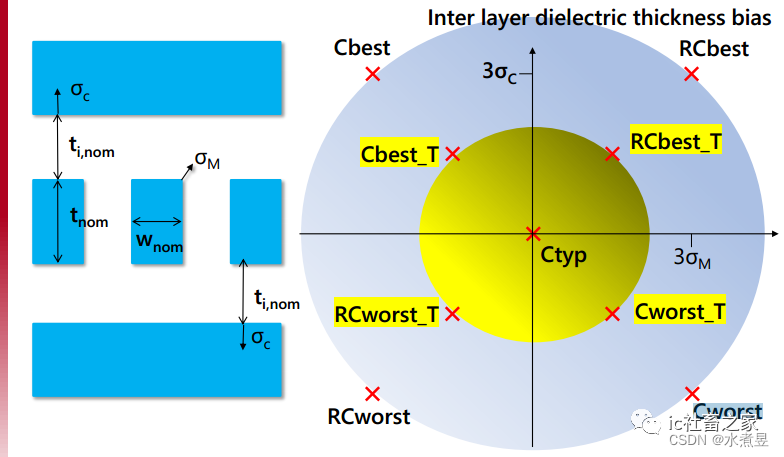

首先看下图

图中,Tnom是“通常”的金属厚度,Wnom是“通常”的金属宽度,Ti,nom应该是“通常”的金属间距。σM我理解是金属厚度和宽度的“变量”(和normal相比),σc我理解是金属间距和厚度影响到的电容的“变量”。图中,带_T的部分是1.5σ(sigma),不带的是3σ;

由于,考虑coupling capacitance的RC corner比不考虑的更悲观。因此,我们在DCT中设置tluplus的时候,max和min都有了定论。即max考虑耦合电容,min不考虑。

1265

1265

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?