目录

1、Architecture

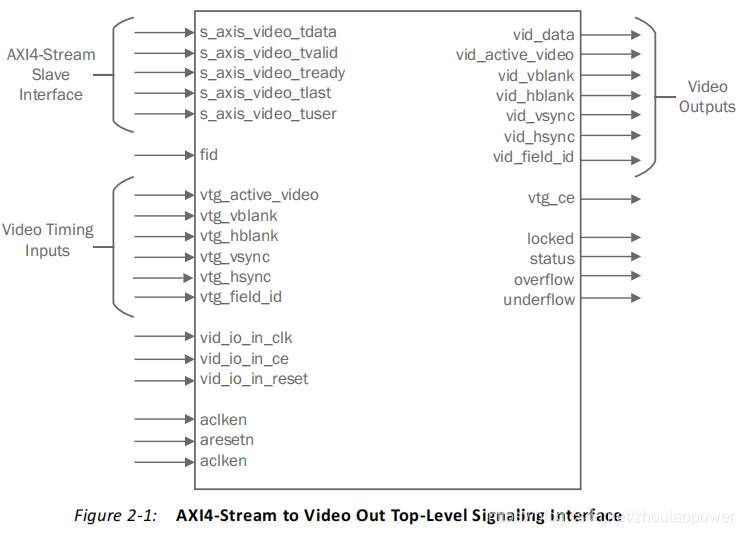

前面介绍了《Zynq-PS-SDK(9) 之 VDMA》和《Zynq-PS-SDK(10) 之 VTC》,数据流和时序流;从 VDMA 出来的是 AXI-Stream 流式数据,从 VTC 出来的是像素时钟得到的 Hsync,Vsync,Hbank,Vbank等时序信号,而我们最后对应到 HDMI 的是像素和时序一起的信号,所以这里需要一个将 AXI-Stream 流式数据和 Timing 信号转为一组同步的像素+Timing信号的 IP Core,Xilinx 提供了一个叫做 AXI4-Stream To Video Out 的软核:

下面是 AXI4-Stream Video Out 的内部结构:

我分别使用不同颜色进行了标记,接下来我们围绕这个结构来进行分析如何使用这个 IP;

从左到右,自上而下进行分析:

1、AXI4-Stream To Video Out 第一个输入为深红色的 AXI4-Stream 数据流,我标记红色的两个通道第一个为 s_axis_tvalid 和 s_axis_tready;他们用于 AXI4-Stream 和 AXI4-Stream To Video Out 的握手信号,能够起到流控作用;

2、蓝色方框内,称之为 Stream Coupler,它左边接受来自 AXI4-Stream 的图像数据,将数据存储到 ASync FIFO 中,右边将缓存的数据输入到下方黄色的同步单元;异步 FIFO 的使用,主要是因为可能输入的 AXI-4 Stream 速率可能和图像的输出速率不一致,双方时钟不同步,所以,这里可以看到,这个 ASync FIFO 的 full 信号,接到了 AXI4-Stream 的s_axis_tready 上,就是为了流控;

3、左下方的红色为 Video Clock,像素时钟,它给到 4 个模块:VTC、Output Synchronizer、Data Formatter、Async FIFO;

4、黄色的 Output Synchronizer 作为同步模块,接收来自 ASync FIFO 的数据和 SOF(Start Of Frame)、EOL(End Of Line)以及 VTC 的时序信号,同步锁定后,生成 Locked 信号;

5、Output Synchronizer 的 Locked 信号作用到绿色的 Data Formatter 模块,Data Formatter 的信号输出由 Locked 信号作为 Mux 选择信号;

官方针对数据吞吐量有一个说明:

Throughput:

The average data rates of active pixels on the Video output bus matches the average rate of active pixels in on the AXI4-Stream bus. The data throughput is dictated by the video line standard and clock rate. However, the clock rates of the input need not match the output.

Furthermore, since the AXI4-Stream bus does not carry blank pixels, the clock rate can be lower than the video clock rate and still have sufficient bandwidth to meet the average rate requirement. Additional FIFO depth is required in order to smooth the mismatch in instantaneous rates.

Both the AXI4-Stream Clock (Faclk) and the rate of the AXI4-Stream Clock (Faclk) is limited by the overall Fmax.

我简单的翻译一下,就是:

1、输出的视频(或者说是图像)的速率是由视频相关的标准规定的,比如你 RGB888 1080p 60Hz 的分辨率,其实是可以计算出你需要的带宽的,所以在输出端的带宽是可以计算出来的,并且一定是遵循了视频标准的;

2、输入的 AXI4-Stream 数据速率没必要和输出的视频速率匹配(因为是可以支持到异步 FIFO),但是为了视频输出正常,最好是输入速率不能够太低,否则无法满足正常的视频帧的输出;

3、输入的 AXI4-Stream 速率可以比像素时钟稍微小一些,因为随着像素时钟输出的视频数据,存在消隐区,也就是说,随着像素时钟输出的并不是 100% 的显示数据,但是随着 AXI4-Stream 输入的数据,是 100% 的有效显示数据;

4、为了满足正常显示并合理的数据率(比如 1080p 60Hz),输出端速度已定,输入端需要足够的带宽,所以 AXI4-Stream 的数据率不能够太低;

2、Signals

这个 AXI4-Stream To Video Out 模块的输入输出如下:

这里的描述不再多说,已经非常清晰了,针对几个点,多说几句:

|

Signal Name

|

Direction

|

Width

|

Description

|

| s_axis_video_tvalid | Input | 1 | AXI4-Stream TVALID,Active video data enable |

| s_axis_video_tuser | Input | 1 | AXI4-Stream TUSER. Start Of Frame |

| s_axis_video_tlast | Input | 1 | AXI4-Stream TLAST. End Of Line |

| s_axis_video_tready | Output | 1 | AXI4-Stream TREADY. Inverted FIFO full |

| s_axis_video_tdata | Input | N | AXI4-Stream Data |

可以看到,s_axis_video_tvalid 和 s_axis_video_tready 用于交互握手和流控;

s_axis_video_tuser 用于代表一行视频帧数据的开始,即 SOF;

s_axis_video_tlast 用于代表一行视频帧的结尾,即 EOL;

s_axis_video_tdata 是实际的视频数据,必须是 8bits 的倍数;对于非 8bits 倍数的,需要在 MSB 上使用 0 来补齐;

说明:

在 AXI4-Stream 协议中,USER 信号的含义是自定义,在视频通路搭建中,s_axis_video_tuser 信号用作了 SOF 信号;

SOF 针对的是一帧数据的开始;

EOL 针对的是图像每一行的末尾;

3、Timings

针对 SOF 和 EOL 的信号的一个例子如下:

T0:ACLK 上升沿检测到 EOL,说明某一帧的某一行完毕,Pn-1 是该行的最后一个数据;

T1:ACLK 上升沿检测到 VALID 和 READY 握手有效,开始传输该帧的下一行的第一个数据 P0;

T2:ACLK 上升沿检测到 EOL,说明该帧的某一行结束;

T3:ACLK 上升沿检测到 VALID 和 READY 握手有效,并且 SOF 有效,说这是下一帧的第一行数据;

T4:ACLK 上升沿检测到 VALID 和 READY 握手有效,并且 EOL 有效,说明这是这一帧第一行的最后一个数据;

4、General Design Guidelines

AXI4 Stream to Video Out 这个 IP 需要连接的是 Video Sink,也就是设备端,比如显示器等;典型的设计是,增加一个 Video Timing Controller 来提供时序,如下所示:

红色部分就是我们今天的重点:AXI4 Stream to Video Out,它接收来自左边 source 的 AXI4 Stream 数据,同时接收来自左下角的 Video Timing Controller(配置成为 generator)的时序,自生输出右边的信号;

在我们的设计中,这个 Source 后面会被设计成为 VDMA 的 AXI4 Stream 输出信号;

这里需要注意的一点是,这个时钟信号(紫色)连接到了 Source 和 AXI4 Stream to Video Out;

这个还有一个 Timing mode 的概念,可以配置为 Master 或者 Slave:

Timing Mode 的 Slave mode 是指 VTC 是时序的 Slave,由 Video Out 模块通过 clock enable 控制时序的输出。Master Mode 指 VTC 是时序的 master,不由 Video Out 控制;

参考文献:

http://xilinx.eetrend.com/d6-xilinx/blog/2018-04/12794.html

4564

4564

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?