近日收到一个网友的提问,在这里粗浅表达一下见解:

“网传固态硬盘断电后数据只能放一年,一年之后就会损坏。但是我有一个固态硬盘已经放了五六年了(上次通电还是在2018年左右,我读初中的时候),锁在柜子里一直没动过,今天偶然想起来就翻出来插上电脑看了看,发现里面的文件都还在(试了几个文件,都未损坏)。这是为什么?那个固态硬盘数据能放一年的说法是真是假呢?”

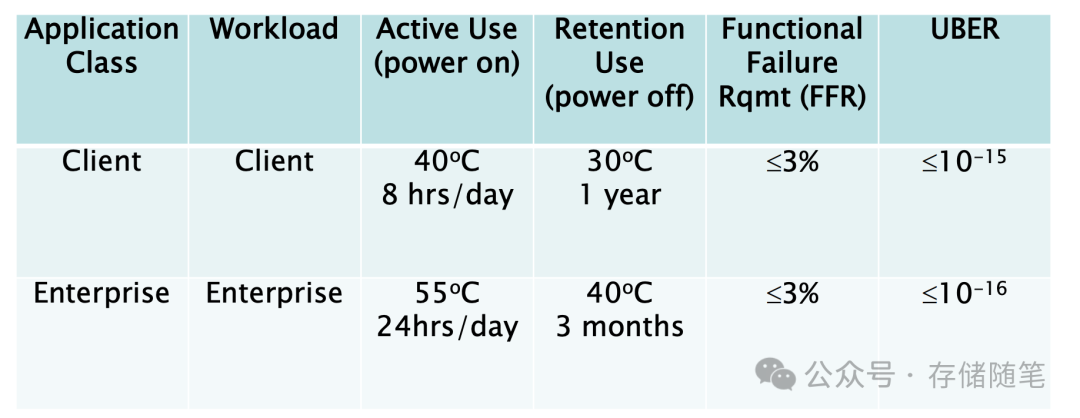

首先,强调下在JEDEC规范中,的确有断电数据保持的时间要求:

-

消费级SSD要求在30度环境断电保持1年

-

企业级SSD要求在40度环境断电保持3个月

这里需要注意的是,这个要求都是基于SSD寿命磨损末期的条件。如果是新盘写了数据,断电保存,理论上比这个时间要长很多。厂商虽然不会在产品手册里明确写新盘断电数据保持时间,根据小编的经验,对于大品牌的SSD,通常3-5年不成问题。

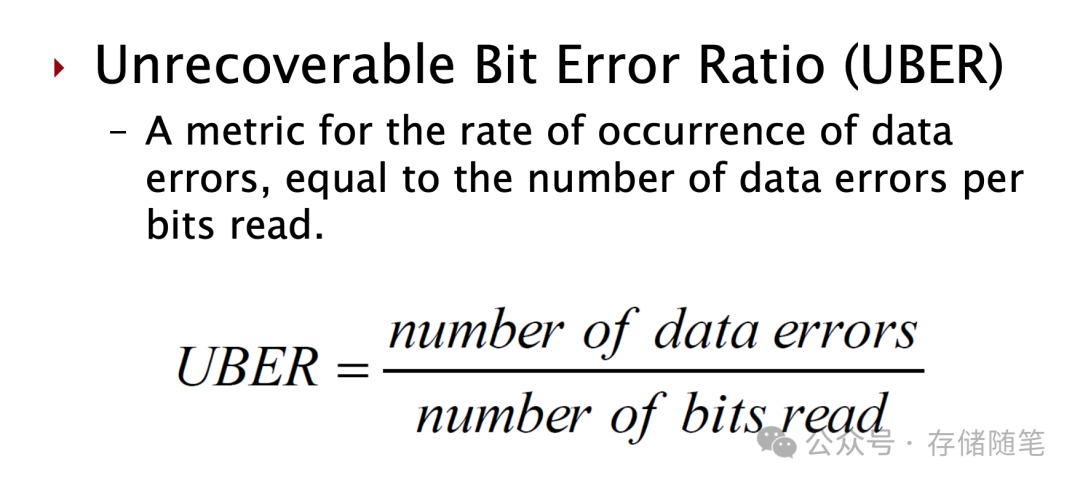

如果文件损坏,常见可能是发生了Media Error,这就得先了解下JEDEC规范中对UBER的定义。SSD UBER(Uncorrectable Bit Error Rate)是指固态硬盘(SSD)在应用了任意特定的错误纠正机制后依然产生的每比特读取的数据错误数量占总读取数量的比例。

SSD UBER是描述SSD硬盘的一项重要参数,用于衡量SSD的稳定性和可靠性。它反映了SSD在读取过程中出现不可修复的数据错误的概率,即SSD的读取错误率。企业级SSD的UBER要比消费级UEBR高一个量级。目前厂家基本都可以做到10^-17甚至更高,部分SSD产品可以到10^-19.

在实际应用中,SSD UBER的数值越低,表示SSD的稳定性越高,数据读取的可靠性也越好。因此,对于需要高稳定性和高可靠性的应用场景,选择SSD UBER较低的SSD硬盘是更为可靠的选择。

发生Media Error不可修复的错误,在SSD产品中是非常常见的故障。不可避免会出现media error坏块,不能要求SSD不出错,重要数据一定要记得有数据备份!重要数据一定要记得有数据备份!重要数据一定要记得有数据备份!

NAND介质Media error产生,通常是跟Read disturb(读干扰),Program disturb(写干扰),P/E Endurance以及Data Retention有关,我们可以简单介绍下机理。

本文主要以SLC/MLC/TLC基础入手,从基本原理解释NAND的一些可靠性问题,万变不离其宗。

第一幕:NAND基础背景

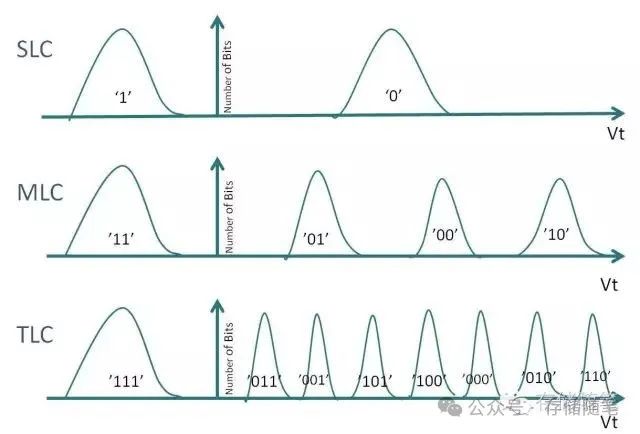

NAND根据cell包含bit的数目分为SLC、MLC、TLC,

NAND里面所有cell的状态采用VT分布图展示,如下图,

SLC包含1 bit,有1,0两个状态,

MLC包含2 bit,有11,10,00,01四个状态,

TLC包含3 bit,有111,011,001,101,100,000,010,110八个状态。

注:横坐标:NAND cell的阈值电压Vt; 纵坐标:每一个Vt对应的bit数目。

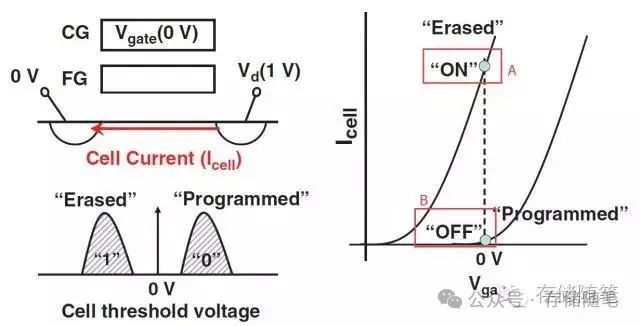

介绍完NAND cell的状态,再来show一下NAND的基本操作(以最简单的SLC为例)。

读(Read):

如上图所示,这是对单一cell进行read的基本操作。在控制栅极(CG, 也是WL)加上0V的电压,源极(Source)端加上0V以及漏极(Drain, 也是BL)加上1V,然后通过源极与漏极之间电流Icell的大小来判断cell的状态(0或者1)。

A点的状态代表存在Icell,所以Cell处于“开态”(ON),称为Erased;

B点的状态代表不存在Icell或者Icell很小且可忽略,所以Cell处于“关态”(OFF),称为Programmed。

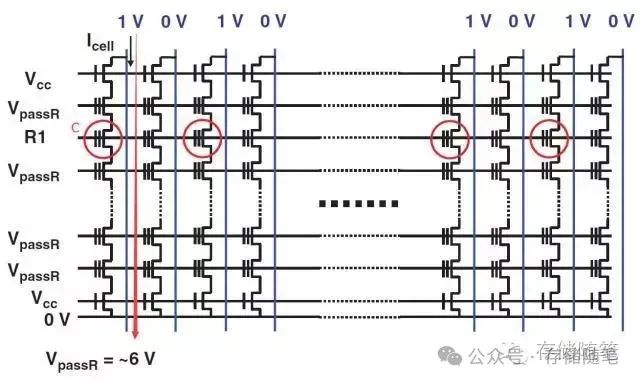

如果对NAND cell阵列操作,原理图如下:

在需要read的target Page的WL上面加一个R1(一个较小的电压),其他WL的加VpassR, BL方向加1V,

如果Cell C处于Erased, 对应BL的Sense电路会感应到有电流;

如果Cell C处于Programmed, 对应BL的Sense电路不会感应到有电流。

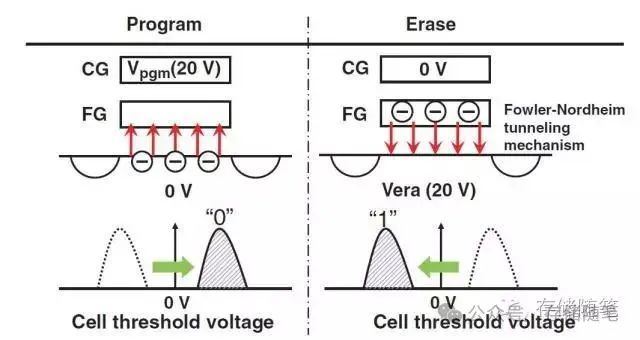

写(Program):

在控制栅CG加上一个高压20V,基底接0V, 由于电场的存在以及隧穿效应,电子会被俘获在浮栅FG,也就完成了单个Cell的Program操作。

Program之后cell的状态为“0”。

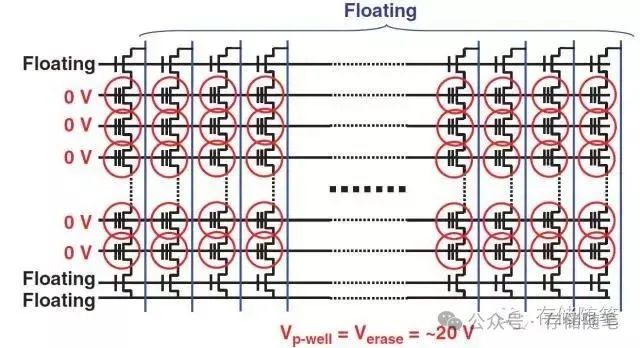

擦除(Erase):

在控制栅CG接0V,基底加上一个高压20V, 由于电场的存在以及隧穿效应,电子逃离浮栅FG,也就完成了单个Cell的Erase操作。

Erase之后cell的状态为“1”。

需要注意的是,Read、Program都是以Page为最小基本操作单位,而Erase以Block为最小基本操作单位。

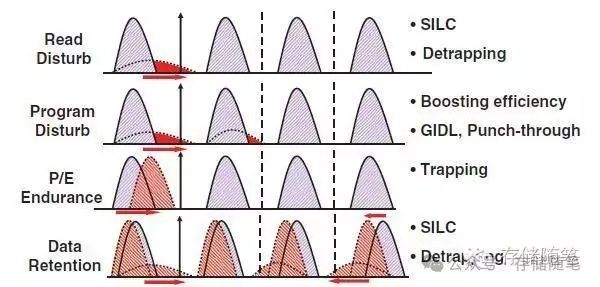

对NAND可靠性影响很大的效应主要有:Read disturb,Program disturb,P/E Endurance以及Data Retention。

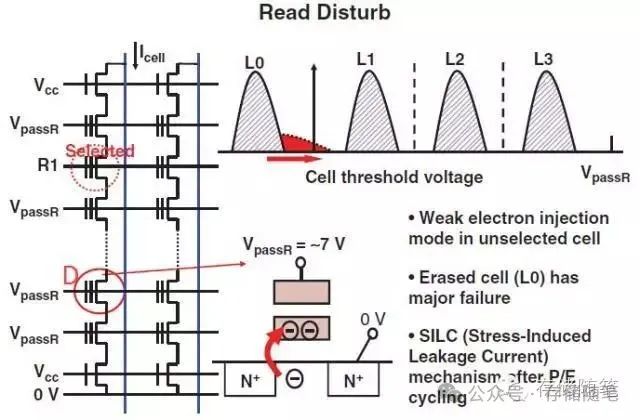

1. Read Disturb

我们在第一幕介绍Read操作的时候提到,Read过程中,需要在Non-Target WL上加一个VpassR, 如果对一个Block里面的Page连续Read很多次的话,就相当于在某一WL一直会有VpassR的Stress。

如下图,Cell D 由于VpassR长时间的Stress, 会引起浮栅FG弱的电子注入,因为Read disturb主要影响Erased状态的cell,进而表现在Vt图中L0向右飘移。

在SSD中,针对Read disturb有优化措施,就是尽量避免持续读同一Block的Page,如果在进行了长时间的读操作之后,会加入Erase/Program操作,减小Read stress。

提一下SILC效应:

SILC(Stress Induced Leakage Current)是压力诱导漏电流,由于Stress的影响,在Gate氧化层做成缺陷,缺陷会俘获电子。

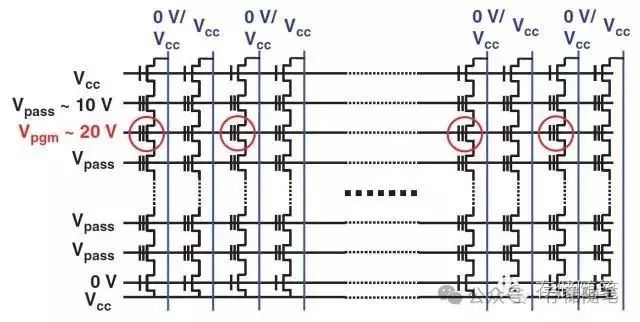

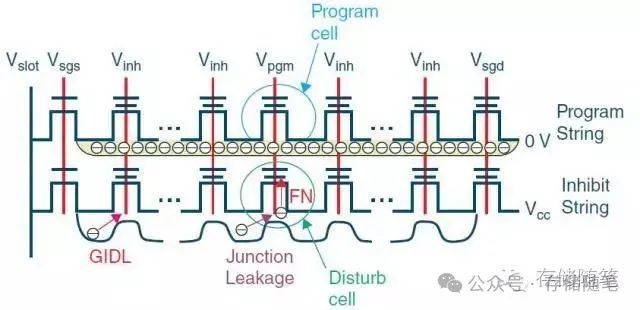

2. Program Disturb

在Program时,需要在WL加一个高压20V左右,由于高压的存在会造成其他BL上电子隧穿进入浮栅,再加上由于缺陷引起漏电以及GIDL效应的存在,最后的结果就是Program cell周围的Cell的Vt会向右偏移。

这里简单说一下GIDL效应:

GIDL(gated-induce drain leakage) 是指栅诱导漏极泄漏电流,当栅漏交叠区处栅漏电压 VDG很大时,交叠区界面附近硅中电子在价带和导带之间发生带带隧穿形成电流,我们把这种电流称之为 GIDL 隧穿电流。随着栅氧化层越来越薄,GIDL 隧穿电流急剧增加。

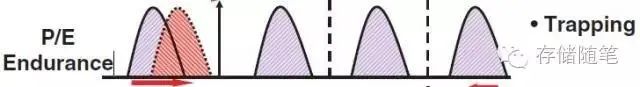

3. P/E Endurance

评判一颗NAND的寿命,P/E cycle是一个关键参数。在不断写入与擦除的过程中,器件的氧化层会慢慢变薄,电子的隧穿效应会更容易,最后造成的现象就是VT向右偏移。

4. Data Retention

在NAND经历一段高温测试之后,电子会逃离浮栅,造成Vt向左偏移。在加上SILC的影响,Vt出现偏移。

总结一下这几种效应的VT分布图,如下:

NAND技术扩展阅读:

如果真的发生了盘的故障,也可以尝试修复:SSD数据错误如何修复?

如果您看完有所受益,欢迎点击文章底部左下角“关注”并点击“分享”、“在看”,非常感谢!

精彩推荐:

2161

2161

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?