Verilog刷题记录02

文章目录

一、基础门

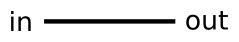

1. 导线(Wire)

module top_module (

input in,

output out);

assign out = in;

endmodule

2. 接地(GND)

module top_module (

output out);

assign out = 1'b0;

endmodule

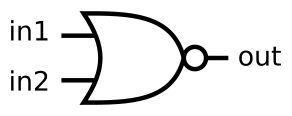

3. 或非门(NOR)

module top_module (

input in1,

input in2,

output out);

assign out = ~(in1 | in2);

endmodule

4. 二级电路(中间加导线)

module top_module (

input in1,

input in2,

input in3,

output out);

wire out1;

assign out1 = ~(in1^in2);

assign out = out1^in3;

endmodule

5. 7420 chip

module top_module (

input p1a, p1b, p1c, p1d,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

assign p1y = ~(p1a&p1b&p1c&p1d);

assign p2y = ~(p2a&p2b&p2c&p2d);

endmodule

6. Truthtable1

module top_module(

input x3,

input x2,

input x1, // three inputs

output f // one output

);

assign f = (~x3&x2)|(x3&x1)|(x2&x1);

endmodule

7. Mt2015 eq2

module top_module(

input [1:0] A,

input [1:0] B,

output z);

assign z = (A[1:0]==B[1:0]); // Comparisons produce a 1 or 0 result.

// Another option is to use a 16-entry truth table ( {A,B} is 4 bits, with 16 combinations ).

// There are 4 rows with a 1 result. 0000, 0101, 1010, and 1111.

endmodule

8. Mt2015 q4

module module_a (input x, input y, output z);

assign z = (x^y)&x;

endmodule

module module_b ( input x, input y, output z );

assign z = ~(x^y);

endmodule

module top_module (input x, input y, output z);

wire a1,a2,b1,b2;

module_a inst_a1 (x,y,a1);

module_a inst_a2 (x,y,a2);

module_b inst_b1 (x,y,b1);

module_b inst_b2 (x,y,b2);

wire ret1,ret2;

assign ret1 = a1|b1;

assign ret2 = a2&b2;

assign z = ret1^ret2;

endmodule

9. Ringer

module top_module (

input ring,

input vibrate_mode,

output ringer, // Make sound

output motor // Vibrate

);

assign ringer = (~vibrate_mode & ring);

assign motor = (vibrate_mode & ring);

endmodule

10. Thermostat

module top_module (

input too_cold,

input too_hot,

input mode,

input fan_on,

output heater,

output aircon,

output fan

);

assign heater = (mode & too_cold);

assign aircon = (~mode & too_hot);

assign fan = (heater | aircon | fan_on);

endmodule

11. Popcount3

module top_module (

input [2:0] in,

output [1:0] out

);

// This is a function of 3 inputs. One method is to use a 8-entry truth table:

// in[2:0] out[1:0]

// 000 00

// 001 01

// 010 01

// 011 10

// 100 01

// 101 10

// 110 10

// 111 11

assign out[0] = (~in[2] & ~in[1] & in[0]) | (~in[2] & in[1] & ~in[0]) | (in[2] & ~in[1] & ~in[0]) | (in[2] & in[1] & in[0]);

assign out[1] = (in[1] & in[0]) | (in[2] & in[0]) | (in[2] & in[1]);

endmodule

12. Gatesv100

module top_module(

input [99:0] in,

output [98:0] out_both,

output [99:1] out_any,

output [99:0] out_different );

always @(*) begin

for (int i=0;i<99;i++) begin

out_both[i] = in[i]&in[i+1];

end

end

always @(*) begin

for (int i=1;i<100;i++) begin

out_any[i] = in[i]|in[i-1];

end

end

always @(*) begin

for (int i=0;i<99;i++) begin

out_different[i] = in[i]^in[i+1];

end

end

assign out_different[99] = in[99]^in[0];

endmodule

二、Multiplexers

-

Mux2to1

module top_module ( input a, input b, input sel, output out ); assign out = (sel & b) | (~sel & a); // Mux expressed as AND and OR // Ternary operator is easier to read, especially if vectors are used: // assign out = sel ? b : a; endmodule -

Mux2to1v

module top_module( input [99:0] a, b, input sel, output [99:0] out ); assign out = (sel) ? b : a; endmodule -

Mux9to1v

module top_module( input [15:0] a, b, c, d, e, f, g, h, i, input [3:0] sel, output [15:0] out ); // Case statements can only be used inside procedural blocks (always block) // This is a combinational circuit, so use a combinational always @(*) block. always @(*) begin out = '1; // '1 is a special literal syntax for a number with all bits set to 1. // '0, 'x, and 'z are also valid. // I prefer to assign a default value to 'out' instead of using a // default case. case (sel) 4'h0: out = a; 4'h1: out = b; 4'h2: out = c; 4'h3: out = d; 4'h4: out = e; 4'h5: out = f; 4'h6: out = g; 4'h7: out = h; 4'h8: out = i; endcase end endmodule -

Mux256to1

module top_module( input [255:0] in, input [7:0] sel, output reg out ); //过于精妙,verilog可以直接识别sel的大小,并且数组索引可以是变量 assign out = in[sel]; endmodule -

Mux256to1v

module top_module ( input [1023:0] in, input [7:0] sel, output [3:0] out ); // We can't part-select multiple bits without an error, but we can select one bit at a time, // four times, then concatenate them together. assign out = {in[sel*4+3], in[sel*4+2], in[sel*4+1], in[sel*4+0]}; // Alternatively, "indexed vector part select" works better, but has an unfamiliar syntax: // assign out = in[sel*4 +: 4]; // Select starting at index "sel*4", then select a total width of 4 bits with increasing (+:) index number. // assign out = in[sel*4+3 -: 4]; // Select starting at index "sel*4+3", then select a total width of 4 bits with decreasing (-:) index number. // Note: The width (4 in this case) must be constant. endmodule

三、Arithmetic Circuits

1. Full adder

module top_module(

input a, b, cin,

output cout, sum );

//行为级描述

assign {cout,sum} = a+b+cin;

endmodule

2.Full adder 3-bits

module fadd1(

input a, b,

input cin,

output cout,

output sum );

assign cout = (a&b) | (a^b)&cin;

assign sum = a^b^cin;

endmodule

module top_module(

input [2:0] a, b,

input cin,

output [2:0] cout,

output [2:0] sum );

fadd1 inst1 (a[0],b[0],cin,cout[0],sum[0]);

fadd1 inst2 (a[1],b[1],cout[0],cout[1],sum[1]);

fadd1 inst3 (a[2],b[2],cout[1],cout[2],sum[2]);

endmodule

357

357

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?