VL53 单端口RAM

1 思路

简简单单,读取存储器单元值操作即可

2 功能猜想版

说明:

下面注释就是我对模块端口信号 自己猜测的理解。

因为题目并没有说清楚,甚至连参考波形都没有给出。

唉,这就完全是让人猜测呢,如果一点学术背景的人来刷题,指定不容易!!

好在,我有较为深厚的学术背景

(1)代码

`timescale 1ns/1ns

module RAM_1port(

input clk,

input rst,

input enb, //读写使能:0-写;1-读

input [6:0]addr, //读写地址

input [3:0]w_data, //写入数据

output wire [3:0]r_data//读出数据

);

//*************code***********//

//ROM

reg [3:0] ROM [6:0];

//写入数据

always@(posedge clk, negedge rst)begin

if(rst==0) ROM[addr] <=ROM[addr];

else ROM[addr] <= (enb==0) ? w_data :ROM[addr];

end

//读出数据

reg [3:0] data_out;

always@(posedge clk, negedge rst)begin

if(rst==0) data_out<=0;

else data_out<= enb ? ROM[addr] : 0;

end

assign r_data =data_out;

//*************code***********//

endmodule

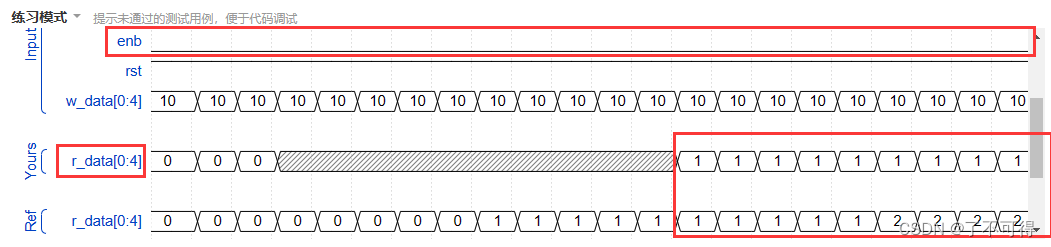

(2)问题:读写控制搞反

【修改】将代码中用到enb的地方,高改低,低改高 即可

(3)仿真结果

enb=0 控制读取数据 确实无误

但是读取的数据是不对的。

3 不断试错版

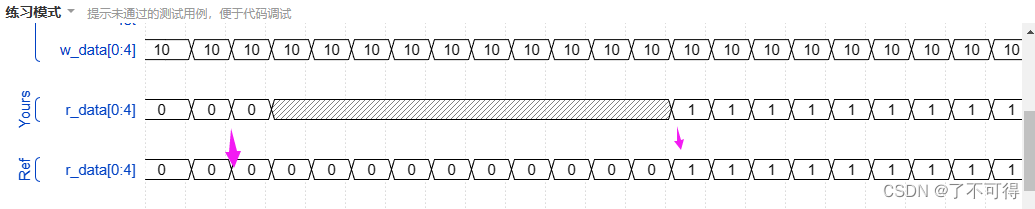

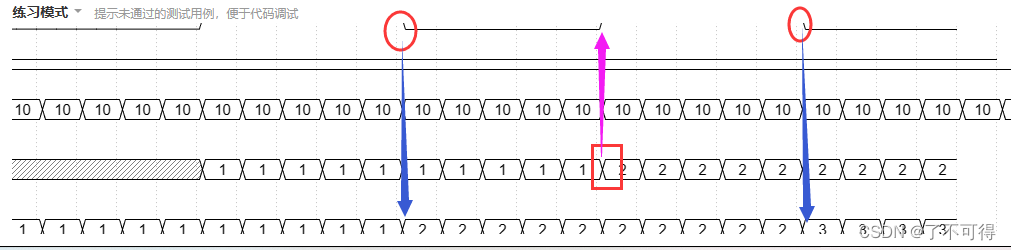

(1)问题2:读取数据晚半拍

还是上面程序的仿真波形。

仔细观察,发现问题:

仔细观察上面的仿真波形,发现问题所在:人家读数据是在clk 下降沿读的

(2)解决2:用【下降沿读取数据】

代码

//读出数据

reg [3:0] data_out;

always@(negedge clk, negedge rst)begin

if(rst==0) data_out<=0;

else data_out<= (enb==0) ? ROM[addr] : 0;

end

assign r_data =data_out;

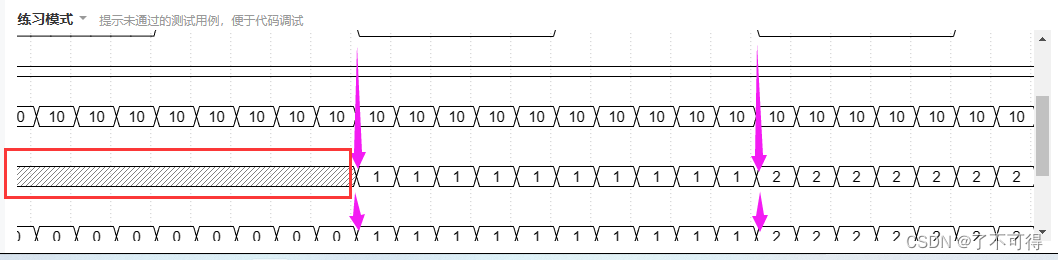

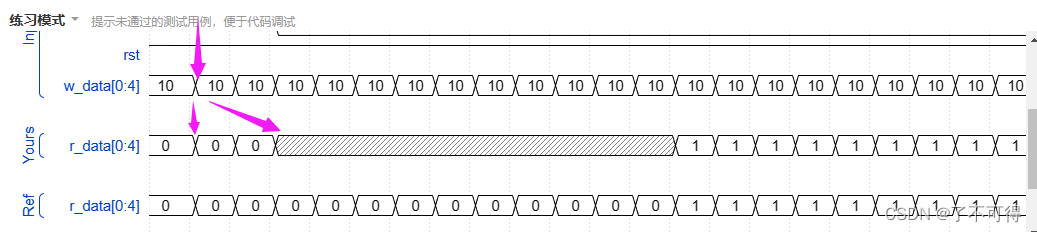

仿真结果

可见修改后的输出,基本上都对应上了。

(3)问题3:读出数据为不定值

但是从上面代码的仿真结果中发现了另一个问题:

当enb=1表示 写功能时,RAM的值没有写进去

噢!不对!!!这里的r_data是读RAM的值,所以写进RAM的值在这里暂且是看不到的。

所以这里的问题是从RAM中读出的数据为不定值啦

而此时【读数据】是下降沿有效,要么读到的是地址10要么是地址0上的值,好像更可能是地址0上的值为不定值

所以这个问题定位到,向RAM写入数据时的逻辑,看为什么导致地址0上的数据为不定值

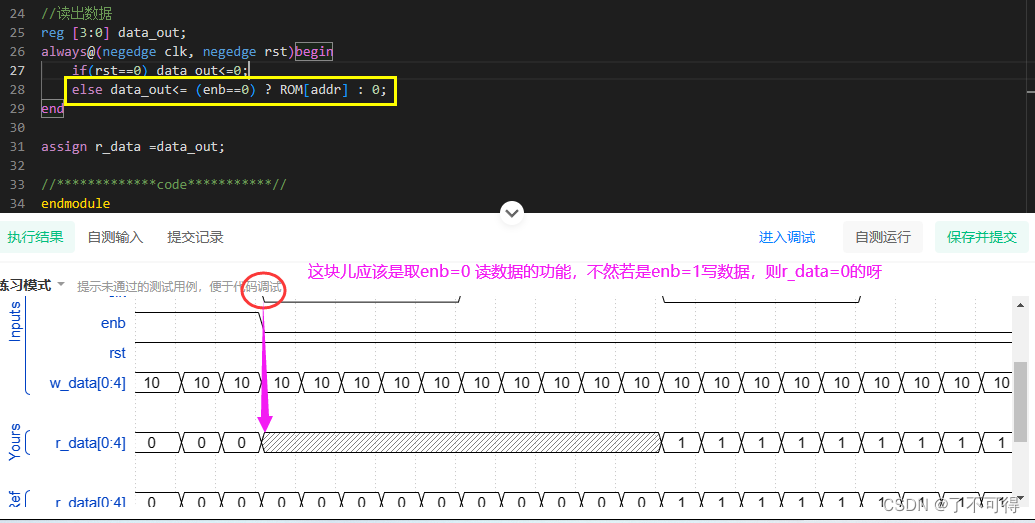

(4)解决3:解决了很多次,但都没解决

原来写入RAM的代码为:

//写入数据

always@(posedge clk, negedge rst)begin

if(rst==0) ROM[addr] <= ROM[addr];

else ROM[addr] <=enb ? w_data :ROM[addr];

end

针对这个问题,我修改了无数次可能,但最终都没有修改成功。心情被搞坏了,气炸了

最后的代码是这样的:

`timescale 1ns/1ns

module RAM_1port(

input clk,

input rst,

input enb, //读写使能:0-写;1-读 //根据提交的错误结果,知道这里逻辑是 1-写 0-读

input [6:0

本文详细记录了使用Verilog实现单端口RAM的过程,从最初的读写控制错误,到解决读取数据延迟和不定值问题,再到尝试组合逻辑写入RAM的编译错误,最终实现可行的RAM读写方案。作者强调了理解RAM深度的重要性,并分享了通过观察时序波形图来确定数据采集时刻的经验。

本文详细记录了使用Verilog实现单端口RAM的过程,从最初的读写控制错误,到解决读取数据延迟和不定值问题,再到尝试组合逻辑写入RAM的编译错误,最终实现可行的RAM读写方案。作者强调了理解RAM深度的重要性,并分享了通过观察时序波形图来确定数据采集时刻的经验。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1147

1147

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?