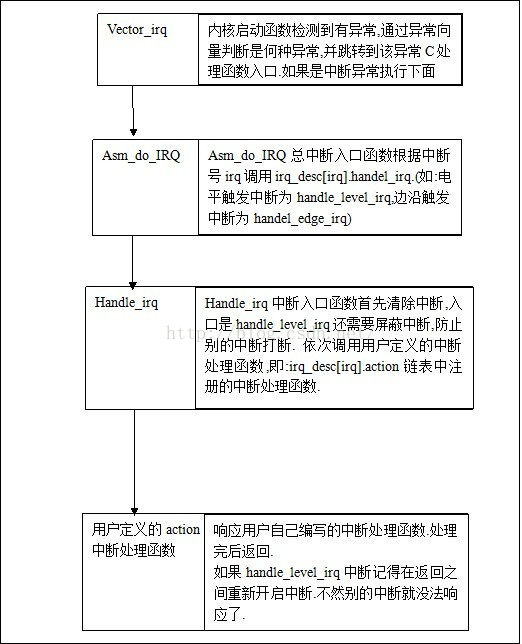

Linux 中,当外设触发中断后,大体处理流程如下:

a -- 具体CPU architecture相关的模块会进行现场保护,然后调用machine driver对应的中断处理handler;

b -- machine driver对应的中断处理handler中会根据硬件的信息获取HW interrupt ID,并且通过irq domain模块翻译成IRQ number;

c -- 调用该IRQ number 对应的high level irq event handler,在这个high level的handler中,会通过和interupt controller交互,进行中断处理的flow control(处理中断的嵌套、抢占等),当然最终会遍历该中断描述符的IRQ action list,调用外设的specific handler来处理该中断;

d -- 具体CPU architecture相关的模块会进行现场恢复;

总结下来,整个过程可以分为三部分:1、硬件处理部分;2、汇编处理部分;3、C 处理部分;

下面我们来追踪一下代码,了解当中断发生时,Linux 是如何处理的,前面的一些中断初始化部分就不再这里详述了,下面开始具体分析:

一、硬件处理部分

当一切准备好之后,一旦打开处理器的全局中断就可以处理来自外设的各种中断事件了。

当外设(SOC内部或者外部都可以)检测到了中断事件,就会通过interrupt requestion line上的电平或者边沿(上升沿或者下降沿或者both)通知到该外设连接到的那个中断控制器,而中断控制器就会在多个处理器中选择一个,并把该中断通过IRQ(或者FIQ,本文不讨论FIQ的情况)分发给该processor。

ARM处理器感知到了中断事件后,会进行下面一系列的动作(硬件处理部分):

1、切换处理器模式

修改 CPSR 寄存器中的 M[4:0],切换处理器模式位 IRQ Mode(这里M[4:0] 所添值为 10010);

2、保护现场

保存发生中断时,CPSR值与PC值(为恢复现场做准备);这里要注意,此时中断可能发生在 usr mode (用户空间),也可能发生在 SVC mode(内核空间);

3、mask IRQ exception

关闭IRQ中断,也就是设定CPSR.I = 1;

4、设定PC值为IRQ exception vector

实现向异常向量表的跳转,ARM处理器会跳转到IRQ的exception vector地址,到这硬件所做的工作就结束了,下面就是软件行为了。

软件处理部分流程如下:

可以看到 Vetor_irq 是汇编部分入口点,而Asm_do_irq 是C 部分入口点,下面分析Vetor_irq 向 Asm_do_irq 跳转过程

二、汇编部分

前面硬件部分结束后,跳转到相应的异常中断处理程序处执行,对于ARMv7向量表普遍是0xFFFF0018 ,而对于低向量PC=0x00000018

假设在用户空间时,产生了外部硬件中断,这个时候的会跳转到异常向量表,向量表(vector table)的代码如下

【arch/arm/kernel/entry-armv.S】

__vectors_start:---------------〉在中断向量表被拷贝后,该地址就是0xffff0000.

ARM( swi SYS_ERROR0 )

THUMB( svc #0 )

THUMB( nop )

W(b) vector_und + stubs_offset

W(ldr) pc, .LCvswi + stubs_offset

W(b) vector_pabt + stubs_offset

W(b) vector_dabt + stubs_offset

W(b) vector_addrexcptn + stubs_offset

W(b)vector_irq + stubs_offset----------〉当外部中断产生时,pc直接指向这个地址。

W(b) vector_fiq + stubs_offset

.globl __vectors_end 1、IRQ mode中的处理 (vector table --- > vector_irq )

IRQ mode的处理都在vector_irq中,vector_stub是一个宏,定义如下:

/*

* Vector stubs.

*

* This code is copied to 0xffff0200 so we can use branches in the

* vectors, rather than ldr's. Note that this code must not

* exceed 0x300 bytes.

*

* Common stub entry macro:

* Enter in IRQ mode, spsr = SVC/USR CPSR, lr = SVC/USR PC

*

* SP points to a minimal amount of processor-private memory, the address

* of which is copied into r0 for the mode specific abort handler.

*/

.macro vector_stub, name, mode, correction=0

.align 5

vector_\name:

Linux 中,当外设触发中断后,大体处理流程如下:a -- 具体CPU architecture相关的模块会进行现场保护,然后调用machine driver对应的中断处理handler;b -- machine driver对应的中断处理handler中会根据硬件的信息获取HW interrupt ID,并且通过irq domain模块翻译成IRQ number;c -- 调用该

Linux 中,当外设触发中断后,大体处理流程如下:a -- 具体CPU architecture相关的模块会进行现场保护,然后调用machine driver对应的中断处理handler;b -- machine driver对应的中断处理handler中会根据硬件的信息获取HW interrupt ID,并且通过irq domain模块翻译成IRQ number;c -- 调用该

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

811

811

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?