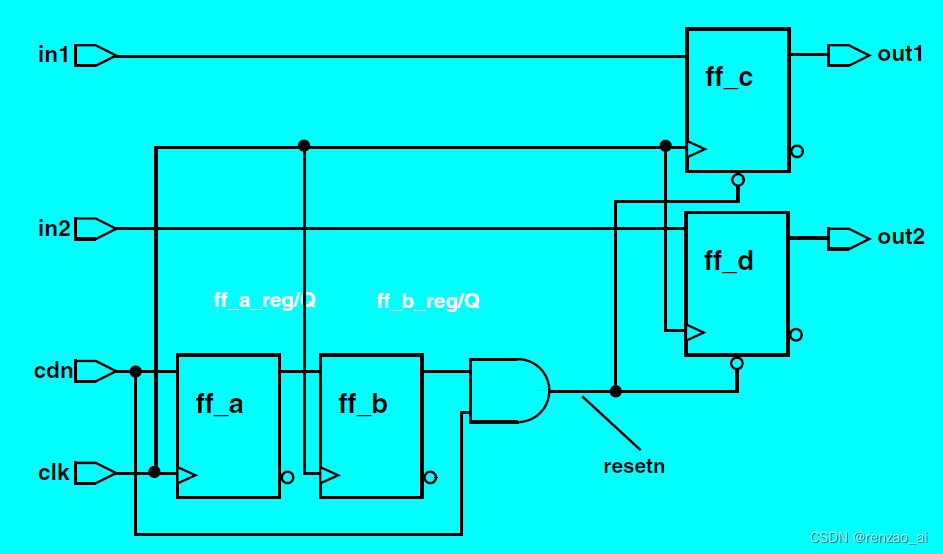

电路结构

电路对于SCAN不友好的地方在于 resetn不可控,两种解决手段

(1) 改代码:或者RTL设计人员修改,或者DFT工具 autofix (本文使用autofix)

(2) 改pattern:利用初始化序列控制住resetn不复位。

RTL

module ssug (in1, in2, clk, cdn, out1, out2);

input in1, in2, clk, cdn;

output out1, out2;

reg ff_a, ff_b, ff_c, ff_d;

wire resetn;

always @(posedge clk) begin

ff_b <= ff_a;

ff_a <= cdn;

end

assign resetn = cdn & ff_b;

always @(posedge clk or negedge resetn) begin

if (!resetn) begin

ff_c <= 1’b0;

ff_d <= 1’b0;

end

else begin

ff_c <= in1;

ff_d <= in2;

end

end

assign out1 = ff_c;

assign out2 = ff_d;

endmodule

脚本

set_app_var search_path “…/ref …/ref/db ./rtl ./”

set_app_var target_library “sc_max.db”

set_app_var link_library “* sc_max.db dw_foundation.sldb”

set synthetic_library {dw_foundation.sldb}

set hdlin_enable_rtldrc_info true;

read_verilog rtl/ssug.v

current_design ssug

link

create_clock -name clk [get_ports clk] -period 100

compile -scan

write -format ddc -hierarchy -output results/ssug.scan.ddc

write -format verilog -hierarchy -output results/ssug.scan.no_protocol.vg

set_dft_signal -view existing_dft -type ScanClock -timing [list 45 55 ] -port clk

set_dft_signal -view existing_dft -type Constant -active_state 1 -port cdn

create_test_protocol

write_test_protocol -output first.spf

write -format verilog -hierarchy -output results/ssug.scan.protocol.vg

结果

(1)如果没有处理resetn

dft_drc

Begin Pre-DFT violations...

Warning: Reset input CDN of DFF ff_c_reg was not controlled. (D3-1)

Information: There is 1 other cell with the same violation. (TEST-173)

Pre-DFT violations completed...

SEQUENTIAL CELLS WITH VIOLATIONS

* 2 cells have test design rule violations

SEQUENTIAL CELLS WITHOUT VIOLATIONS

* 2 cells are valid scan cells

(2)没有test协议之前,

scan netlist

module ssug ( in1, in2, clk, cdn, out1, out2 );

input in1, in2, clk, cdn;

output out1, out2;

wire ff_b, ff_a, n7;

sdnrq1 ff_a_reg ( .D(cdn), .SD(1'b0), .SC(1'b0), .CP(clk), .Q(ff_a) );

sdnrq1 ff_b_reg ( .D(ff_a), .SD(1'b0), .SC(1'b0), .CP(clk), .Q(ff_b) );

sdcrq1 ff_c_reg ( .D(in1), .SD(1'b0), .SC(1'b0), .CP(clk), .CDN(n7), .Q(out1) );

sdcrq1 ff_d_reg ( .D(in2), .SD(1'b0), .SC(1'b0), .CP(clk), .CDN(n7), .Q(out2) );

an02d1 U9 ( .A1(ff_b), .A2(cdn), .Z(n7) );

endmodule

(3)建立test协议之后

scan netlist

module ssug ( in1, in2, clk, cdn, out1, out2, test_si, test_so, test_se );

input in1, in2, clk, cdn, test_si, test_se;

output out1, out2, test_so;

wire ff_b, ff_a, n7;

assign test_so = ff_b;

sdnrq1 ff_a_reg ( .D(cdn), .SD(test_si), .SC(test_se), .CP(clk), .Q(ff_a) );

sdnrq1 ff_b_reg ( .D(ff_a), .SD(ff_a), .SC(test_se), .CP(clk), .Q(ff_b) );

sdcrq1 ff_c_reg ( .D(in1), .SD(1'b0), .SC(1'b0), .CP(clk), .CDN(n7), .Q(out1) );

sdcrq1 ff_d_reg ( .D(in2), .SD(1'b0), .SC(1'b0), .CP(clk), .CDN(n7), .Q(out2) );

an02d1 U9 ( .A1(ff_b), .A2(cdn), .Z(n7) );

endmodule

如果没有修正,虽然可以插入scan,但是DRC问题依然。

(4)set_dft_configuration -fix_reset enable之后

preview_dft

************ Test Point Plan Report ************

Total number of test points : 1

Number of Autofix test points: 1

Number of Wrapper test points: 0

Number of test modes : 1

Number of test point enables : 0

Number of data sources : 1

Number of data sinks : 0

**************************************************

insert_dft

module ssug ( in1, in2, clk, cdn, out1, out2, test_si, test_so, test_se,

data_source, test_mode );

input in1, in2, clk, cdn, test_si, test_se, data_source, test_mode;

output out1, out2, test_so;

wire ff_b, ff_a, n15, n16;

sdnrq1 ff_a_reg ( .D(cdn), .SD(test_si), .SC(test_se), .CP(clk), .Q(ff_a) );

sdnrq1 ff_b_reg ( .D(ff_a), .SD(ff_a), .SC(test_se), .CP(clk), .Q(ff_b) );

sdcrq1 ff_c_reg ( .D(in1), .SD(ff_b), .SC(test_se), .CP(clk), .CDN(n15), .Q(

out1) );

sdcrq1 ff_d_reg ( .D(in2), .SD(out1), .SC(test_se), .CP(clk), .CDN(n15), .Q(

out2) );

an02d1 U9 ( .A1(ff_b), .A2(cdn), .Z(n16) );

mx02d0 U10 ( .I0(ff_b), .I1(out2), .S(test_se), .Z(test_so) );

mx02d1 U11 ( .I0(n16), .I1(data_source), .S(test_mode), .Z(n15) );

endmodule

全部上链。

1989

1989

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?