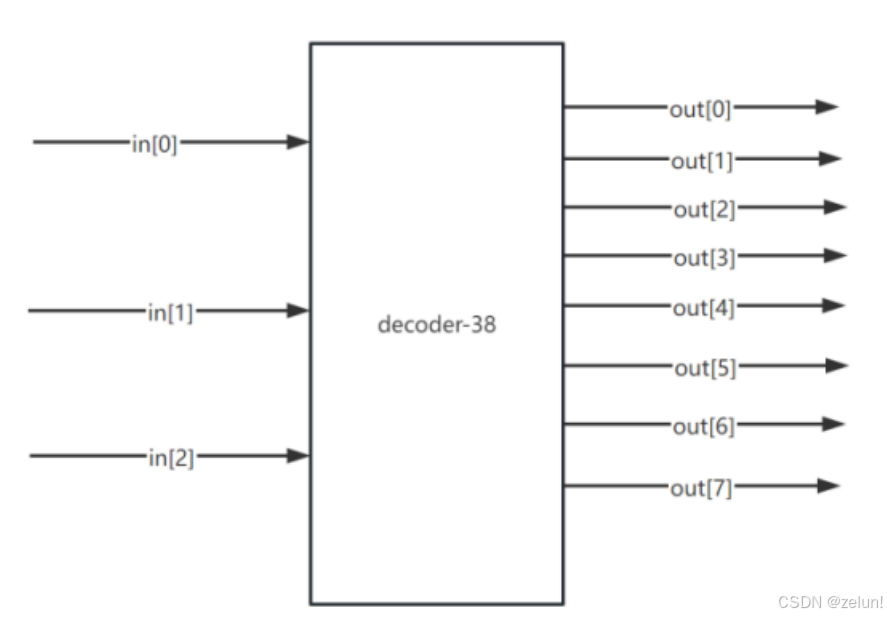

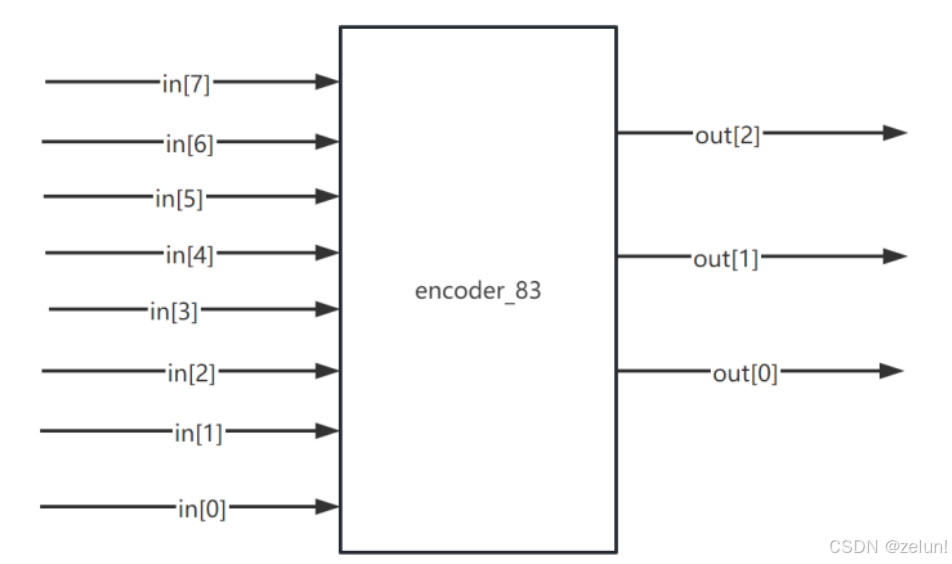

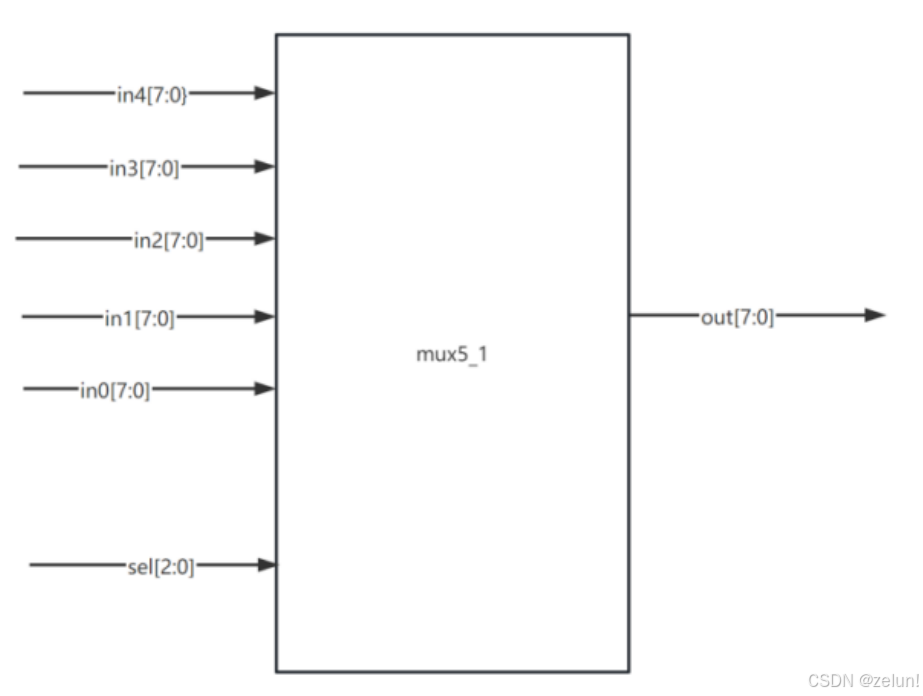

- 实验设计图(或接口描述)

图1 3-8 译码器

图2 带有优先级的 83 编码器

图3 5选1多路选择器

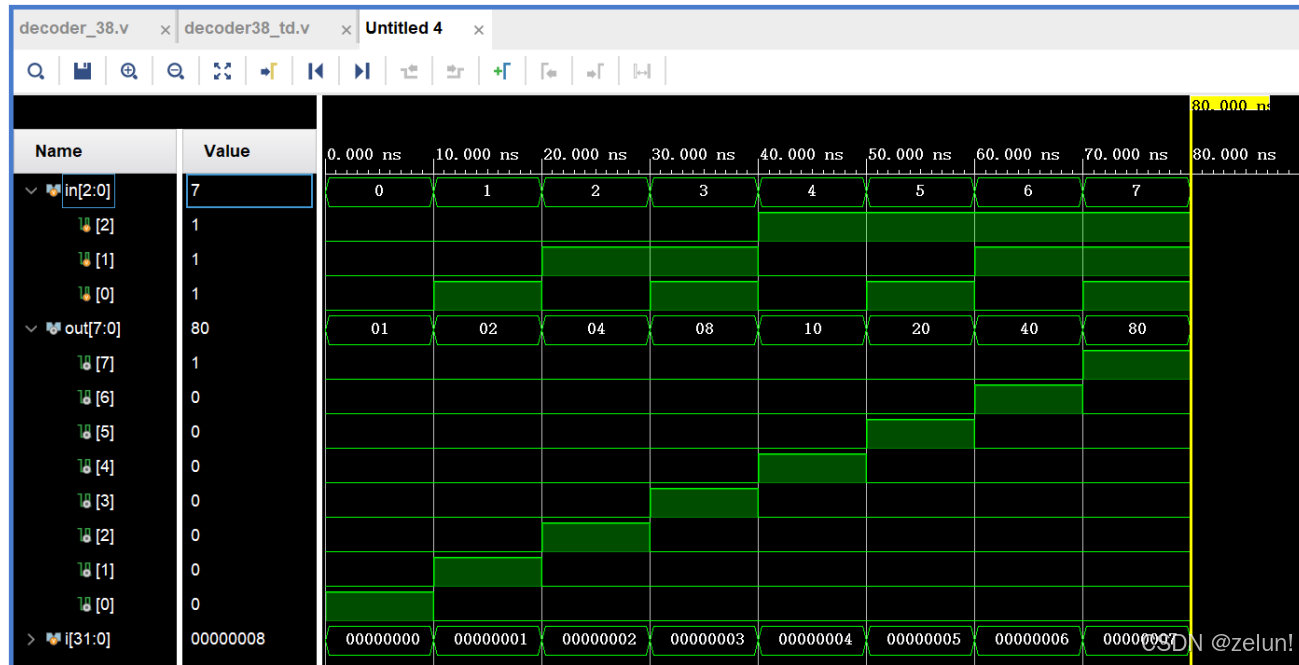

图4 3-8 译码器仿真图

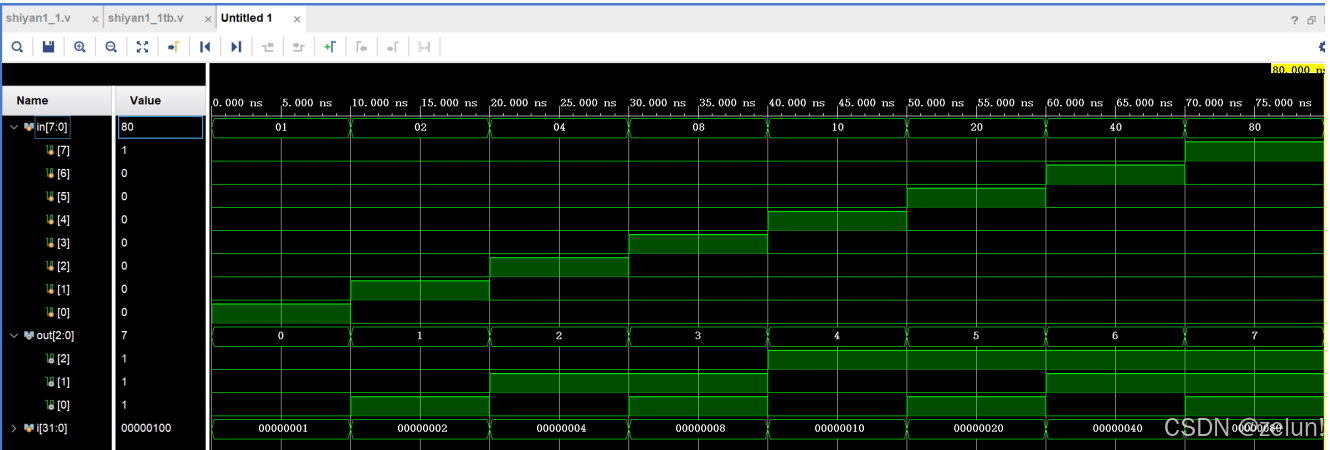

图6 带有优先级的 83 编码器仿真图

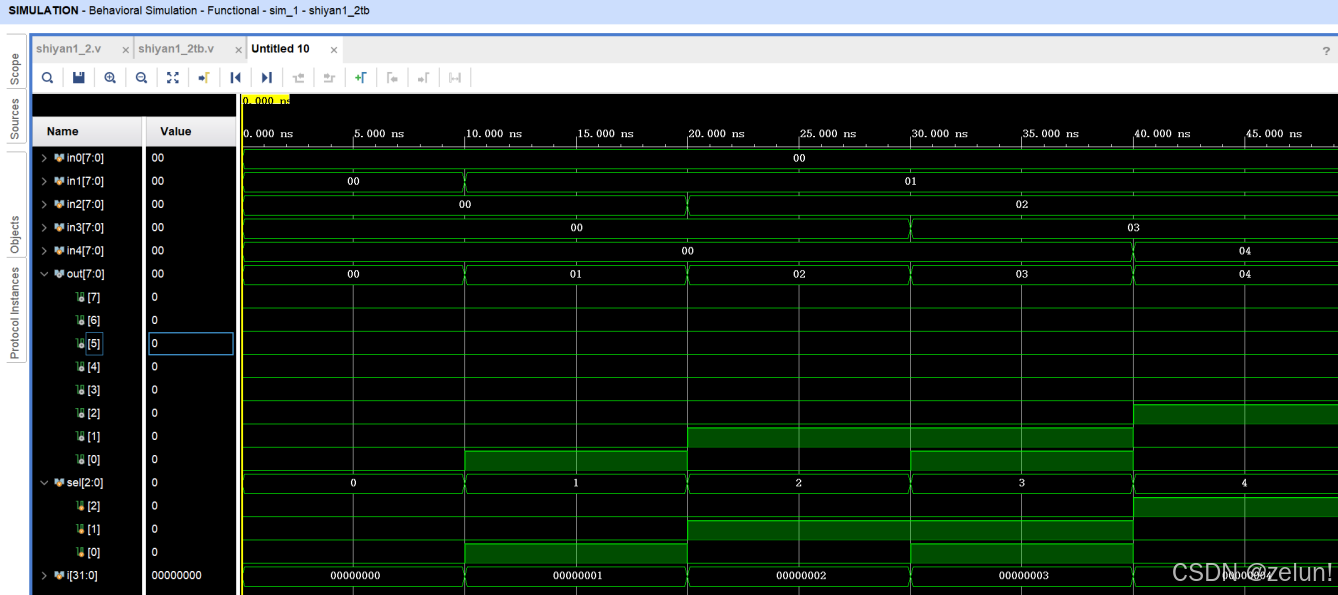

图7 5选1多路选择器仿真图

//3-8译码器设计代码

`timescale 1ns / 1ps

module decoder_38(

input wire [2:0]in,

output wire [7:0]out

);

assign out=(in==3'd0)?8'd1:

(in==3'd1)?8'd2:

(in==3'd2)?8'd4:

(in==3'd3)?8'd8:

(in==3'd4)?8'd16:

(in==3'd5)?8'd32:

(in==3'd6)?8'd64:

(in==3'd7)?8'd128:

8'd0;

endmodule

//3-8译码器仿真代码

`timescale 1ns / 1ps

module decoder38_td(

);

reg[2:0]in;

wire[7:0]out;

decoder_38 d38(in,out);

integer i=0;

initial begin

for(i=0;i<=7;i=i+1)begin

in=i;

#10;

end

$finish;

end

endmodule

//8-3编码器设计代码

module shiyan1_1(

input wire [7:0]in,

output wire [2:0]out

);

assign out=(in==8'd1)?8'd0:

(in==8'd2)?8'd1:

(in==8'd4)?8'd2:

(in==8'd8)?8'd3:

(in==8'd16)?8'd4:

(in==8'd32)?8'd5:

(in==8'd64)?8'd6:

(in==8'd128)?8'd7:

8'd0;

endmodule

//8-3编码器仿真代码

`timescale 1ns / 1ps

module shiyan1_1tb(

);

reg [7:0]in;

wire [2:0]out;

shiyan1_1 e83(in,out);

integer i = 0;

initial begin

//in = 1;

for(i=1;i<=128;i=i*2)begin

in = i;

#10; //for(i=0;i<=7;i=i+1)begin

//in = in<<1;

end

$finish;

end

endmodule

//5选1多路选择器设计代码

`timescale 1ns / 1ps

module shiyan1_2(

input [7:0]in0,

input [7:0]in1,

input [7:0]in2,

input [7:0]in3,

input [7:0]in4,

output wire [7:0]out,

input wire [2:0]sel

);

assign out=(sel==3'b000)?in0:

(sel==3'b001)?in1:

(sel==3'b010)?in2:

(sel==3'b011)?in3:

(sel==3'b100)?in4:

8'b0;

endmodule

//5选1多路选择器仿真代码

`timescale 1ns / 1ps

module shiyan1_2tb(

);

reg [7:0]in0;

reg [7:0]in1;

reg [7:0]in2;

reg [7:0]in3;

reg [7:0]in4;

wire [7:0]out;

reg [2:0]sel;

shiyan1_2 mux51(

.in0(in0),

.in1(in1),

.in2(in2),

.in3(in3),

.in4(in4),

.out(out),

.sel(sel)

);

integer i=0;

initial begin

in0 = 8'd0;

in1 = 8'd0;

in2 = 8'd0;

in3 = 8'd0;

in4 = 8'd0;

for(i=0;i<=4;i=i+1)begin

sel=i;

//#10;

if(sel==3'b000)begin

in0 = 8'd0;

end

if(sel==3'b001)begin

in1 = 8'd1;

end

if(sel==3'b010)begin

in2 = 8'd2;

end

if(sel==3'b011)begin

in3 = 8'd3;

end

if(sel==3'b100)begin

in4 = 8'd4;

end

#10;

end

$finish;

end

endmodule

904

904

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?