没有PLL的时钟:

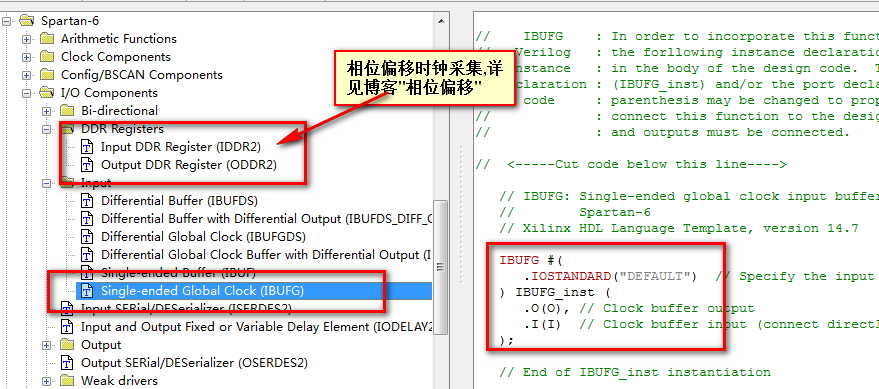

输入时钟在没有连接到PLL中,那么一定在输入端链接BUFG,

IBUFG #(

.IOSTANDARD("DEFAULT") // Specify the input I/O standard

) IBUFG_inst (

.O(O), // Clock buffer output

.I(I) // Clock buffer input (connect directly to top-level port)

);//此代码请参考,ISE软件中的语言模板工具。

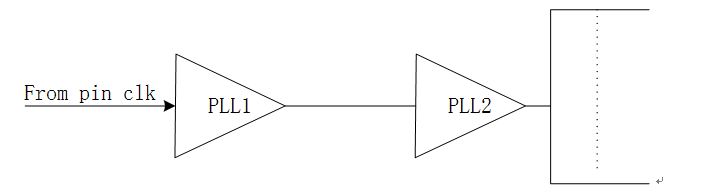

两个PLL级联的时钟:

第一个PLL称作P1第二称作P2

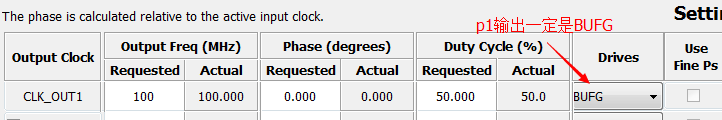

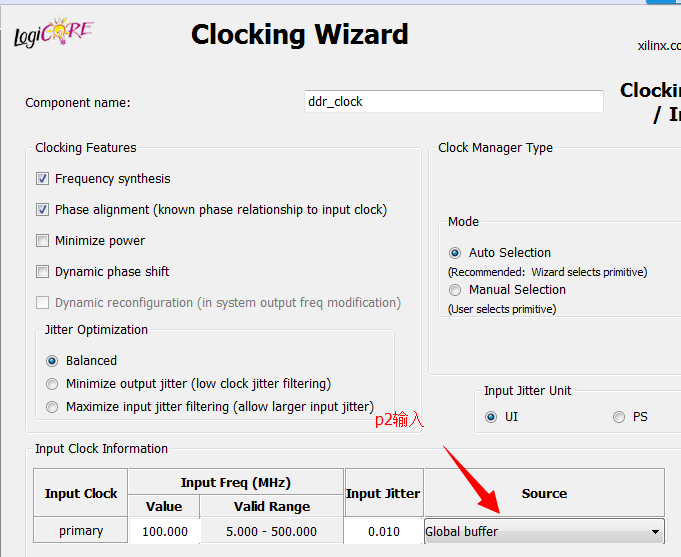

P1输出的时钟要链接BUFG,作为第二级PLL P2的输入,第二级PLL的输入时钟要选择为BUFG输入。

IP核设置:

输入模型:

参考设计代码:

clk_65M clk_65M_inst

(// Clock in ports

.CLK(CLK), // IN

// Clock out ports

.clk_65M(clk_65M), // OUT

.clk_100M(clk_100M), // OUT

.CLK_100(CLK_100)); // OUT

clk_333M clk_333M_inst

(// Clock in ports

.CLK_100(CLK_100), // IN

// Clock out ports

.clk_333M(clk_333M)); // OUT

360

360

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?