整个芯片中时钟信号到达时间的差异成为时钟偏移,即clock skew。在时序设计的时候,满足寄存器的建立时间和保持时间的要求是最基本的设计原则。在相邻的寄存器之间的数据传输延迟,与时钟偏移应该满足一定的关系,在本节中,我们来详细地讨论其关系。

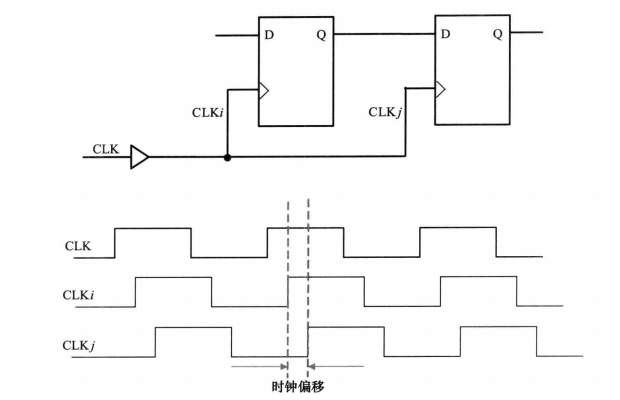

通过图1来看相邻寄存器之间传输的时候的数据延迟和时钟偏移,以及详细的时序关系

图 1 两个相邻触发器之间的时钟偏移

给定两个相邻的触发器DFF1和DFF2以及一个等电位时钟分布网络,这两个触发器之间的时钟偏移定义为:

Tskew = T2 - T1

在这里T1和T2分别从市中院到触发器DFF1和DFF2的延迟。

本文深入探讨了时钟偏移(clock skew)在时序设计中的重要性,强调了满足寄存器建立时间和保持时间的必要性。通过实例分析了短路径问题,指出当数据路径延迟小于时钟偏移时,可能导致功能错误。解决方案包括在数据路径上增加延迟、时钟翻转和交替相位时钟技术,以确保设计的稳健性和正确性。重点介绍了如何通过这些方法最小化时钟偏移,提高系统的时序性能。

本文深入探讨了时钟偏移(clock skew)在时序设计中的重要性,强调了满足寄存器建立时间和保持时间的必要性。通过实例分析了短路径问题,指出当数据路径延迟小于时钟偏移时,可能导致功能错误。解决方案包括在数据路径上增加延迟、时钟翻转和交替相位时钟技术,以确保设计的稳健性和正确性。重点介绍了如何通过这些方法最小化时钟偏移,提高系统的时序性能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1232

1232

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?