一些电路的综合结果

阻塞赋值 = 一般不带D-Q延时;非阻塞赋值<= 带D-Q延时。阻塞和非阻塞是针对块内下一条语句而言,阻塞赋值会阻塞后面语句执行(后面的逻辑例化于阻塞逻辑之后),在完成该条阻塞赋值后再执行后面的语句。这也与D-Q延时对电路的影响一致。

-

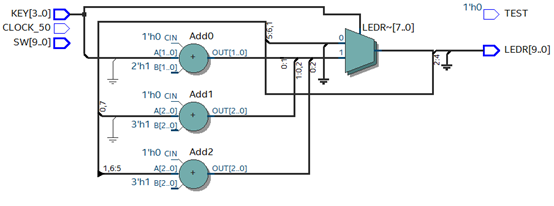

组合逻辑

//组合逻辑

always_combbegin:comb_led

LEDR[2:0]='0;//默认

for(int i =0;i<4;i++)begin

if(KEY[1])begin

LEDR[2:0]+=1;

end

end

end:comb_led

电路描述:0状态LEDR[2:0],在KEY[1]使能下进行4次阻塞加1。加法运算过程中KEY[1]的改变会影响加1的次数。值得注意的是的4次阻塞加1延时很小,使能在功能上是有效,但这种设计是否符合设计的意图。

-

锁存器

//锁存器

always_latchbegin:latch_led

if(KEY[2])//锁存器使能

LEDR[3:2]= SW[4:3];//使能输出

end:latch_led

电路描述:锁存器电路,在KEY[2] =1的时候输出结果为SW[4:3],在KEY[2] =0时,锁存器锁存。

-

触发器

//时序逻辑,不带使能

always_ff@(posedge CLOCK_50 ornegedge KEY[0])begin:ff_led

if(!KEY[0])

LEDR[5:4]<='0;//异步复位

elsebegin

LEDR[5:4]<= SW[4:3];//同步输出= else

if(KEY[1])

LEDR[5:4]<= SW[6:5];//同步输出

end

end:ff_led

电路描述:触发器,0时刻与其他时刻一致,KEY[1] = 0,时钟上沿同步输出为SW[4:3],KEY[1] = 1, 时钟上沿同步输出为SW[4:3]。对于时序电路,一般由复位置默认值。

-

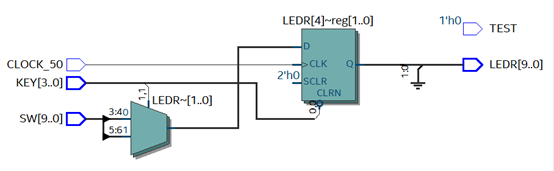

带使能触发器

//时序逻辑,带使能

always_ff@(posedge CLOCK_50 ornegedge KEY[0])

本文详细分析了SystemVerilog中使用for循环在组合逻辑和时序逻辑中的不同表现,包括阻塞赋值与非阻塞赋值的影响,以及带使能和不带使能的触发器行为。通过各种示例,展示了循环在电路综合时的优化和锁存器形成的情况。

本文详细分析了SystemVerilog中使用for循环在组合逻辑和时序逻辑中的不同表现,包括阻塞赋值与非阻塞赋值的影响,以及带使能和不带使能的触发器行为。通过各种示例,展示了循环在电路综合时的优化和锁存器形成的情况。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

255

255

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?