3—8译码器的真值表如下

| input | output | ||

| 0 | 0 | 0 | 0000_0001 |

| 0 | 0 | 1 | 0000_0010 |

| 0 | 1 | 0 | 0000_0100 |

| 0 | 1 | 1 | 0000_1000 |

| 1 | 0 | 0 | 0001_0000 |

| 1 | 0 | 1 | 0010_0000 |

| 1 | 1 | 0 | 0100_0000 |

| 1 | 1 | 1 | 1000_0001 |

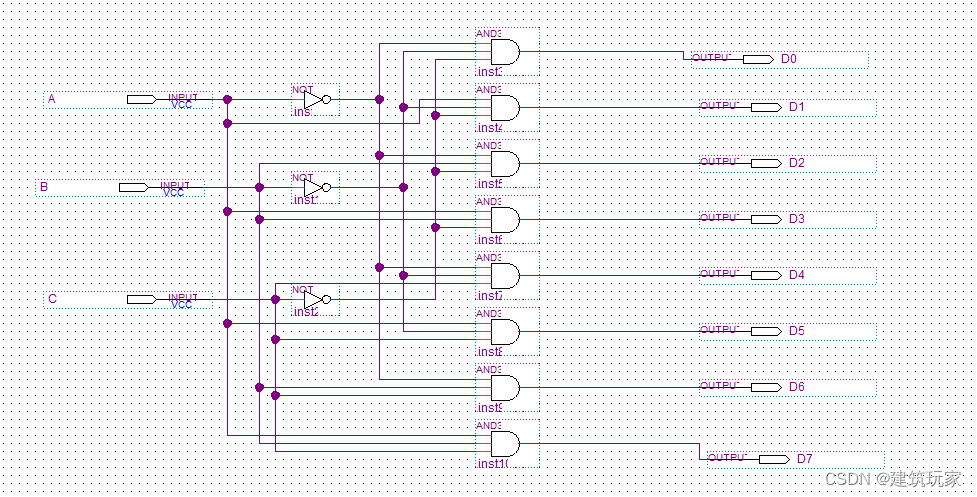

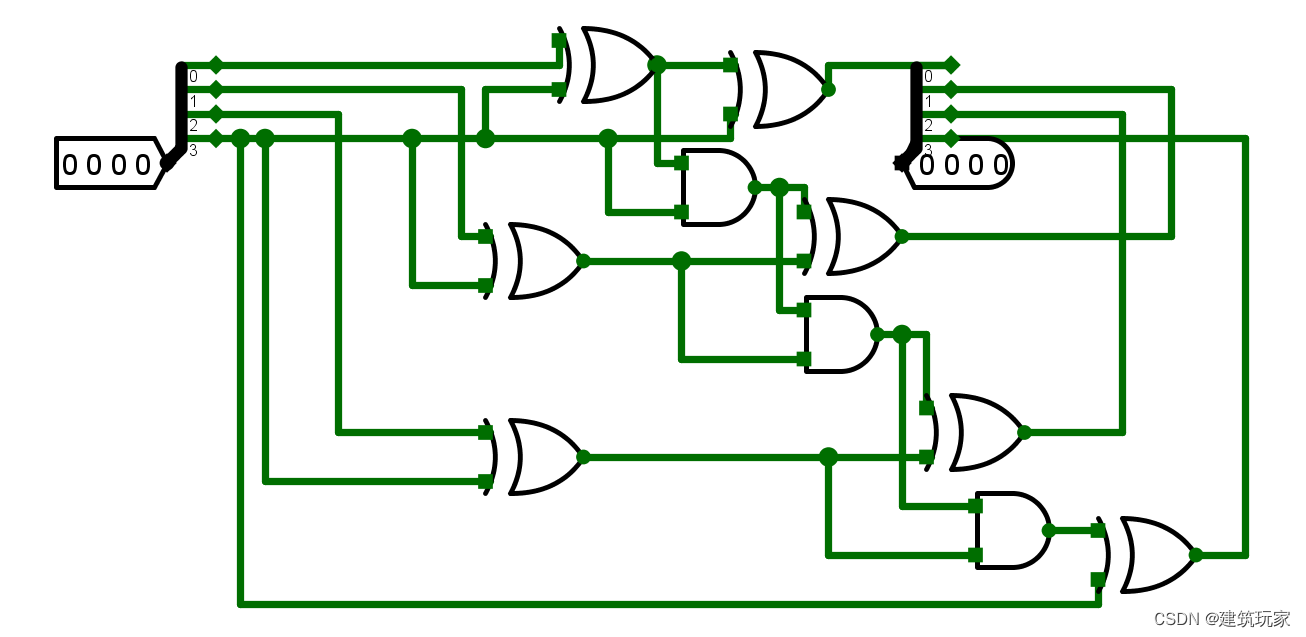

其电路图如下

我们打开quartus,新建一个verilog文件,写出下列代码

module decoder3_8(in1,in2,in3,out);

input in1,in2,in3;

output [7:0] out;

reg [7:0] out;

always@(*)

if({in1,in2,in3} == 3'b000)

out = 8'b1000_0001;

else if({in1,in2,in3} == 3'b001)

out = 8'b0000_0010;

else if({in1,in2,in3} == 3'b010)

out = 8'b0000_0100;

else if({in1,in2,in3} == 3'b011)

out = 8'b0000_1000;

else if({in1,in2,in3} == 3'b100)

out = 8'b0001_0000;

else if({in1,in2,in3} == 3'b101)

out = 8'b0010_0000;

else if({in1,in2,in3} == 3'b110)

out = 8'b0100_0000;

else if({in1,in2,in3} == 3'b111)

out = 8'b1000_0000;

else

out=8'b0000_0001;

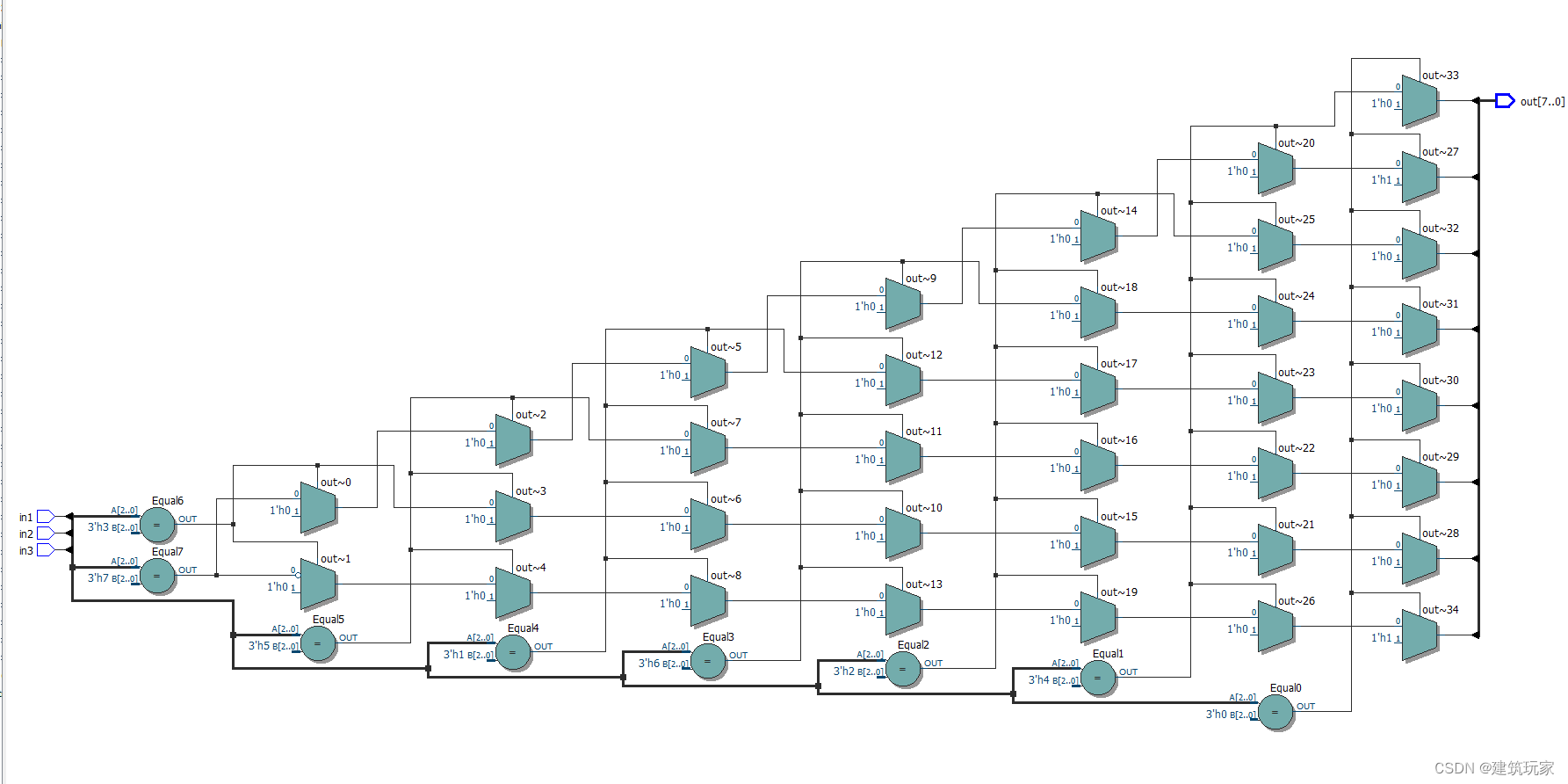

endmodule选择生成RTL电路

问题

1)Verilog 综合生成的3-8译码器电路原理图与原始设计电路存在什么差异? 仿真测试生成的结果是否与真值表一致?

一个是用门来表达,一个是系统自动生成;结果与真值表一致。

2) Verilog代码设计的3-8译码器模块的输出信号 为何要定义为 reg类型而不用默认wire(导线)类型?改成wire型是否可以? (即是否可以把 output reg [7:0] out 改为 output [7:0] out) 修改后会出现什么错误?为什么会出错?

在aways语句存在时,应当用reg类型而不用wire类型;不能改为wire类型,会提示分配左侧的对象“out”必须具有可变数据类型;因为在时序电路中应该用reg代表可变数据类型。

1位全加器

再次新建verilog文件,我们写出1位全加器的代码

module full_adder(

input a,

input b,

input cin,

output sum,

output cout

);

assign sum = a ^ b ^ cin;

assign cout = (a&b)||(cin&&(a^b));

endmodule

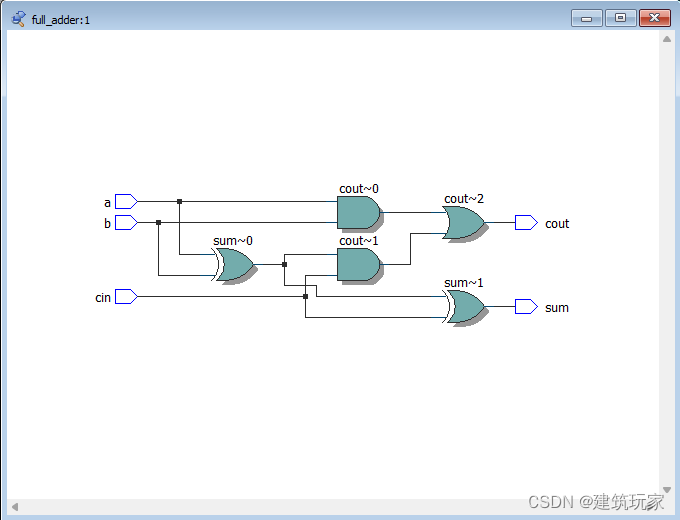

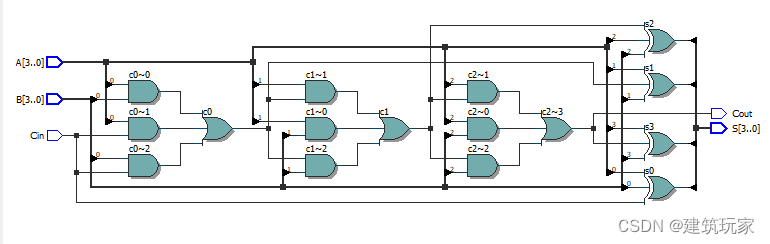

下图为生成的RTC电路图

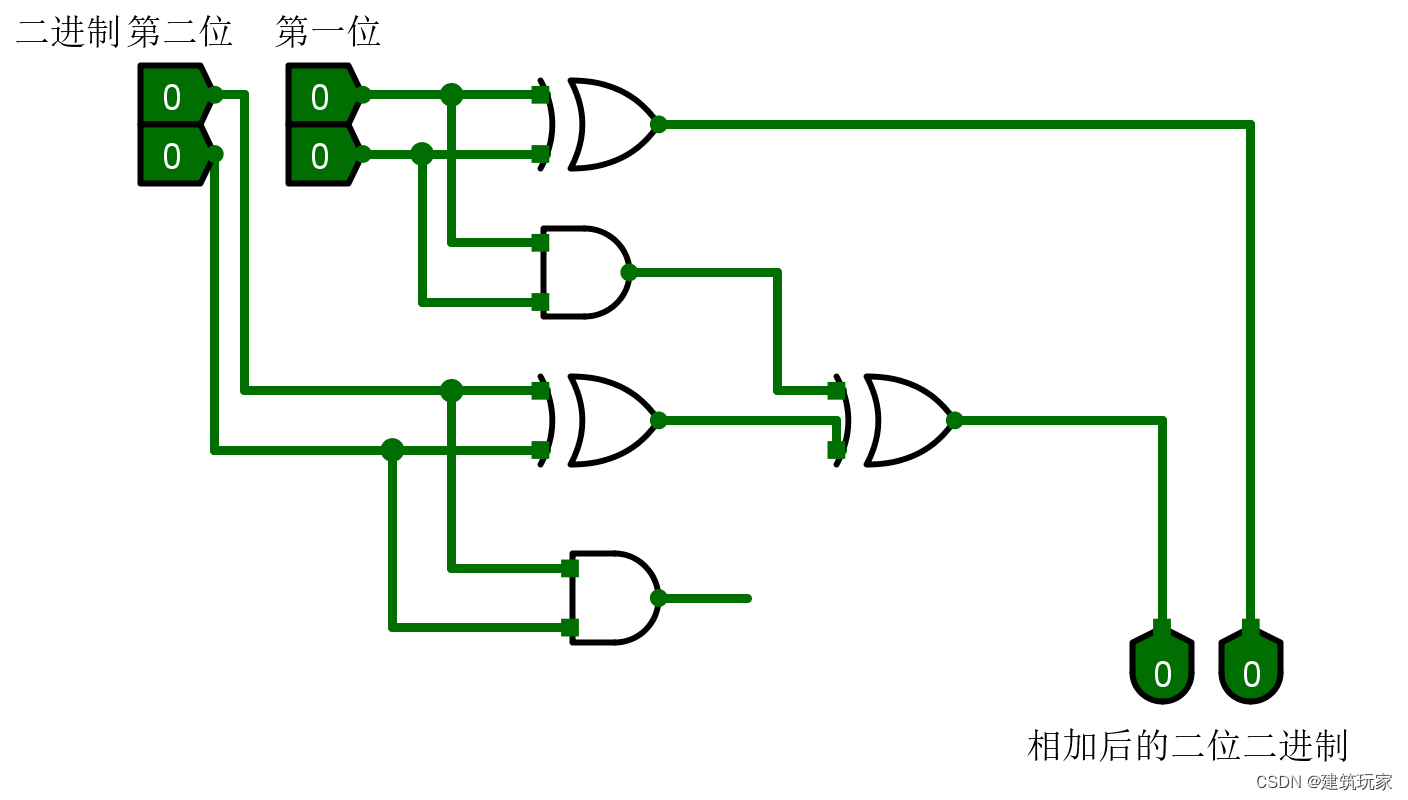

下图为logisim生成的一位全加器

可以看出,两者差别不大

4bit全加器

module full_adder_4bit (

input [3:0] A, B,

input Cin,

output [3:0] S,

output Cout

);

wire c0, c1, c2;

wire s0, s1, s2, s3;

assign s0 = A[0] ^ B[0] ^ Cin;

assign c0 = (A[0] & B[0]) | (A[0] & Cin) | (B[0] & Cin);

assign s1 = A[1] ^ B[1] ^ c0;

assign c1 = (A[1] & B[1]) | (A[1] & c0) | (B[1] & c0);

assign s2 = A[2] ^ B[2] ^ c1;

assign c2 = (A[2] & B[2]) | (A[2] & c1) | (B[2] & c1);

assign s3 = A[3] ^ B[3] ^ c2;

assign S = {s3, s2, s1, s0}; // 组合4位求和信号

assign Cout = c2; // 输出进位信号

endmodule其电路图如下

可以跟logisim做出来的4bit全加器作对比

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?