最近因为需要使用到LPDDR5,快速地浏览了JEDEC标准文档,发现与前几代相比出现了一些新的电路设计功能,总结为如下三点:

1. CK/WCK/RDQS时钟方案;

2. 电源的PDN设计目标;

3. DQ, DMI和RDQS的Rx端DFE均衡技术。

本文就上述三种新功能进行了简述。

CK/WCK/RDQS时钟方案

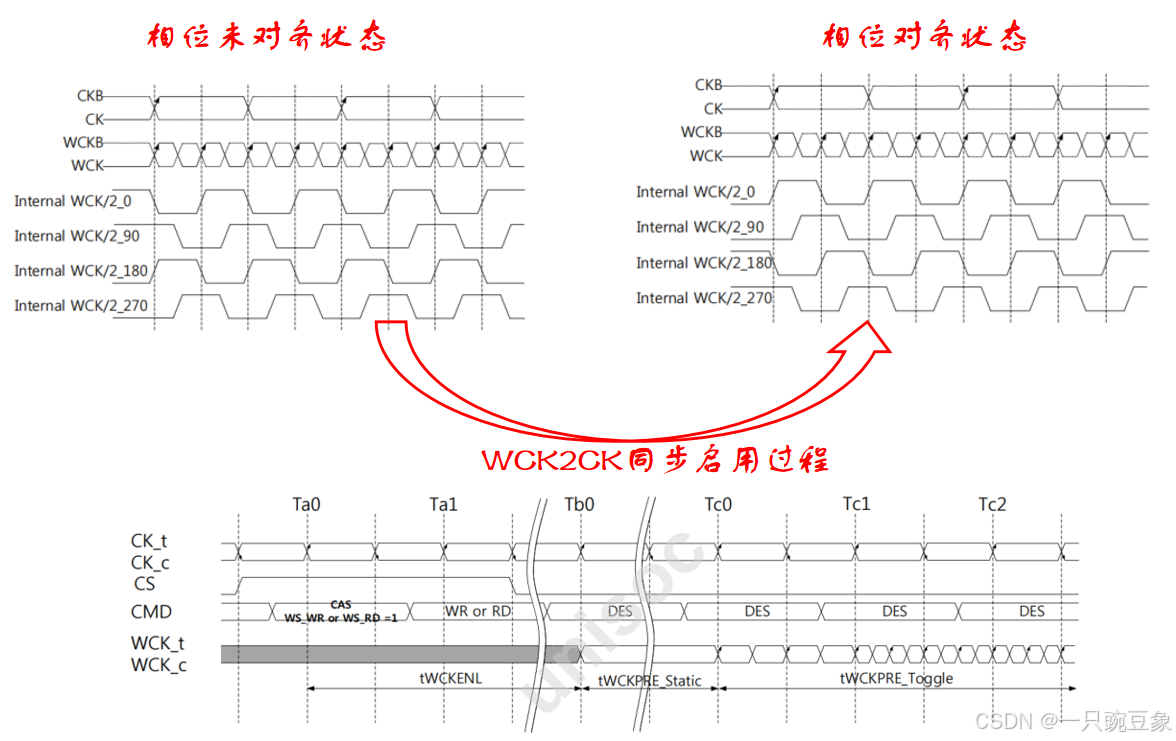

LPDDR5 SDRAM采用两种不同频率的时钟:WCK的频率是CK时钟频率的四倍或两倍,但是,为了实现无差错延迟控制,SDRAM内部的时延控制单元必须知道WCK是否与CK状态对齐。为此,LPDDR5 SDRAM通过一个称为WCK2CK同步的过程重置或检测其对齐状态,当控制器发出带有WCK2CK同步位的CAS命令时,控制器向SDRAM提供半频WCK脉冲来减缓码间干扰(ISI)以提高时间裕度,从而降低相位对齐的难度,该操作定义为“WCK2CK Synchronization”,对应的读写操作也产生了一些新的变化。

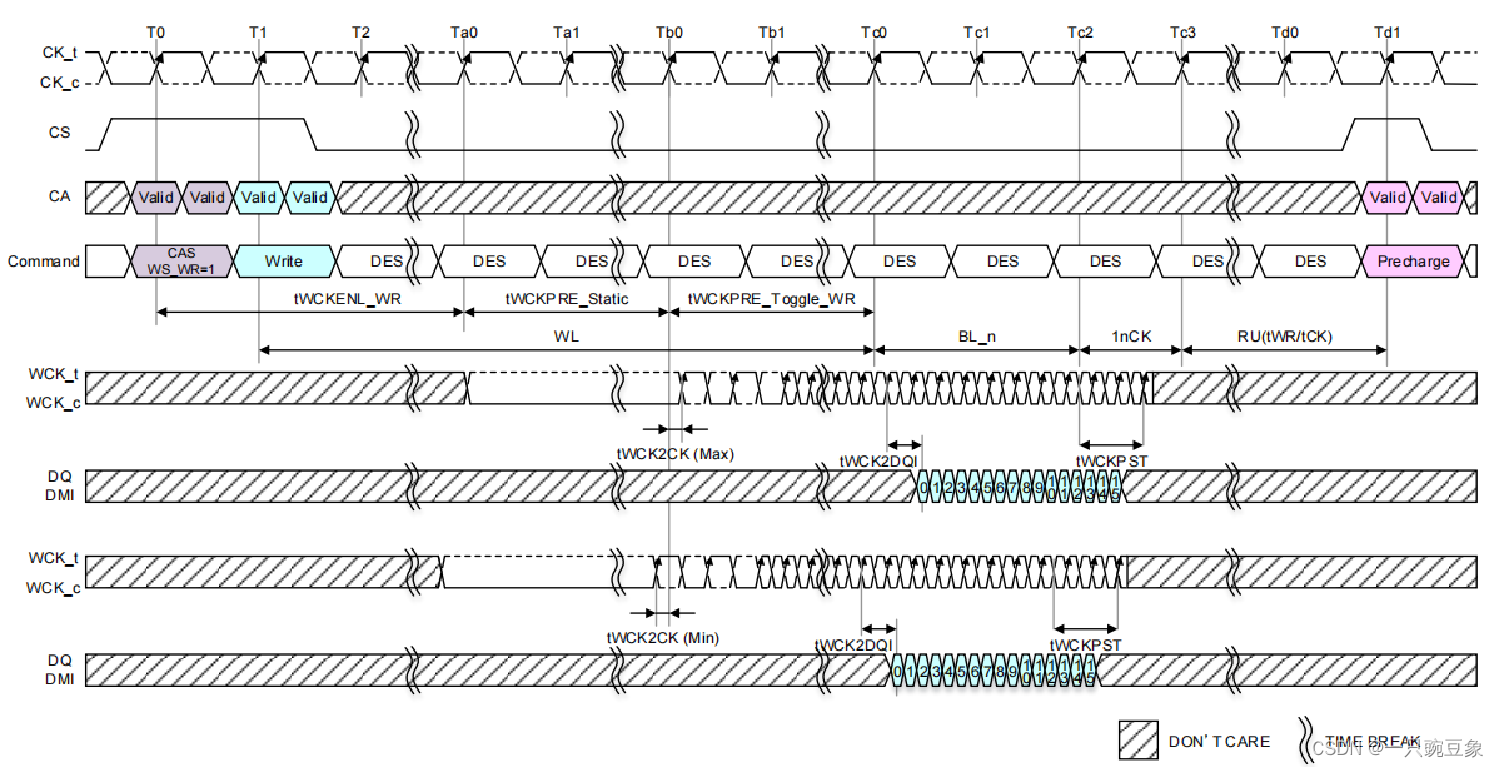

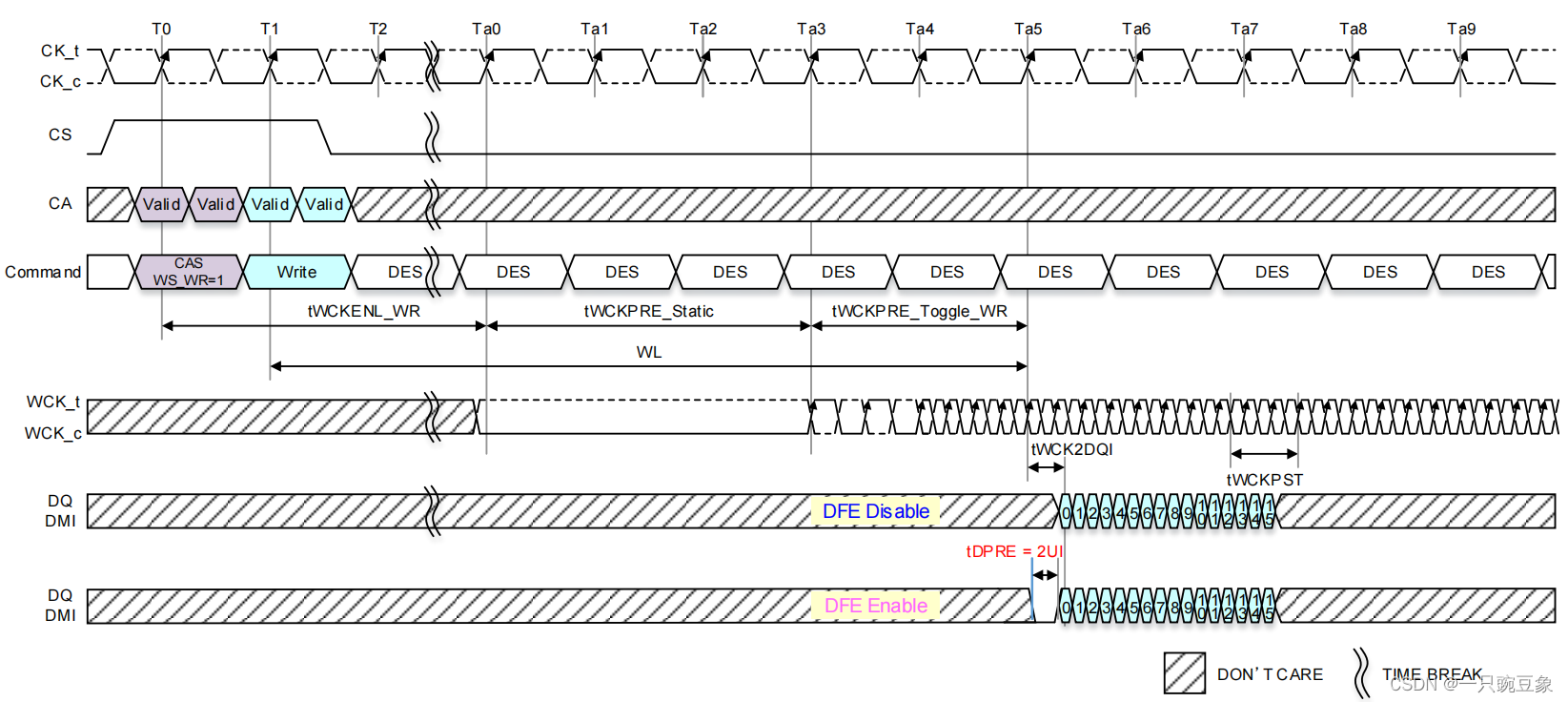

如下图所示,写操作仍然由CS发起,CA总线在CK的双边沿完成采样,WCK的第一个有效的“锁存”边必须在完成写命令的CK_t上升沿之后再驱动WL * tCK + tWCK2CK,其中,写延迟(WL)被定义为从启动写命令的CK_t的上升沿到测量tWCK2DQI的CK_t的上升沿。

另外,WCK必须在tWCK2DQI的时间步长之前到达SDRAM球,WCK由SDRAM控制tWCKPRE_Static+tWCKPRE_Toggle_WR时间量后在第一个有效的上升沿之前被驱动。

换句话说,写操作中,CS和CA由CK进行采样,DQ由WCK进行采样。

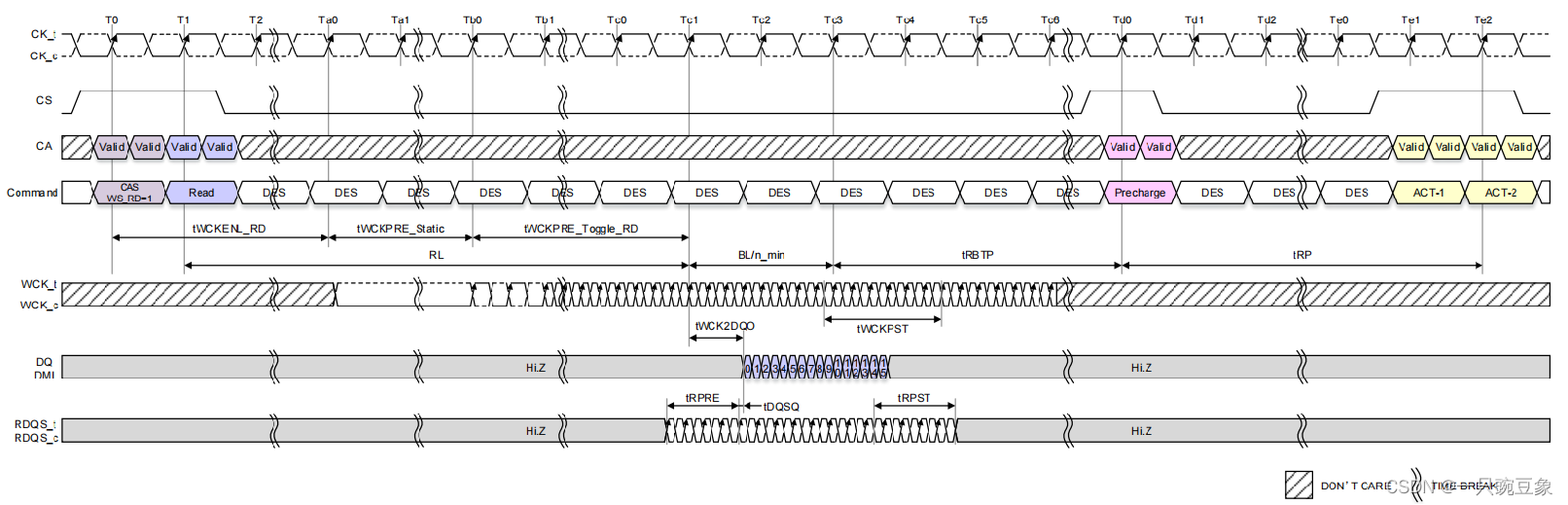

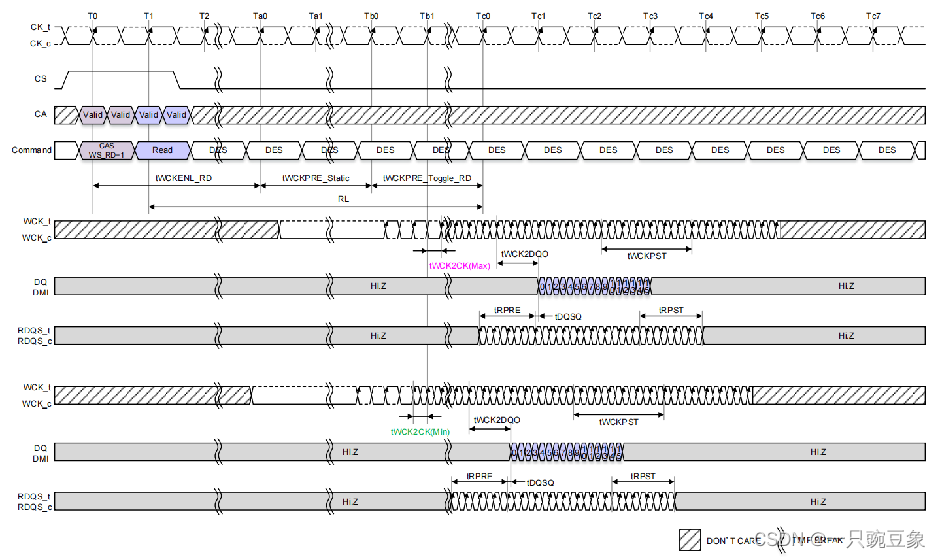

读操作有两种方式:

在读命令的CK_t上升沿之后,经过RL * tCK + tWCK2CK + tWCK2DQO的时间量后的第一个有效DQ数据可用,其中,读延迟(RL)定义为从启动读命令的CK_t的上升沿到测量(tWCK2CK + tWCK2DQO)后的CK_t的上升沿,WCK在第一个有效的读数据开始之前,由SDRAM控制器经过tWCKPRE_Static+tWCKPRE_Toggle_RD时间量后被驱动。

在高时钟频率下工作,可以将LPDDR5 SDRAM设置为RDQS模式,此模式下,读指令的时钟将由RDQS差分端口提供。启用RDQS模式时的读取时序如下图所示,除了额外的RDQS计时外,所有的计时都与前述的READ操作相同。 RDQS相关的参数:tDQSQ, tRPRE and tRPST,RDQS的第一个锁存边将迟于第一个有效DQ数据,具有“tDQSQ”延迟,tDQSQ是LPDDR4中的已知参数。RDQS需要在第一个锁存边(具有第一个有效数据的RDQS的上升边)之前预发送,并且在最后一个锁存边之后需要进行持续发送。前同步(tRPRE)和后同步(tRPST)时间长度定义为可以通过模式寄存器写(MRW)设置的参数。

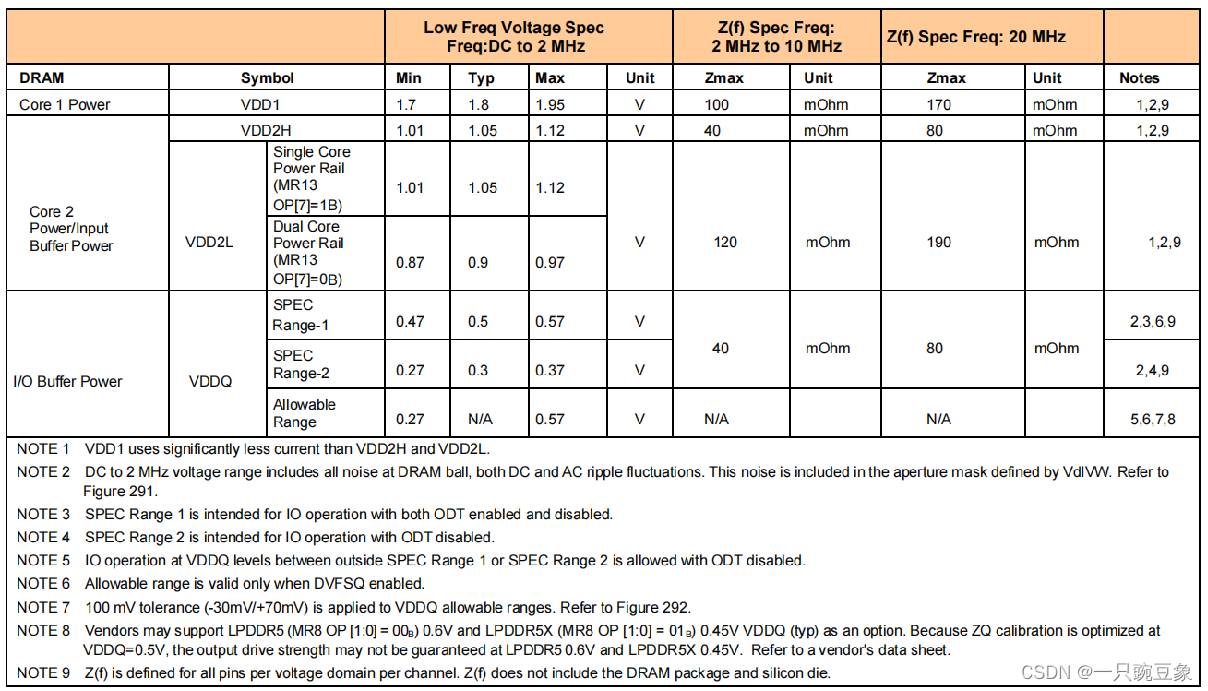

电源的PDN设计目标

这一代DDR首次引入了PDN的设计要求,可见,速率的提升必然带来电源纹波的激增,不过从其数据手册中,可以发现阻抗动态频率范围最高要求到20MHz,这还是板级SMT电容可以控制的范围,设计难度处于中等,难点可能出现在电容的数量和BGA区域的摆放空间。

Rx端DFE均衡技术

LPDDR5支持6400Mbps以上的数据速率,为了补偿通道特性,首次采用了Rx端的均衡技术,可以支持到DQ, DMI和RDQS。当WCK高于800MHz时,DFE就可以启用。LPDDR5为DQ Rx提供了反馈判决均衡(DFE)功能,支持1抽头负反馈,通过寄存器配置可以为每个字节支持不同的反馈量。 DFE是一个可选特性,如下图所示,在写数据突发操作之前,启用DFE之前需要2UI DQ预驱至0(tDPRE),这种预驱动设置是DFE电路的前置条件。

参考文献

JEDEC JESD209-5C

263

263

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?