原理介绍:

要将27MHz(27*10^6)分频为1Hz,需要使用一个25位的计数器(lpm_counter)。每个时钟周期,计数器将增加1,直到达到2^25-1(即33554431)(刚好可以算到27*10^6),然后重新开始计数。当计数器达到特定值时,可以触发一个输出信号。还需要一个25位输入的数值比较器(lpm_compare)这个是来判断信号是否达到1s。

一、器件介绍

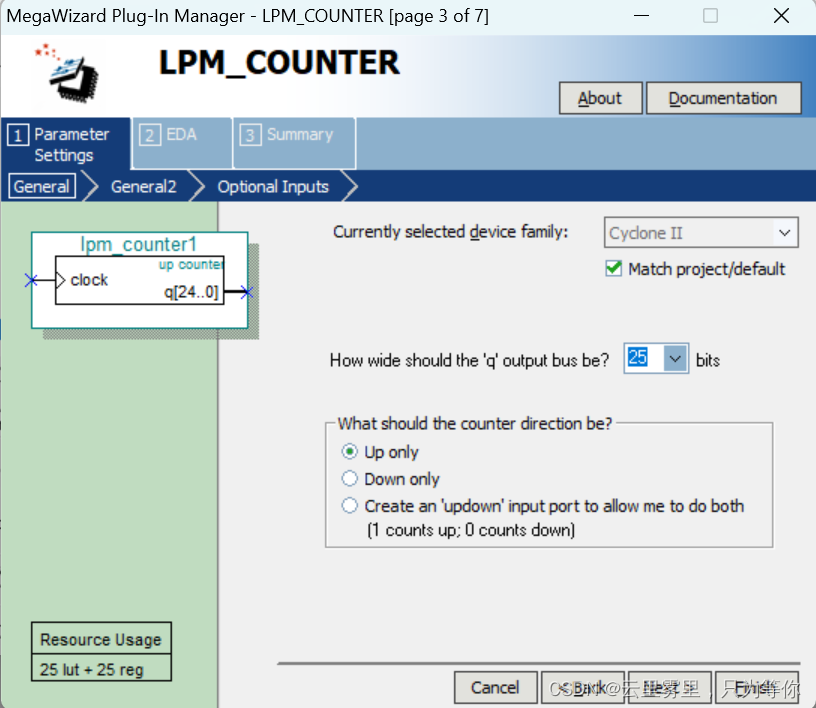

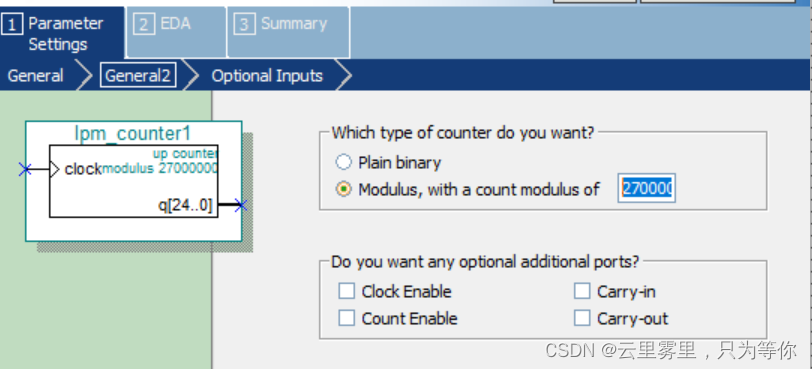

25位计数器(lpm_counter)设置如下:

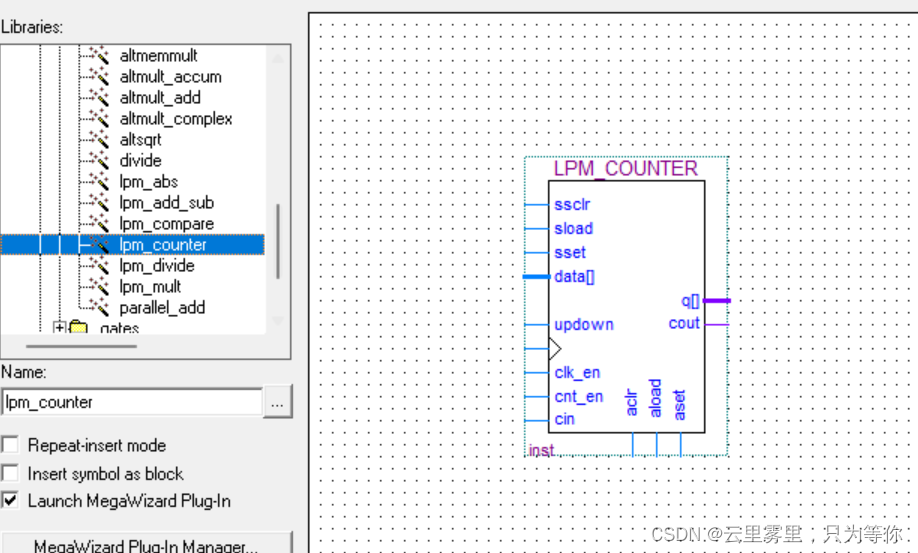

找到相应器件:

设置25位bits:

设置计数目标(27000000):

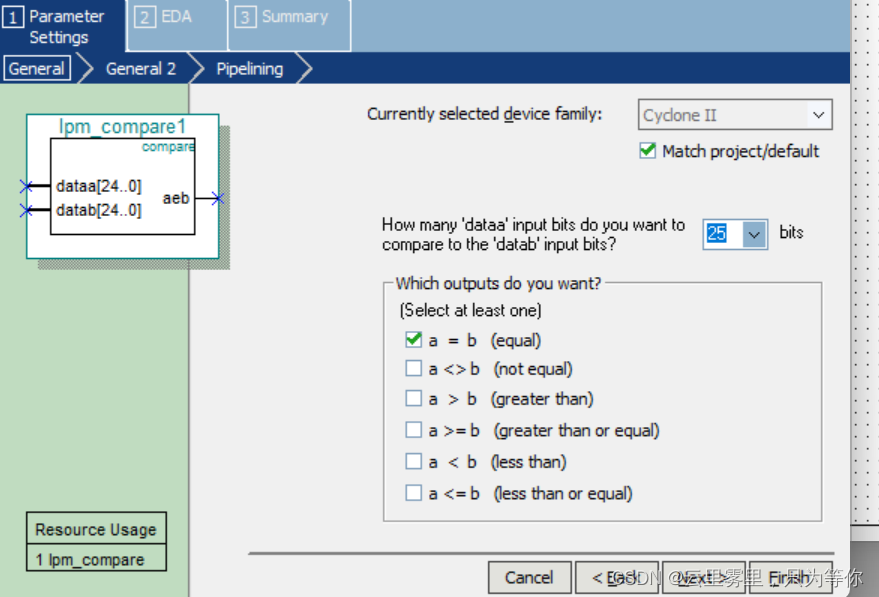

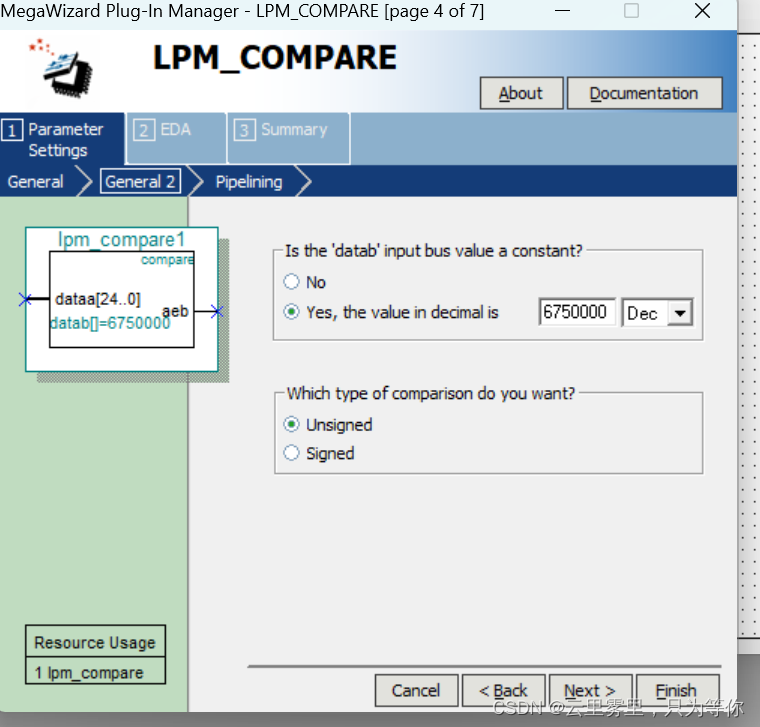

25位的数值比较器(lpm_compare):

找到相应器件:

设置25位bits和a=b判断条件:

设置比较目标(参数6750000)(切记不是27000000):

没提到的步骤选“Next”,最后“Finish”。

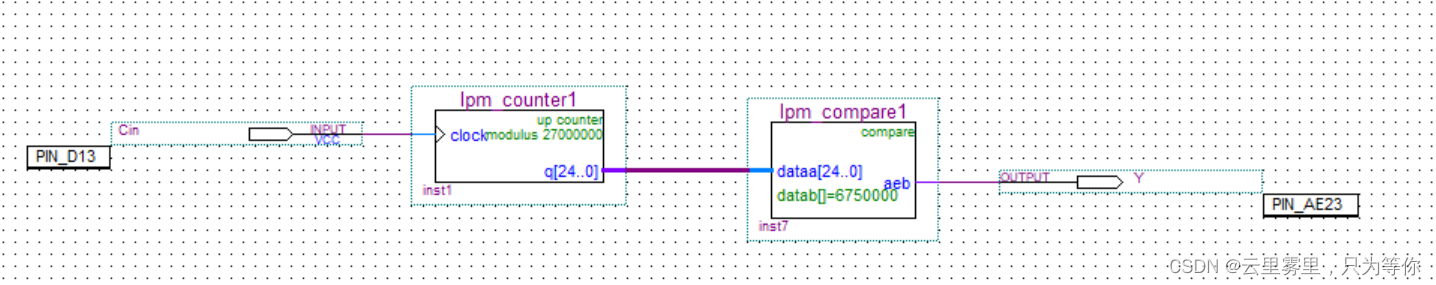

二、电路图演示(左边是计数器,右边为比较器):

其中输入引脚绑定了27MHz的时钟信号,输出结果绑定了SW[0]的灯泡。

三、注意

仿真时,因为未做一些参数调整,有可能结果是固定的值,原因是仿真时波形图是纳秒级别的与1s相差过远,所以结果为0(不变)。只有烧录时才能正常显示。因为只是单纯分频信号故结果展示不是很明显。这章主要是配置,下一章出一个案例(用D触发器实现8进制计数器)。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?