基于Xilinx的数据手册pg007_SRIO的P1-55、P73-83得到以下SRIO接口知识:

SRIO(Serial RapidIO,串行RapidIO)是一种用于高速差分串行通信协议。

(1)SRIO Gen2支持 1 路、2 路和 4 路(1x、2x、4x,“x”表示通道数,选择几lane,几组差分线,几个高速收发器通道)通道传输数据(选择lane的宽度,要考虑板子底层差分线数量是否支持)

(2)SRIO Gen2每个通道(per lane)传输速度支持 1.25、2.5、3.125、5.0 和 6.25 Gbaud

(3)SRIO Gen2使用简单的握手机制控制 AXI4-Stream接口进行高吞吐量数据传输,使用 AXI4-Lite接口进行配置、维护(联想到以太网的MAC核)

(4)SRIO Gen2兼容A7板卡,A7高速收发器是GTP,最大线速6.6Gbit/s,故SRIO Gen2通道最大速度是6.25Gbaud(木桶效应)

板间高速差分通信GTX---GTH,木桶效应,按照GTX(慢的)算

(5)SRIO(发数据和中断)用途:

1. FPGA与DSP进行通信

2. 含有高速收发器的俩板子//芯片(片间板间)进行通信,可以使用SRIO,但此方法并不是最优解

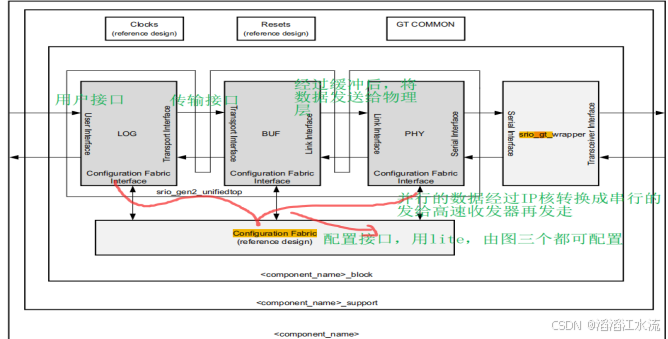

(6)SRIO Gen2 分三层:逻辑层、缓冲层、物理层

逻辑层:逻辑层定义整体协议和数据包格式。

缓冲层:接收发送缓存的包深度(8/16/32,通常默认或最大)

SRIO系统传输框架:

SRIO分三层:逻辑层、缓冲层、物理层;通过用户接口,以AXI4-stream形式将数据传送到逻辑层,再将数据通过传输接口送到缓冲层,之后将数据传到物理层,最后通过GT高速收发器将数据串行发送出去:

(1)框图左边用户接口以I/O Port形式进行传输,框图右边收发器接口以差分串行高速收发器形式进行传输

(1)每个SRIO IP核的物理层数据通过1个高速收发器(1个高速通道)串行输出,高速收发器通道由1个GT COMMON(QPLL)提供时钟

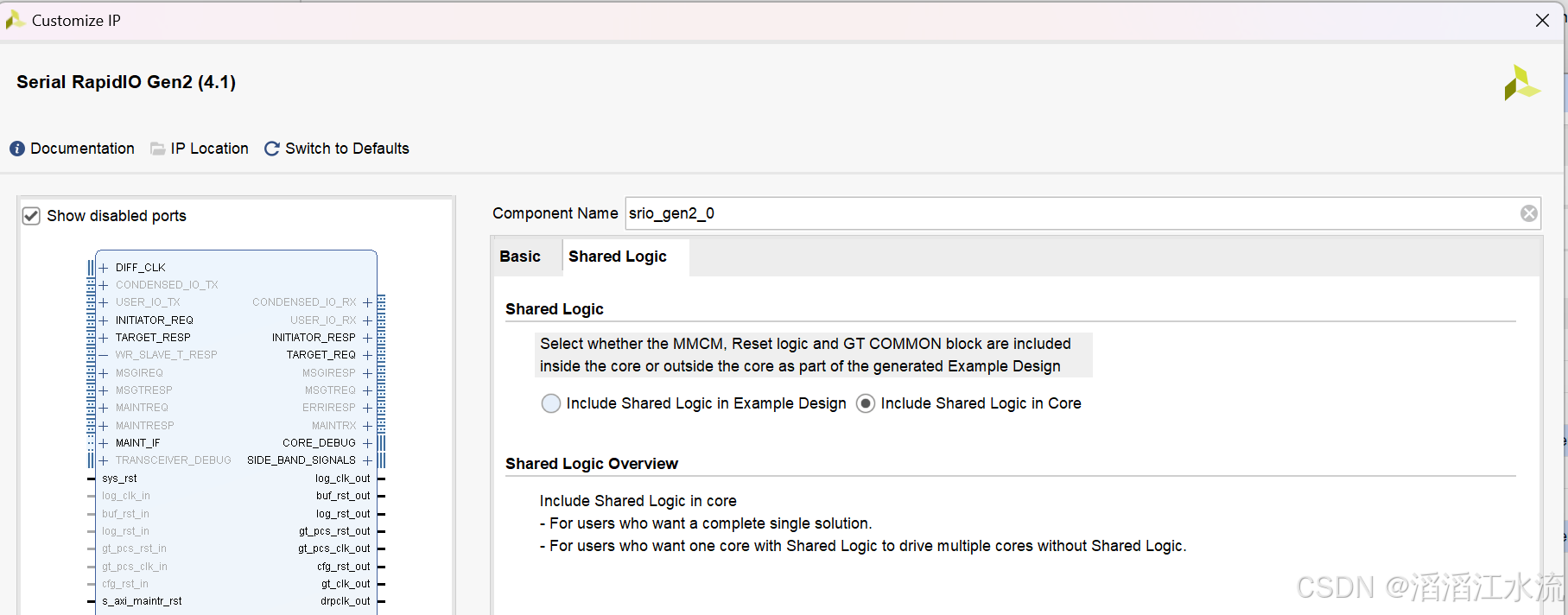

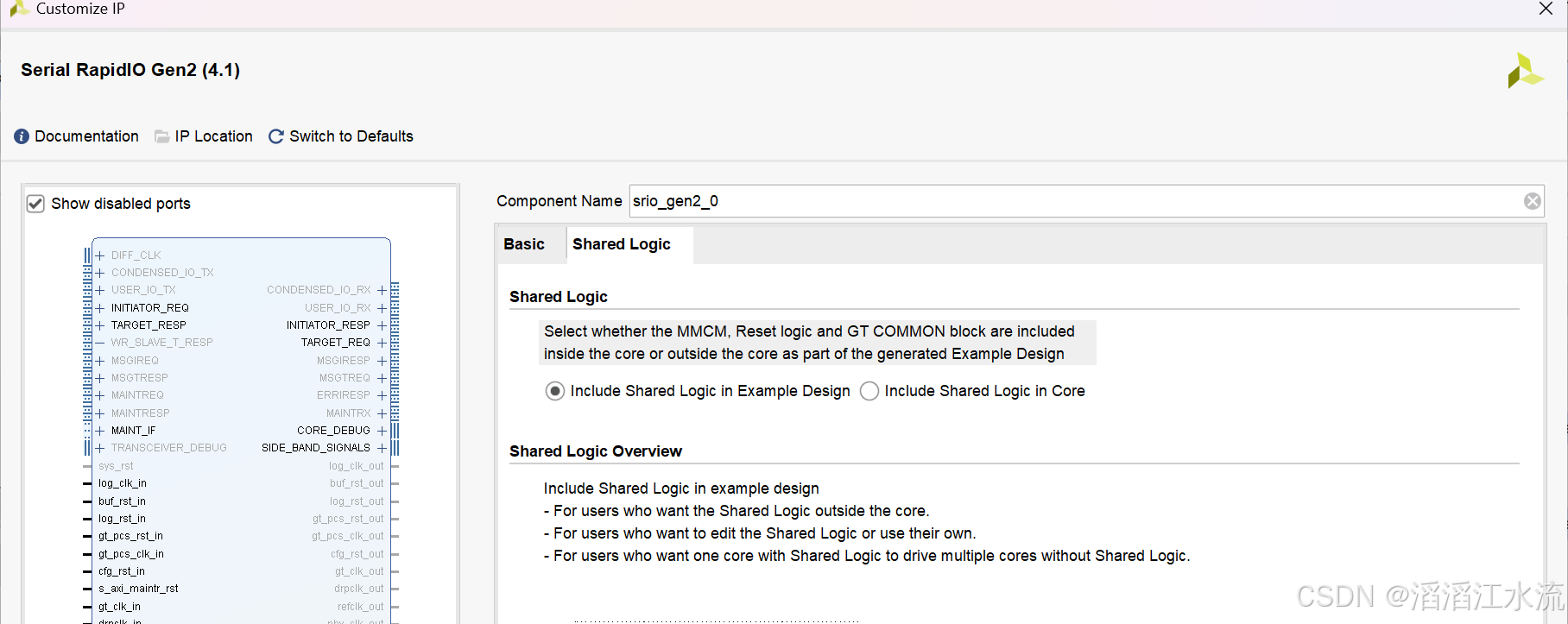

(2)1个GT Quad里面只有1个QPLL,只能给一个高速收发器通道提供时钟,若多个高速收发器通道都调用SRIO IP核,就需要多个QPLL驱动,这时就需要共享逻辑资源:

①共享资源实现:其中一个IP核包含共享逻辑资源(共享资源端),其它IP核不包含共享逻辑资源(被共享资源端),将共享IP的输出端连接被共享IP的输入,为其提供逻辑资源

②共享资源设置步骤:

在调用SRIO IP核时,选择“Include Shared Logic in Core”为共享资源端

选择“Include Shared Logic in Example Design”为被共享资源端

SRIO传输接口叙述:

1、用户接口传输情况:

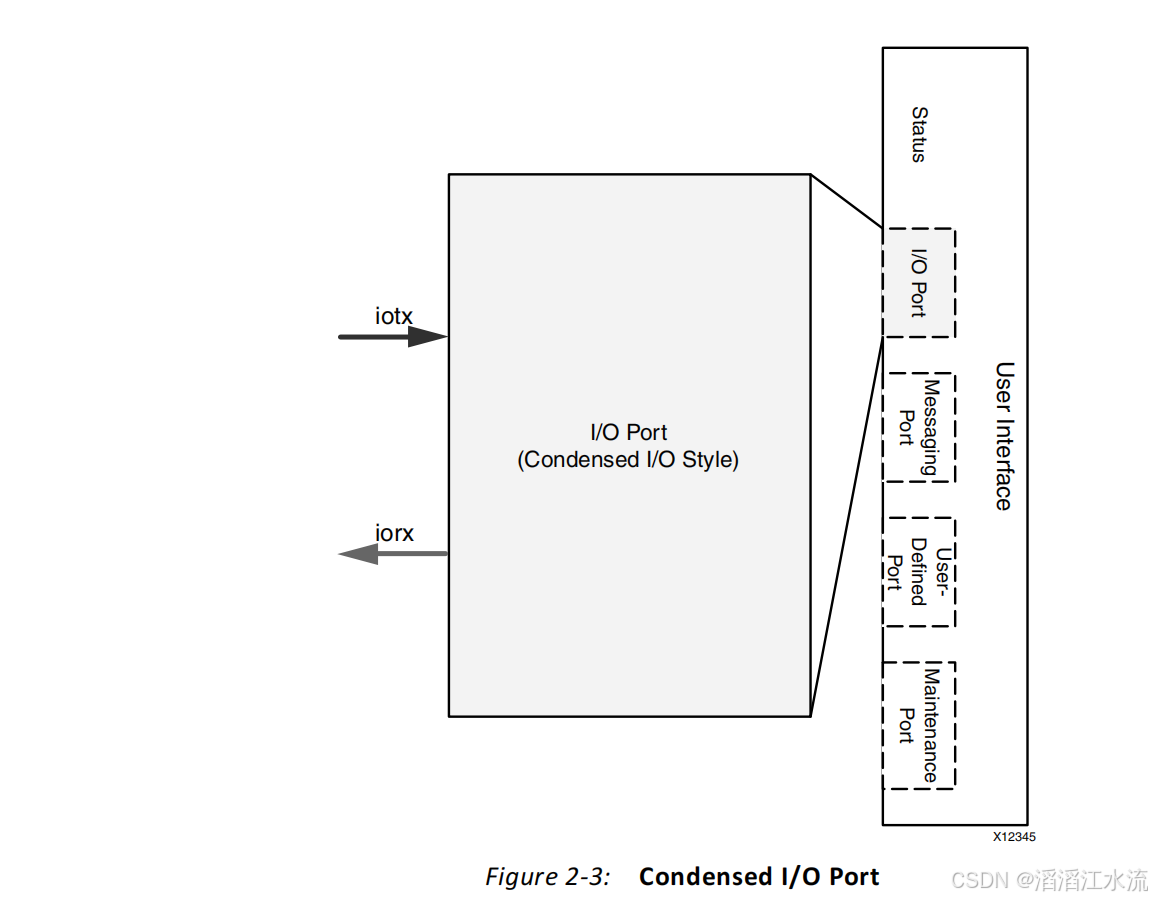

(1)逻辑层用户接口主要通过I/O Port 进行数据传输

①maintr、cfgr、cfgl:使用AXI4-Lite接口,管配置和维护

②I/O Port、消息端口、用户自定义端口使用AXI4-stream协议

(2)I/O Port有两种类型:收发、带应答(默认I/O Port带应答)

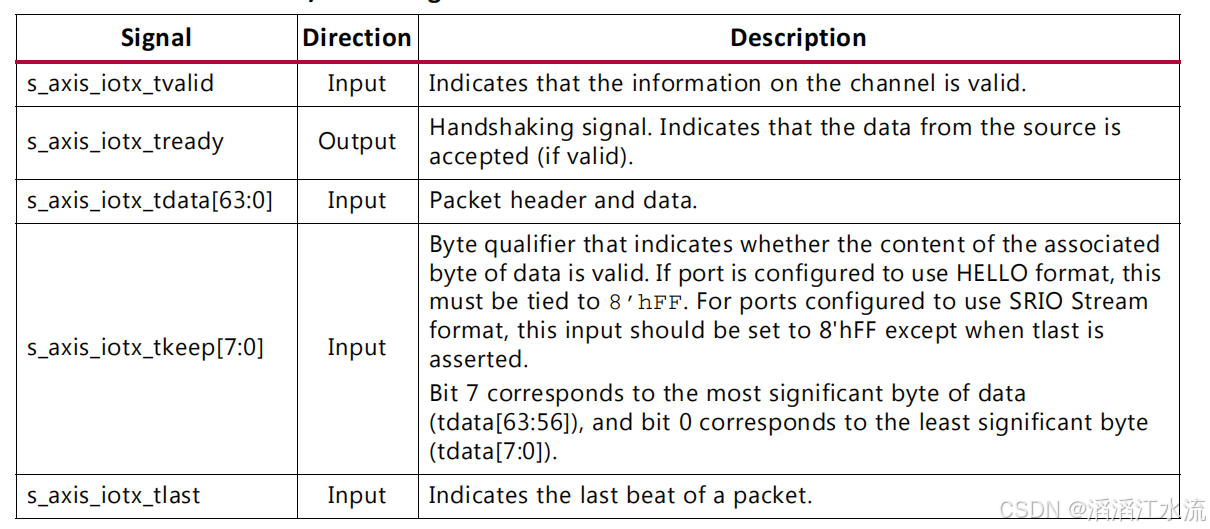

I/O Port引脚说明:(使用AXI4-stream协议,引脚相似)

①发送引脚iotx:

• s_axis_iotx_tvalid(我提供)和s_axis_iotx_tready(SRIO IP核提供)组成握手信号

• s_axis_iotx_tdata[63:0]:64位数据线,握手后,数据有效

• s_axis_iotx_tkeep[7:0]:选通信号,每1bit对应data的1字节(data : keep位宽 8:1)

• s_axis_iotx_tlast:最后突发数据标志,拉高

• s_axis_iotx_tuser[31:0]:用户自定义,一般不用,用在一个SRIO向多从传输时(扇出时),通过ID(器件ID,16bit)进行选择传输

HELLO格式:由源 ID (31:16) 和目标 ID (15:0) 组成

SRIO stream格式:tuser 只有 8 位宽

②接收引脚iorx:(同理)

• m_axis_iorx_tvalid(数据发送方SRIO IP核提供),m_axis_iorx_tready(数据接收方我提供)

(3)两种传输数据包格式:

• HELLO (精简包,不是一种包格式,里面还包含许多包格式)

• SRIO Stream(标准包,结构复杂)

2、收发器接口传输情况:

(1)高速收发器包括一个发送器TX和一个接收器RX

(2)收发器接口引脚:

• srio_rxnN和srio_rxpN:一对差分的高速串行输入引脚

• srio_txnN和srio_txpN:一对差分的高速串行输出引脚

• 命名规则:rx输出,tx输入;p和n指差分的两条正、负线;N指第几lane

(3)收发器接口时钟信号(gt_clk),时钟速率基于内核的传输频率:

3、串行接口传输情况:

串行接口的时钟信号(gt_pcs_clk),时钟速率基于内核的传输频率,是gt_clk的一半:

对于高速收发器,区分串行接口和收发器接口:

串行接口:主要用于传输数字信号,它定义了数据的格式、速率、时序等。

收发器接口:主要与传输介质进行数据传输,包括信号的调制、解调、放大、滤波等。

HELLO包具体数据格式:

(1)HELLO包分为许多事务类型:(由FTYPE/TTYPE决定)

①NREAD:基础读取请求事务,带响应(0010/0100)

②NWRITE:基础写操作包,不带响应(0101/0100)

③NWRITE_R:带响应的的写操作包(0101/0101)

④SWRITE:不带响应的连续写操作(0110/----)

⑤DOORBELL:门铃包、中断包(1010/----)

(2)HELLO包:

①HELLO包包长64bit(8Byte)

②HELLO 包最大净荷量(最大传输数据量):256字节(传输范围为 0 - 255)

③事务类型相当于包头(车头)

③我们使用的是NWRITE和DOORBELL

• NWRITE包头后跟数据(这车载货)

•OORBELL包头后不跟数据(这车不载货)

(3)HELLO包的包格式:

• TID:数据包的事务 ID

• FTYPE/TTYPE:各4bit,FTYPE和TTYPE两条线控制事务类型选择

• priority:2bit,数据包的优先级

• CRF:1bit,包响应,用时置1

• size:8bit,决定包长度、净荷量(范围0 - 255,最大传输256字节数据)

• addr:地址

• R:R保留位

• info:表明不是数据包,是中断包

①NWRITE包叙述:(DOORBELL构成要知道,NREAD/SWRITE要了解)

主要有8bit的ID、4bit的FTYPE和4bit的TTYPE共同决定了它的事务类型、8bit的净荷量(0-255字节)、34bit的地址,剩下还有3bit的保留位,1bit响应,2bit优先级

②DOORBELL包:中断包,先有数据再有中断,先发NWRITE包,再发DOORBELL包

FPGA---DSP传输机制:

FPGA先发包头NWRITE+size个字节数据,之后发DOORBELL(不跟数据)进行中断,告诉DSP现在处理刚发来的数据

SRIO使用AXI4-stream发送数据相比AXI4-stream接口区别:

SRIO需要先发个包头(事务类型)----(这里只说数据格式上的区别)

包头后面若能跟数据(如:HELLO包的NWRITE),数据最大能传输256个字节长度,不是无限制的;

其他的呢,在这儿呢

SRIO的板间远端回环和单板近端回环:

(1)1个板子近端回环,我们使用的是近端回环,1个板子调2个SRIO IP核自己和自己发

1个板子回环过程:数据生成模块APP使用AXI4-stream协议发送HELLO数据包到SRIO1 IP核,在SRIO1 IP核将数据包转化成高速收发器接口的形式发送到SRIO2 IP核,在SRIO2 IP核对包进行解析,以AXI4-stream接口形式发送到APP,形成回环

(2)2个板子远端回环:

2个开发板进行回环:每个板子都调用1个SRIO IP核,板内部通过SRIO用户接口以AXI4-stream形式与数据模块进行交互,两板之间通过高速收发器进行传输,通过SRIO选择的lane的个数(1x、2x、4x),使用对应个数的高速收发器进行传输

SRIO时序:

(1)I/O Port:AXI4-stream协议,在握手机制有效下,写NWRITE事务和DOORBELL事务

①NWRITE事务:先发64bit包头后跟数据(最大限制256字节,数据最后last拉高)

②DOORBELL事务:只发64bit中断包(last拉高)

(2)维护端口:AXI4-Lite协议,上写入事务的示例

SRIO程序信息:(默认I/O Port带应答,我们用的是不带应答机制的包类型)

需要经过初始化:

SRIO有2个初始化信号:

①port_initialized(用户端口,端口初始化,快些)

②link_initialized(整条传输通道(链路)的初始化,慢些)

当2个初始化都完成后,初始化信号都有效(高电平有效)后,才能进行传数

TEST_DATA_SEND.v文件:造了个NWRITE包

SRIO_TOP_LOOP.v是顶层文件

TB文件主要模拟将2个SRIO IP核外部的高速收发器的线连接在一起

调用SRIO IP核步骤:

选择模式,我们使用的是基础模式

(1)基础模式下,选择lane数量,传输速率,时钟频率,器件ID等

(注意:时钟频率指的是收发器接口时钟频率,要和lane的传输速率匹配)

选择此SRIO IP核是共享资源端还是被共享资源端

(2)自定义模式下,各层信息可以手动配置选择

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?