1、概述

1.1起源

在SRIO出现之前,PC架构中只有一个中央处理器CPU,其他所有设备均为从,数据传输等进程只能CPU发起,其拓扑结构为典型的星状结构。但是随着嵌入式的发展,DSP\FPGA\CPU\GPU\PowerPC等嵌入式处理器出现之后,多个模块通过背板互联,各处理器完成各自任务,之间又通过背板相互联系,就出现了多主的情况,传统的PCI和PCIX总线就满足不了嵌入式设备使用了。

于是由Motorola\Mercury\TI\Intel\Xilinx等厂商成立了RapidIO TradeAssociation组织,并在2001年推出基于多个LVDS通道并行了RapidIO(也叫SRIO,serial RapidIO)。2014年推出了3.1版本。

1.2特点

- 每条lane最高支持10.3125Gbps,速率可裁剪,支持1.25、2、3.125、5、6.25、10.3125Gbps.

- 支持8B/10B、64B/67B编码方式;

- 支持动态非堆成通讯模式,比如发送防线为4X,接收可以是1X或者其他。

- DeviceID扩展到了32为,可以增加啊节点。所有发送数据包支持source ID可配置;

- 支持1x、2x、4x,并且可以从x4、x2向下train down;

- 支持同时发生的Initiator和Target接口操作;

- 支持Doorbell传输和Message传输;

- 使用标准的AXI4-Lite和AXI4-Stream接口实现简单的握手机制和数据流控制

- TXbuffer和RX buffer深度独立可配置,可配置深度分别为8包、16包和32包;

- 支持TX flow control和RX flow control;

- 支持multi-cast传输;

- 支持3C连接(Chip-Chip\Card-Card\Chassis-Chassis);

1.3选择原因

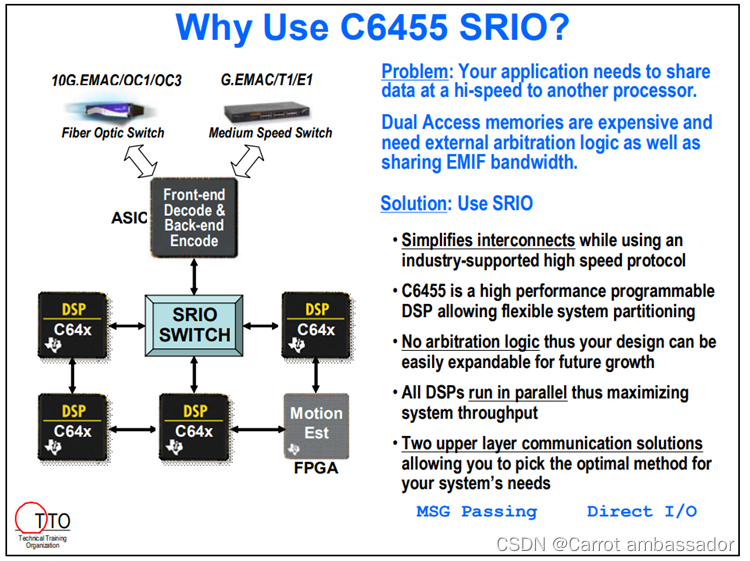

如下图为TI的DSP选用SRIO的原因;

如下图为Xlinx FPGA选择SRIO的原因。

如下图为Xlinx FPGA选择SRIO的原因。

2、SRIO协议

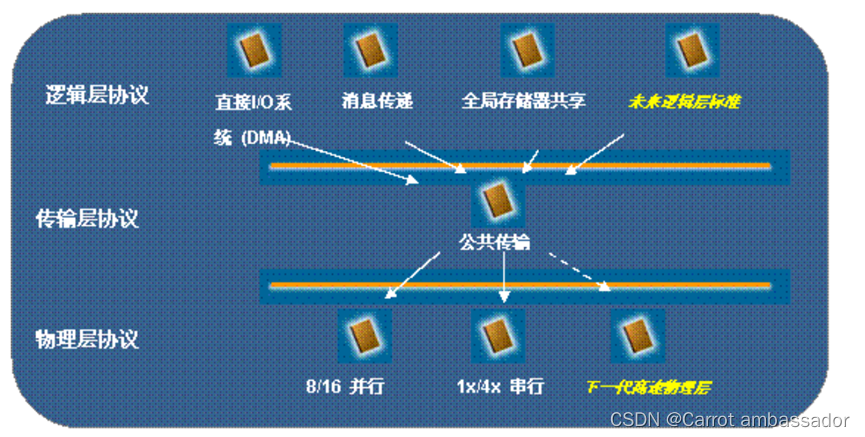

为了满足灵活性和可扩展性的要求,RapidIO协议分为三层:逻辑层、传输层和物理层。图2说明了RapidIO协议的分层结构。

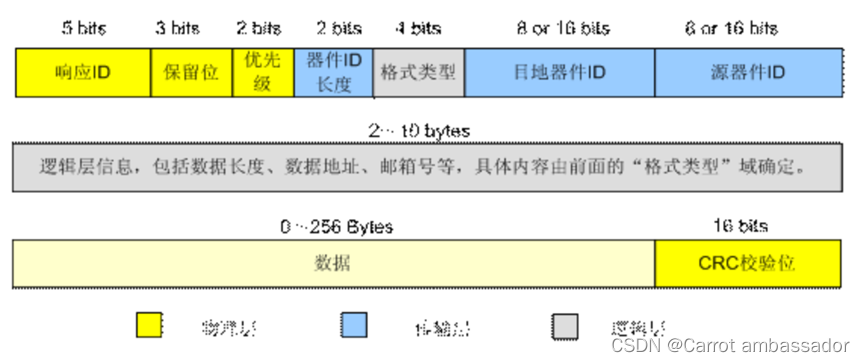

逻辑层定义了操作协议; 传输层定义了包交换、路由和寻址机制;物理层定义了电气特性、链路控制和纠错重传等。像以太网一样,RapidIO也是基于包交换的互连技术。如图3所示,RapidIO包由包头、可选的载荷数据和16bits CRC校验组成。包头的长度因为包类型不同可能是十几到二十几个字节。每包的载荷数据长度不超过256字节,这有利于减少传输时延,简化硬件实现。

上述包格式定义兼顾了包效率及组包/解包的简单性。RapidIO交换器件仅需解析前后16bits,以及源/目地器件ID,这简化了交换器件的实现。

2.1逻辑层协议

逻辑层定义了操作协议和相应的包格式。RapidIO支持的逻辑层业务主要是:直接IO/DMA (Direct IO/Direct Memory Access)和消息传递(Message Passing)。

直接IO/DMA模式是最简单实用的传输方式,其前提是主设备知道被访问端的存储器映射。在这种模式下,主设备可以直接读写从设备的存储器。直接IO/DMA在被访问端的功能往往完全由硬件实现,所以被访问的器件不会有任何软件负担。从功能上讲,这一特点和德州仪器DSP的传统的主机接口(HPI, Host Port Interface)类似。但和HPI口相比,SRIO(Serial RapidIO)带宽大,管脚少,传输方式更灵活。

对上层应用来说,发起直接IO/DMA传输主要需提供以下参数:目地器件ID、数据长度、数据在目地器件存储器中的地址。

直接IO/DMA模式又可进一步分为以下几种传输格式:

- NWRITE: 写操作,不要求接收端响应。

- NWRITE_R: 带响应的NWRITE(NWRITE with Response),要求接收端响应。

- SWRITE:流写(Stream Write),数据长度必须是8字节的整数倍,不要求接收端响应。

- NREAD: 读操作。

SWRITE是最高效的传输格式;带响应的写操作或读操作效率则较低,一般只能达到不带响应的传输的效率的一半。

消息传递(Message Passing)模式则类似于以太网的传输方式,它不要求主设备知道被访问设备的存储器状况。数据在被访问设备中的位置则由邮箱号(类似于以太网协议中的端口号)确定。从设备根据接收到的包的邮箱号把数据保存到对应的缓冲区,这一过程往往无法完全由硬件实现,而需要软件协助,所以会带来一些软件负担。

对上层应用来说,发起消息传递主要需提供以下参数:目地器件ID、数据长度、邮箱号。

下表比较了直接IO/DMA和消息传递模式。

2.2传输层协议

RapidIO是基于包交换的互连技术,传输层定义了包交换的路由和寻址机制。

RapidIO网络主要由两种器件,终端器件(End Point)和交换器件(Switch)组成。终端器件是数据包的源或目的地,不同的终端器件以器件ID来区分。RapidIO支持8 bits 或 16 bits器件ID,因此一个RapidIO网络最多可容纳256或65536个终端器件。与以太网类似,RapidIO也支持广播或组播,每个终端器件除了独有的器件ID外,还可配置广播或组播ID。交换器件根据包的目地器件ID进行包的转发,交换器件本身没有器件ID。

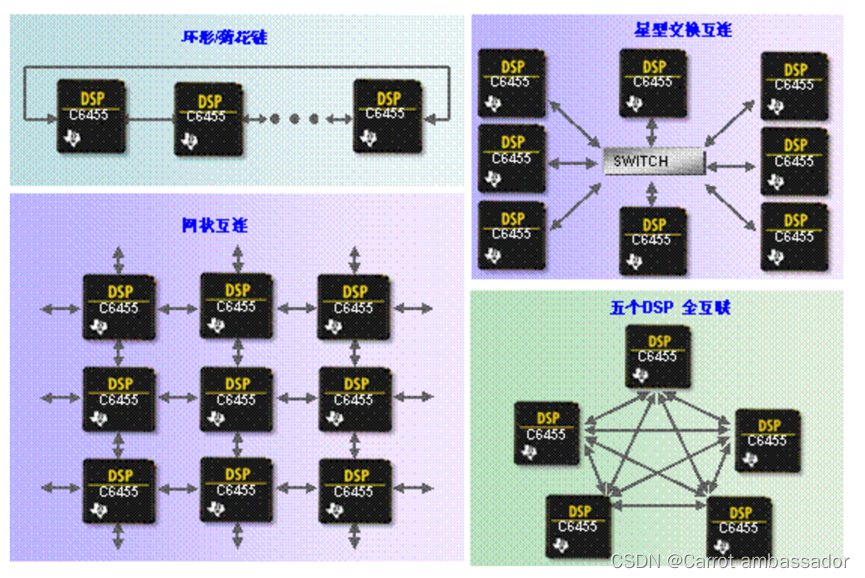

RapidIO的互连拓扑结构非常灵活,除了通过交换器件外,两个终端器件也可直接互连。以德州仪器(TI)的TMS320C6455 DSP为例,它有4个3.125G的SRIO口,它可支持的拓扑结构如图所示。

2.3物理层协议

RapidIO 1.x 协议定义了以下两种物理层接口标准:

- 8/16 并行LVDS协议

- 1x/4x 串行协议 (SRIO)

并行RapidIO由于信号线较多(40~76)难以得到广泛的应用,而1x/4x串行RapidIO仅4或16个信号线,逐渐成为主流,所以本文仅介绍串行RapidIO。

串行RapidIO基于现在已广泛用于背板互连的SerDes(Serialize Deserialize)技术,它采用差分交流耦合信号。差分交流耦合信号具有抗干扰强、速率高、传输距离较远等优点。差分交流耦合信号的质量不是由传统的时序参数来衡量,而是通过眼图来衡量,眼图中的“眼睛”张得越开则信号质量越好。

差分信号的强弱由一对信号线的电压差值表示,串行RapidIO协议规定信号峰-峰值的范围是200mV-2000mV。信号幅度越大,则传输距离越远,RapidIO协议按信号传输距离定义两种传输指标:

- 短距离传输(Short Run),<=50厘米,主要用于板内互连,推荐的发送端信号峰-峰值为500mV-1000mV

- 长距离传输(Long Run),>50厘米,主要用于板间或背板互连,推荐的发送端信号峰-峰值为800mV-1600mV

为了支持全双工传输,串行RapidIO收发信号是独立的,所以每一个串行RapidIO口由4根信号线组成。标准的1x/4x 串行RapidIO接口,支持四个口,共16根信号线。这四个口可被用作独立的接口传输不同的数据;也可合并在一起当作一个接口使用,以提高单一接口的吞吐量。

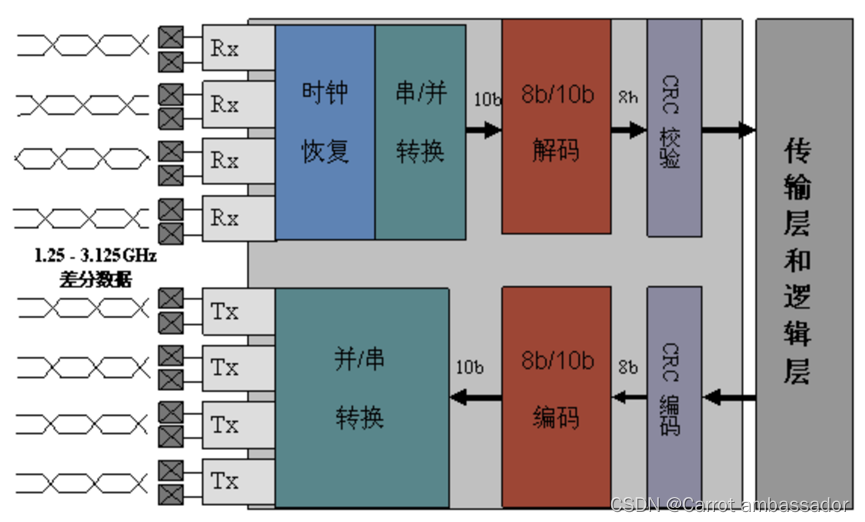

德州仪器TMS320C6455 DSP上集成了标准的1x/4x串行RapidIO接口,如图6所示。

发送时,逻辑层和传输层将组好的包经过CRC编码后被送到物理层的FIFO中,“8b/10b编码”模块将每8bit数据编码成10bits数据,“并/串转换”模块将10bits并行数据转换成串行bits,发送模块把数字bit转换成差分交流耦合信号在信号线上发送出去。这里的8b/10编码的主要作用是:

- 保证信号有足够的跳变,以便于接收方恢复时钟。串行RapidIO没有专门的时钟信号线,接收端靠数据信号的跳变恢复时钟。所以需要把信号跳变少的8bits数据(如全0或全编码成有一定跳变的10bits数据。另外,也使得总体数据中0和1的个数均衡,以消除直流分量,保证交流耦合特性;

- 8b/10编码可扩大符号空间,以承载带内控制符号。10bits能表示1024个符号,其中256个表示有效的8bits数据,剩下的符号中的几十个被用作控制符号。控制符号可被用作包分隔符,响应标志,或用于链路初始化,链路控制等功能;

- 8b/10编码能实现一定的检错功能。1024个符号中,除了256个有效数据符号和几十个控制符号外,其它符号都是非法的,接收方收到非法符号则表示链路传输出错。

接收的过程则正好相反,首先接收方需要根据数据信号的跳变恢复出时钟(硬件设计时不用组间等长),用这个时钟采样串行信号,将串行信号转换为10bits的并行信号,再按8b/10b编码规则解码得到8bits数据,最后做CRC校验并送上层处理。

数据被正确的接收时,接收端会发送一个ACK响应包给发送端;如果数据不正确(CRC错或非法的10bits符号),则会送NACK包,要求发送方重传。这种重传纠错的功能由物理层完成,而物理层功能往往由硬件实现,所以不需要软件干预。

串行RapidIO支持的信号速率有三种:1.25GHz,2.5GHz,3.125GHz。但由于8b/10b编码,其有效数据速率分别为:1Gbps, 2Gbps, 2.5Gbps。 4个1x端口或一个4x端口支持的最高速率为10Gbps。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?