功率 MOSFET 工作在耐压模式下时,整个器件相当于一个 P+/N- 突变结二极管,其中 P 型重掺杂区域由 Pbody 构成,N 型轻掺杂区域由外延层构成。在芯片的元胞区中间位置可以近似认为是一个平行平面结,而在芯片的元胞区外围可以认为是柱面结。因此分析突变结二极管的击穿对理解功率MOSFET的耐压机制有很大的帮助。

1. 平行平面结击穿

突变结的特点是P型区和N型区的掺杂浓度量级相差较大,耗尽层在高掺杂区域的扩展可以忽略不计,所以可以近似认为在高掺杂区域不承担电压。(实际中并不存在)

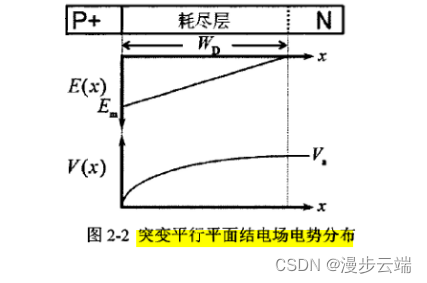

图 2-2 所示为非穿通型突变平行平面结的电场与电势分布。由于 P 型区域是重掺杂,而 N 型区域是轻掺杂,所以耗尽层可以认为只向 N 型区方向扩展。实际上 P 型区也是有耗尽层的,不过相对 N 型区中的耗尽层来说太短,为了方便计算可以忽略。

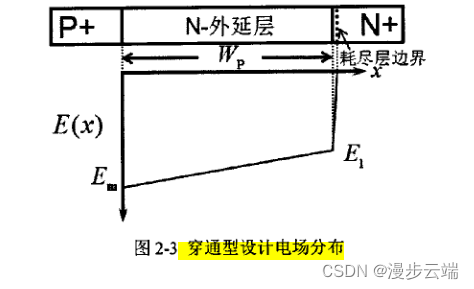

在实际的器件设计中,特别是高压器件,更多采用图 2-3 所示的穿通型突变结二极管模型,类似于 P-i-N 整流器。

与图 2-2 相比,图 2-3 多了一个 N+ 区,并且图 2-2 的外延层掺杂浓度相对较低。耗尽层在扩展到 N- 与 N+ 区域的交界面时,由于 N+ 区域掺杂浓度很大不会再继续扩展更远,相应的电场分布类似梯形,而非穿通型的电场分布是三角形。因此在相同的外延层厚度条件下,穿通型结构能得到更高的击穿电压。当然这是以牺牲 Rdson 为代价来换取更高的击穿电压,因为外延层厚度相同时,穿通型设计必然比非穿通设计有更低的外延层掺杂浓度。

设计1000V的 P-i-N 整流器,用穿通型大概需要 50um 的漂移区外延层厚度,而采用非穿通型需要的漂移区厚度大约为 80urn。漂移区的减小有利于降低器件的导通压降并且对反向恢复特性的优化有帮助。???

2. 缓变结击穿

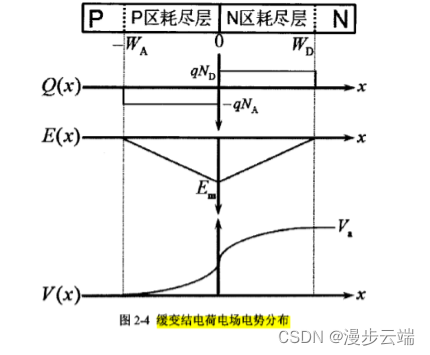

缓变结的 P 区和 N 区掺杂浓度量级接近,耗尽层在 P 区和 N 区的扩展都不可忽略。

图 2-4 所示为缓变结结构及其反偏时的电荷、电场、电势分布。

在一般的书籍及文献中谈论得更多的是线性缓变结,其掺杂浓度由结区向外围线性增加,因此其电荷也是线性分布的,而不是图 2-4 中恒定分布。线性缓变结主要用来分析扩散结二极管,并且由于 P 区掺杂浓度高而结深不容易做得太深,所以对应 N 型区的掺杂浓度也较高,常用来做低压器件。从图 2-4 中可以看出缓变结的 P 区和 N 区都承担了电压,相对于突变结来说,硅片利用率会大大提高。

3. 柱面击穿

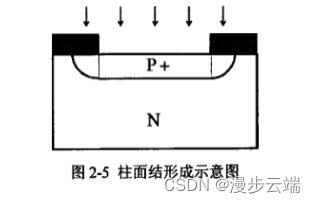

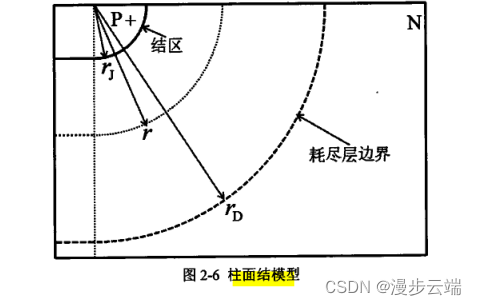

实际的工艺中,通过光刻工艺开窗之后进行离子注入并退火来形成 PN 结,退火时掺杂离子向各个方向扩散,在开窗中间扩散形成一个平面,可以看做平行平面结,但是在开窗的边沿,扩

散形成的却是一个弧形,可以看做一个柱面结,如图 2-5 所示。

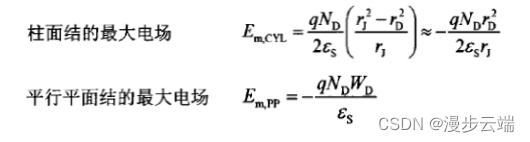

图 2-6 所示为对突变柱面结建模的示意图,其中 P+ 区掺杂浓度远高于 N 区掺杂浓度,耗尽层在 P+ 区的扩散可以忽略不计,P+ 区的结深为 r j 。当施加反向偏压时,耗尽层在 N 区中扩展,其半径为 r D 。

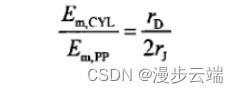

与平行平面结类似,在 r = r j 处有最大电场。并且在高压器件的设计中往往有 r j < r D,所以

假设当平行平面结的耗尽层与柱面结耗尽层相等,即 W D = r D,可以对二者的最大电场进行比较:

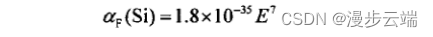

可以看出,在掺杂浓度、等条件相同的情况下,由于通常 rj << r D,因此,柱面结的电场会比平行平面结大很多。由于撞电离系数是电场的强函数,因此柱面结的雪崩击穿电压比平行平面结小很多。这也使得图 2-5 所示的二极管的击穿往往发生在掩膜边沿的柱面结处。

图 2-5 所示的实际工艺形成的 PN 结中,平行平面结的耗尽层宽度与柱面结的相差不多,而 rj由横向扩散形成,一般较小,所以柱面结的临界电场比平行平面结大。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?