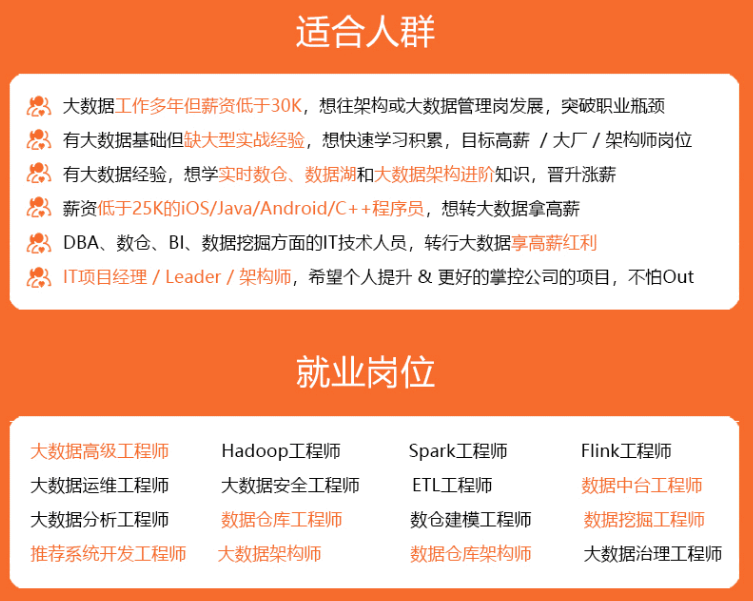

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

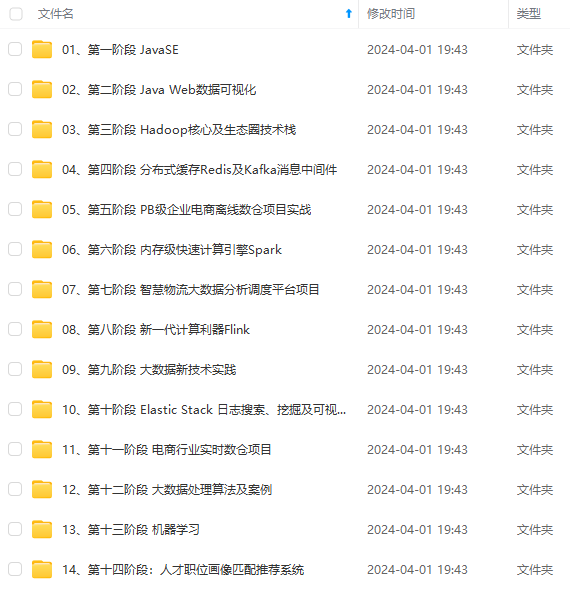

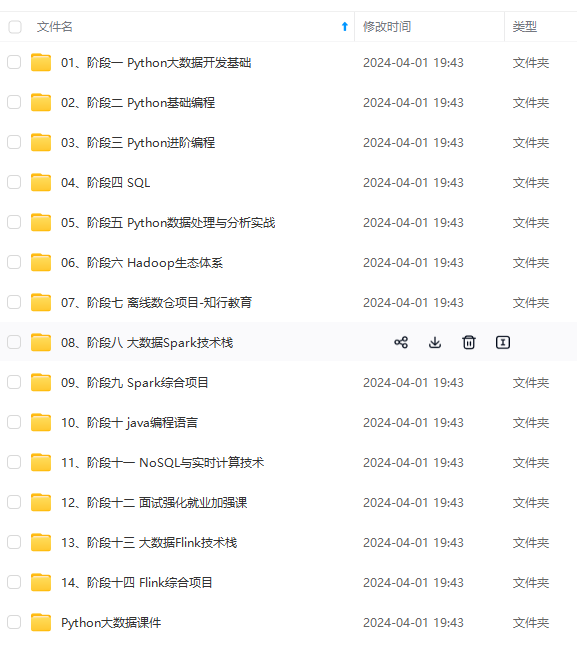

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

🔥**点击查看精选 PCIe 系列文章🔥

🔥点击进入【芯片设计验证】社区,查看更多精彩内容**🔥

📢 声明:

- 🥭 作者主页:【MangoPapa的CSDN主页】。

- ⚠️ 本文首发于CSDN,转载或引用请注明出处 https://blog.csdn.net/weixin_40357487/article/details/120714950。

- ⚠️ 本文为非盈利性质,目的为 个人学习记录 及 知识分享。因个人能力受限,存在协议解读不正确的可能。若您参考本文进行产品设计或进行其他事项并造成了不良后果,本人不承担相关法律责任。

- ⚠️ 若本文所采用图片或相关引用侵犯了您的合法权益,请联系我进行删除。

- 😄 欢迎大家指出文章错误,欢迎同行与我交流 ~

- 📧 邮箱:mangopapa@yeah.net

文章目录

| — 0️⃣ PCIe 6.0 概述 — |

✨ 0. PCIe 6.0 概述

2019 年 5 月中旬 PCI-SIG 正式发布了 PCIe 5.0 的 1.0 版本后,便马不停蹄长驱直入进入了 PCIe 6.0 的预研阶段,并在 4 个半月后发布了 PCIe 6.0 的 0.3 版本。时隔两年,现如今 PCIe 6.0 的 0.9 版本已经发布,PCIe 6.0 正式版倚马可待(预计 2021 年底发布)。 (最新消息:确定了 2022 Q1 发布 )

跟 PCIe 5.0 相比,PCIe 6.0 主要有以下变化:

- 单 Lane 传输速率由 32 GT/s 变为 64 GT/s;

- 传输信号由 NRZ 两电平变为 PAM4 四电平;

- 编码方式由 128b/130b 变为 FLIT 编码;

- 引入了 FEC 前向纠错机制,并维持既有的 Retry 重传机制;

- LTSSM 新增加了 L0p 低功耗状态,允许部分 Lane Electric Idle、部分 Lane Active;

- 新加了几种机制:DOE、CMA、DMWr、IDE。

| — 1️⃣ 速率 64 GT/s — |

✨ 1. 速率 64 GT/s

单条传输线传输速率变为 64 GT/s 似乎在大家的预期之内,毕竟从 PCIe Gen1 到 Gen5 每次都是速率 Double。从 Gen5 的 32 GT/s 到 Gen6,按照惯性思维这次也该 64 GT/s 了。唯一让大家吃惊的是,Gen6 来得属实太快了。千千万万 PCIe 从业者,用都还没用过 PCIe 5.0,PCIe 6.0 便跃然眼前。

| — 2️⃣ PAM4 信号 — |

✨ 2. PAM4 信号

传输信号采用 PAM4 四电平信号有点出乎人的意料,毕竟从 Gen1 到 Gen5 一直用得是 NRZ 二电平信号。不过想想 PAM4 也合情合理,再用 NRZ,这高频 Clock 就太难了。接下来再怎么搞我有点头疼,用 PAM16 也太难了吧,眼图都要瞎掉了。

| — 3️⃣ FLIT 编码 — |

✨ 3. FLIT 编码

FLIT Mode,流控单元模式,是一种1b/1b的编码方式。之前是以 TLP 为单位进行事务传输,PCIe 6.0 以 FLIT 为单位进行事务传输,每个 FLIT 有 256 B 数据(格式如 式1),每 B 数据占用 4 UI。以 x8 为例,一次 FLIT 传输的格式如图 1 所示。

1 FLIT = 236 B TLP + 6 B DLP + 8 B CRC + 6 B FEC = 256 B

(式1)

每个 FLIT 可以包含多笔 TLP,每笔 TLP 也可以拆分到多笔 FLIT。FLIT 中有 6 B DLP 数据(非DLLP),其中前 2 B 是留给 FLIT ACK / NAK / Replay 用的,取代了 Gen5 中采用 DLLP 的 ACK / NAK 机制。以 x16为例,由于不需额外规划 DLLP 的发送,这种在 FLIT 中加入 DLP 的 ACK / NAK 机制把相关时延从 ms 级降到了50 ns 以内,成效可观。只要开启了 FLIT Mode,即便数据速率从Gen6 调到 Gen1 ~ Gen5,仍然采用 FLIT 编码方式。

图1 x8 FLIT 格式

| — 4️⃣ 纠错 — |

✨ 4. 纠错

PCIe 6.0 引入了 FEC 前向纠错机制,并维持既有的 Retry 重传机制。在 PCIe Gen5 中,当 CRC 校验检测到 TLP 传输出错时,采用 Retry 机制进行重传。考虑到重传时延 <300 ns 且重传概率低于 10^-5,其对传输性能影响甚微。在 PCIe Gen6 中,对 Latency 的要求为 10 ns,仅采用 Retry 机制无法满足需求。在综合考量了FBER、FIT、FLIT Retry 概率、带宽效率、Latency 及 FLIT 的 FEC 能力后,PCIe Gen6 最终采用了低权重 FEC + Retry 的纠错方案。

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

g-d6HNhAa6-1714856607315)]

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

文章详细介绍了PCIe6.0的新特性,包括速率提升至64GT/s、PAM4信号的使用、FLIT编码的引入、FEC纠错机制以及低功耗优化。提供针对不同经验水平的学习资源,包括体系化的教程、案例和持续更新的内容。

文章详细介绍了PCIe6.0的新特性,包括速率提升至64GT/s、PAM4信号的使用、FLIT编码的引入、FEC纠错机制以及低功耗优化。提供针对不同经验水平的学习资源,包括体系化的教程、案例和持续更新的内容。

1900

1900

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?