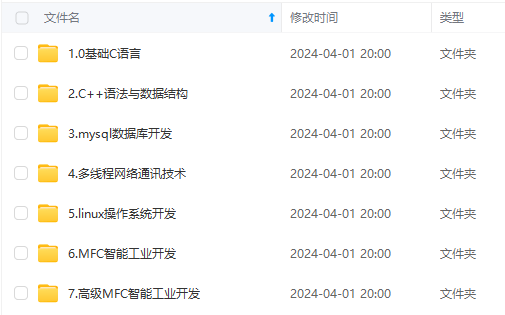

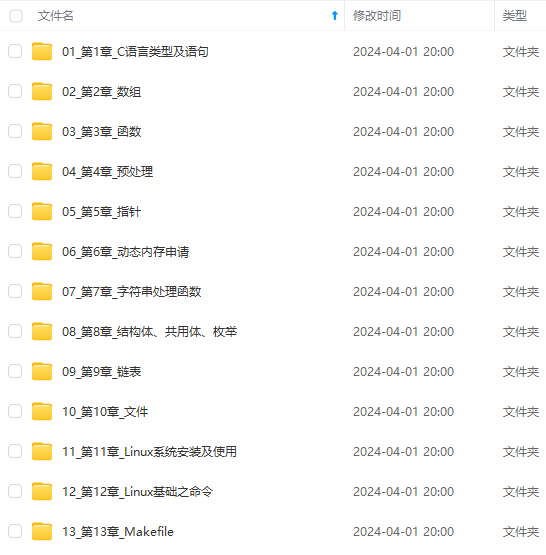

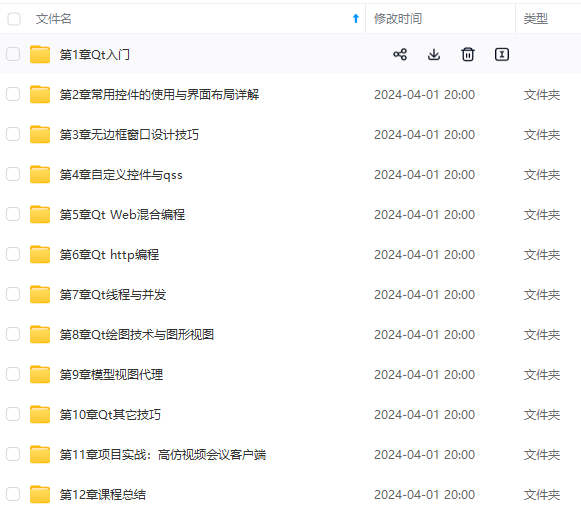

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上C C++开发知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

图1 NRZ 与 PAM4 信号和眼图

图2 NRZ vs PAM4

| — PAM4,凭啥你能行? — |

✨3. PAM4,凭啥你能行?

3.1 PCIe爱上PAM4的N个理由

- 速率更高。相同波特率下,PAM4数据速率是NRZ的两倍。

- 带宽路利用率更高。带宽利用率也为NRZ的两倍。

- 相同数据速率时信道插入损耗(衰减)更低。相同发送发送功率下, 发送频率越大插入损耗越大。同等条件下PAM4的发送频率仅为NRZ的一半,其插入损耗更低。信道衰减不变的情况下,PAM4发送的数据速率时NRZ的两倍。

- ……

3.2 PAM4就完美无瑕了?

3.2.1 人非圣贤,孰能无过

跟NRZ比,PAM4当然有缺点,如下:

- 信噪比低、码间干扰大、误码率高。根据图1,PAM4单个眼睛的张开高度仅为NRZ高度的1/3,

信噪比比NRZ低9.54dB。显然PAM4对噪声更敏感、更容易收到噪声影响,相同传输条件下接收误码率更高。NRZ眼图有2个跳变沿,PAM4有12个跳变沿,PAM4从四个电平来回跳的时候必然会引起转换抖动,使得PAM4的眼宽降低至NRZ的1/2-2/3。也就是说,眼小,眼还窄。你就说解调器的压力大不大?- 功耗大。相比NRZ,PAM4有3个眼睛,这3个眼睛并不是对称的,需要独立处理。为了能有3个漂亮的眼睛,无论是发送端预补偿还是接收端均衡,都有至少3倍的工作要做,PAM4要做的工作都比NRZ多得多,这都耗能。

- 实现成本高。为了后向兼容,在保留既有NRZ电路及逻辑的情况下,从PHY到物理层每个级别都要实现PAM4,成本噌噌噌。

图3 PAM4与NRZ信号跳变

3.2.2 格局打开,放眼全局

有些缺陷时可以弥补的,不能弥补的为了全局收益也可以忍:

- 误码率高——为了降低误码率,加入了FEC前向纠错机制,加之采用格雷码编码,仅以不降低误码率,这不就解决了嘛。

- 额外预补偿和均衡导致功耗高——多干点活付出点代价不应该的吗?哪能又要马儿跑又要马儿不吃草!再说我PCIe 6.0 加个L0p低功耗状态不刚好能找补一些吗?

- 成本高——那我卖贵一点啊,更贵的价格享受更优质的服务,有啥毛病吗?

| — 那些不得不说的事儿 — |

✨4. 那些不得不说的事儿

4.1 有了PAM4,你置我NRZ于何地?

正如Gen3采用了128b/130b编码后仍然兼容Gen1-2的8b/10b编码,采用PAM4信令的Gen6同样做到了向后兼容采用NRZ信令的Gen1-5。为了做到兼容Gen1-5,Gen6在既有基础上新增额外的电路与逻辑来单独处理PAM4的3眼信号。也就是说,NRZ,你之前能干啥,现在还干啥,我PCIe也不是喜新厌旧的人。

PAM4仍然采用与NRZ相同的电压幅度范围,不同之处在于这里要把这段范围分为四个区间。

4.2 PAM4为啥扯上了格雷码?

众所周知,相邻两个电平的信号最容易出现误判。如果不采取点啥措施,在PAM4中从电平1->电平2(01->10),一次误判可就错2bit啊!为了减少误判,我们采用格雷码对电平0、1、2、3进行编码,这样一次相邻电平信号的误判最多只错1bit。

图4 非格雷码PAM4 vs. 格雷码PAM4

4.3 PAM,是不是阶数越大越好?

不是。理想状态下是的,但阶数较大时,尤其时在高速应用中,还要考虑物理设施发送和接收PAM信号的能力:

阶数高了不好发。发出不同电平的信号涉及到发送功率控制问题,精确又高速的功率控制是很难的。阶数高了接收误码率高。考虑到存在传输噪声,对于相同电压幅度范围,阶数越高受噪声影响越大,接收误码率越高。

4.4 PCIe你为何不早点用PAM4?

时机未到。缘分,是对的时间遇到对的人。

| — 参考 — |

📚参考

- PCI-SIG, “PCI Express base specification revision 6.0, version 0.9,” Beaverton, OR, USA, Oct 5, 2021.

- D. Das Sharma, “PCI Express 6.0 Specification: A Low-Latency, High-Bandwidth, High-Reliability, and Cost-Effective Interconnect With 64.0 GT/s PAM-4 Signaling,” in IEEE Micro, vol. 41, no. 1, pp. 23-29, 1 Jan.-Feb. 2021, doi: 10.1109/MM.2020.3039925.

- 400G以太网中的PAM4是什么?与NRZ有什么区别?

- 5.0刚推出,PCIe 6.0又要来了:PAM4取代NRZ,引入前向纠错,速率再翻倍!

- PAM4: For Better and Worse

- Understanding NRZ and PAM4 Signaling

| — END — |

⬆️ 点击回到文首 ⬆️

网上学习资料一大堆,但如果学到的知识不成体系,遇到问题时只是浅尝辄止,不再深入研究,那么很难做到真正的技术提升。

一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人,都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!

607)]

网上学习资料一大堆,但如果学到的知识不成体系,遇到问题时只是浅尝辄止,不再深入研究,那么很难做到真正的技术提升。

一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人,都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!

839

839

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?