一、 FPGA的硬件结构

这里说的硬件结构主要从FPGA的引脚功能方面描述,FPGA内部的电路逻辑暂不讨论。

FPGA的引脚大致可以分为三类:功能引脚、IO引脚、电源和接地引脚。

- 功能引脚

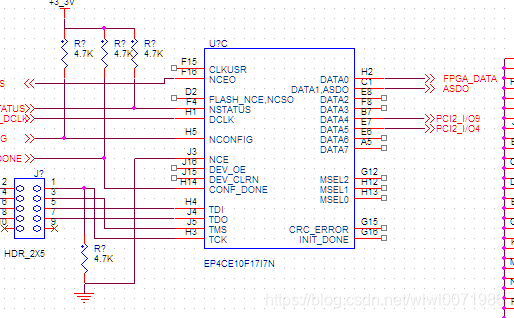

FPGA的功能引脚包含了FPGA配置程序加载、FPGA配置模式选择、状态及错误提示、JTAG调试等等。

DCLK、DATA0、NCONFIG、CONF_DONE这几个引脚是配置FPGA所必须的,DATA1~DATA7可以用作其他功能,INIT_DONE可以不使用。TDI、TDO、TMS、TCK四个脚是JTAG调试使用,一般会预留。

- IO引脚

FPGA的IO引脚是芯片与外部电路的接口部分,完成在不同电气特性下对输入/输出信号的驱动与匹配要求。FPGA的IO引脚按组分类,每组都能够独立地支持不同的IO标准。通过软件的灵活配置,可适配不同的电气标准与IO物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。为了便于管理和适应多种电器标准,FPGA的IO引脚被划分为若干个Bank,每个BANK的接口标准由其接口电压VCCIO决定。

一个BANK只能有一种VCCIO,但不同的BANK的VCCIO可以不同,只有相同电气标准的端口才能接到一起。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

734

734

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?