在电子系统设计中,时钟源是数字电路的核心“心跳”发生器。不同的应用场景对时钟信号的精度、稳定性和成本提出了差异化的需求。

无源晶振:无源晶振(晶体谐振器)是一种基于石英晶体压电效应的频率控制元件,电极施加电压后,石英晶片发生形变,产生周期性机械振动。振动频率由晶片切割方式和物理尺寸决定,形成稳定振荡信号,需匹配MCU/IC内部振荡电路及外部负载电容(通常5-30pF)才能起振。

有源晶振:有源晶振(晶体振荡器)是自带放大电路的完整振荡器,无需依赖外部电路即可输出稳定时钟信号。石英晶片在电压激励下产生机械振动,通过内部放大电路转换为电信号,输出方波信号(精度可达0.1ppm),直接驱动后续电路,无需依赖主控芯片内部振荡电路,独立完成起振。

高稳晶振:高稳晶振是指具有优异频率稳定性的晶体振荡器,其核心指标为频率偏差极小(通常优于±1ppm),且能在复杂环境(如温度波动、机械振动)下保持长期稳定。主要依赖温度补偿技术(TCXO):通过内置热敏网络或数字补偿算法抵消温度变化对频率的影响、恒温控制技术(OCXO):将石英晶体置于恒温槽中,消除温度波动引起的频率漂移、低老化率设计:优化晶体加工工艺,降低石英材料随时间的老化速率(典型值<±0.5ppm/年)。

| 序号 | 类型 | 工作原理 | 电路复杂度 | 输出特性 |

| 1 | 无源晶振 | 基于石英晶体压电效应,需外接匹配电容和振荡电路 | 高(需外部起振电路) | 正弦波/方波(需整形) |

| 2 | 有源晶振 | 内置振荡器和放大电路,直接输出稳定时钟信号 | 低(无需外部电路) | 方波(CMOS/LVDS电平) |

| 3 | 高稳晶振 | 采用温度补偿(TCXO)或恒温控制(OCXO)技术 | 极高(集成温控系统) | 低抖动高纯度方波 |

性能参数对比

| 序号 | 参数 | 无源晶振 | 有源晶振 | 高稳晶振(TCXO/OCXO) |

| 1 | 频率精度 | ±10~100ppm | ±0.1~10ppm | ±0.01~1ppm(TCXO) ±0.001ppm(OCXO) |

| 2 | 温度稳定性 | ±20~100ppm(全温) | ±5~50ppm(全温) | ±0.1~0.5ppm(TCXO) ±0.01ppm(OCXO) |

| 3 | 相位噪声 | -120dBc/Hz@1kHz | -140dBc/Hz@1kHz | -160dBc/Hz@1kHz |

| 4 | 功耗 | <1mW | 10~100mW | 0.1~5W(OCXO可达10W) |

| 5 | 启动时间 | 1~10ms | 0.1~5ms | 30s~5分钟(OCXO需预热) |

| 6 | 典型成本 | ¥0.1~1(3225封装) | ¥1~50(SMD封装) | ¥50~500(TCXO) ¥500~5000(OCXO) |

应用场景与选型策略

1. 无源晶振适用场景

- 消费电子:智能手表(32.768kHz RTC时钟)、蓝牙耳机(16MHz主频)等

- 选型要点:优先选择±20ppm精度+12pF负载电容规格,避免时钟频偏导致通信失败

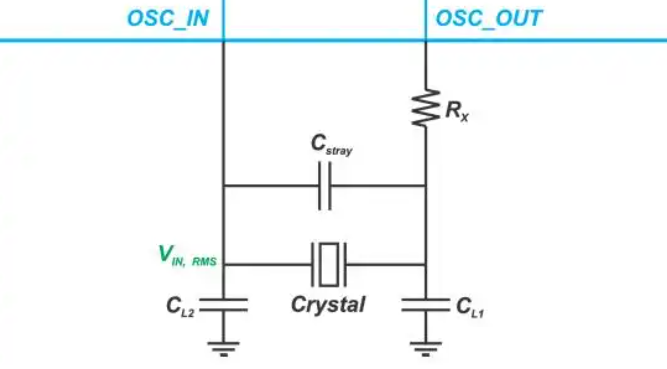

- 负载电容(C1/C2):依据公式 CL=(C1×C2)/(C1+C2)+Cstray 计算,其中Cstray为PCB寄生电容(约2-5pF)

- 反馈电阻(Rx):MHz晶振并联1MΩ电阻,kHz晶振用10MΩ,用于降低Q值、提升负性阻抗以辅助起振

- 晶振优先靠近MCU放置,距离控制在5mm以内以减少时钟路径干扰

- 负载电容需贴近晶振引脚,间距≤2mm以降低寄生电容影响

- 外围300mil(7.6mm)内禁止放置其他元件,避免机械振动干扰

- 时钟线优先走顶层,线宽≥8mil,与其他信号保持20mil间距并用地线包裹

- 晶振下方禁止走线,必须全层铺地且外壳接地以抑制辐射

2. 有源晶振适用场景

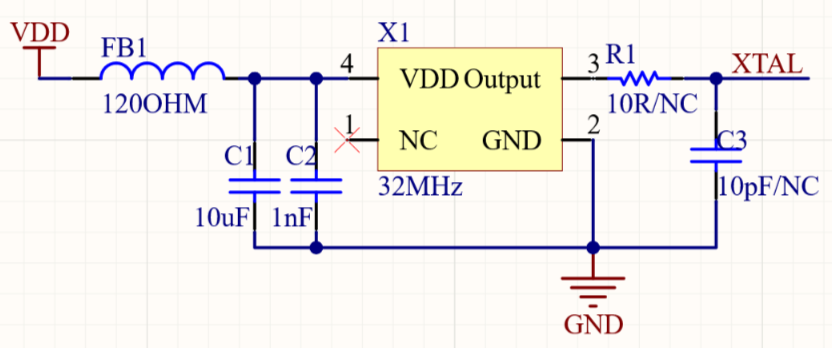

- 工业控制:无线射频时钟、5G小基站(156.25MHz差分时钟)

- 电源端需串联磁珠(如0603封装/100Ω@100MHz)以隔离电源噪声,并搭配π型滤波电路

- 去耦电容采用三级递减配置(如100nF+10nF+1nF),按电源流向依次靠近晶振引脚布局

- 输出端串联22-100Ω电阻(预留调试点),用于抑制谐波、减少信号反射及过冲

- 晶振优先靠近MCU放置,距离控制在5mm以内以减少时钟路径干扰

- 负载电容需贴近晶振引脚,间距≤2mm以降低寄生电容影响

- 外围300mil(7.6mm)内禁止放置其他元件,避免机械振动干扰

- 时钟线优先走顶层,线宽≥8mil,与其他信号保持20mil间距并用地线包裹

- 晶振下方禁止走线,必须全层铺地且外壳接地以抑制辐射

3. 高稳晶振核心应用

- 通信设备:OTN光传输网(156.25MHz OCXO,±0.05ppb稳定度)

- 关键技术:DOCXO(数字补偿OCXO)在-55~105℃实现<±3ppb全温频偏

- 高稳晶振多以外挂模块的形式出现

设计法则

- 精度冗余原则:实际选型精度应比系统需求高3倍(如USB 2.0需±500ppm,选±150ppm晶振)

- 功耗平衡法则:电池供电设备避免选用OCXO,优先TCXO或温补型有源晶振

- 热设计优先:高稳晶振需预留散热空间,OCXO周边1cm内禁止布置发热元件

- 信号完整性:>50MHz时钟建议采用阻抗控制布线,差分时钟线对长度误差<5mil

1055

1055

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?