使用过Vivado和Quartus的都知道,这两个软件的代码编辑器做的都不太行,微软的Visual Studio Code不管从界面还是功能上,都完胜上述两款软件的编辑器,因此这里教大家如何在VS Code上配置Verilog编程环境。

1. 下载VS Code

不多说,在微软官网上下载安装就行。

2. 配置VS Code

2.1 安装插件

Control + Shift + X,打开VS Code的扩展,在顶部搜索栏上输入Verilog,这里只推荐3个扩展插件,分别是

Verilog-HDL/SystemVerilog/Bluespec SystemVerilog、

Verilog_Testbench

SystemVerilog and Verilog Formatter

我们主要用VS Code进行Verilog代码编辑,仿真测试还是在Vivado和Quartus中进行。

2.2 配置插件

Verilog-HDL/SystemVerilog/Bluespec SystemVerilog插件安装完成后,需要配置,主要是安装Ctags。在这里下载Ctags,我自己电脑是64位 Win10下载x64版本。

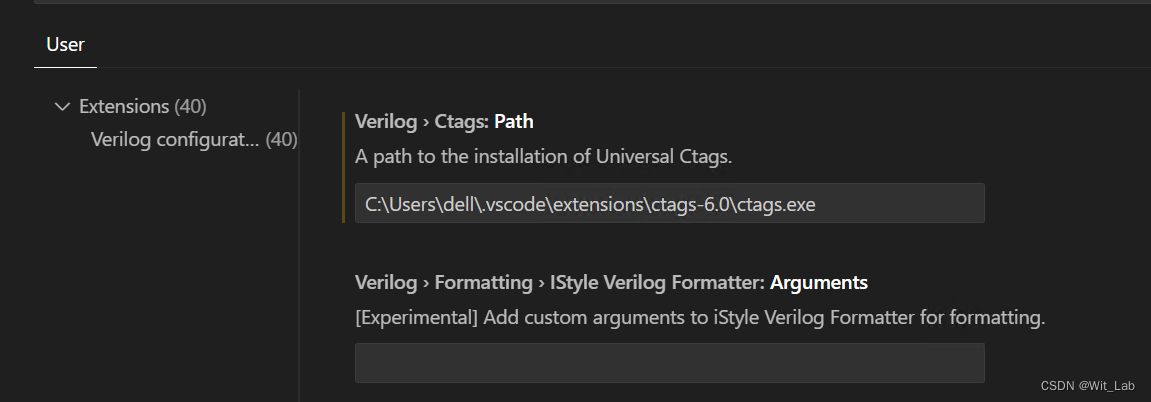

下载后解压到非中文目录,目录深度不要太深,否则会识别不到。然后在Verilog-HDL/SystemVerilog/Bluespec SystemVerilog插件的设置里面添加刚才Ctags的解压地址(需要指定catags.exe地址),如图所示。

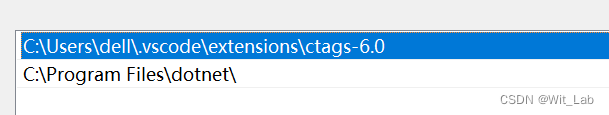

解下来将ctags的解压地址添加到系统环境变量的Path中,如下图所示:

解下来将ctags的解压地址添加到系统环境变量的Path中,如下图所示:

注:这里我的Path变量的长度过长了,所以新建了一个环境变量,并在Path中引用了新建的变量。

2.3 配置Vivado或Quartus

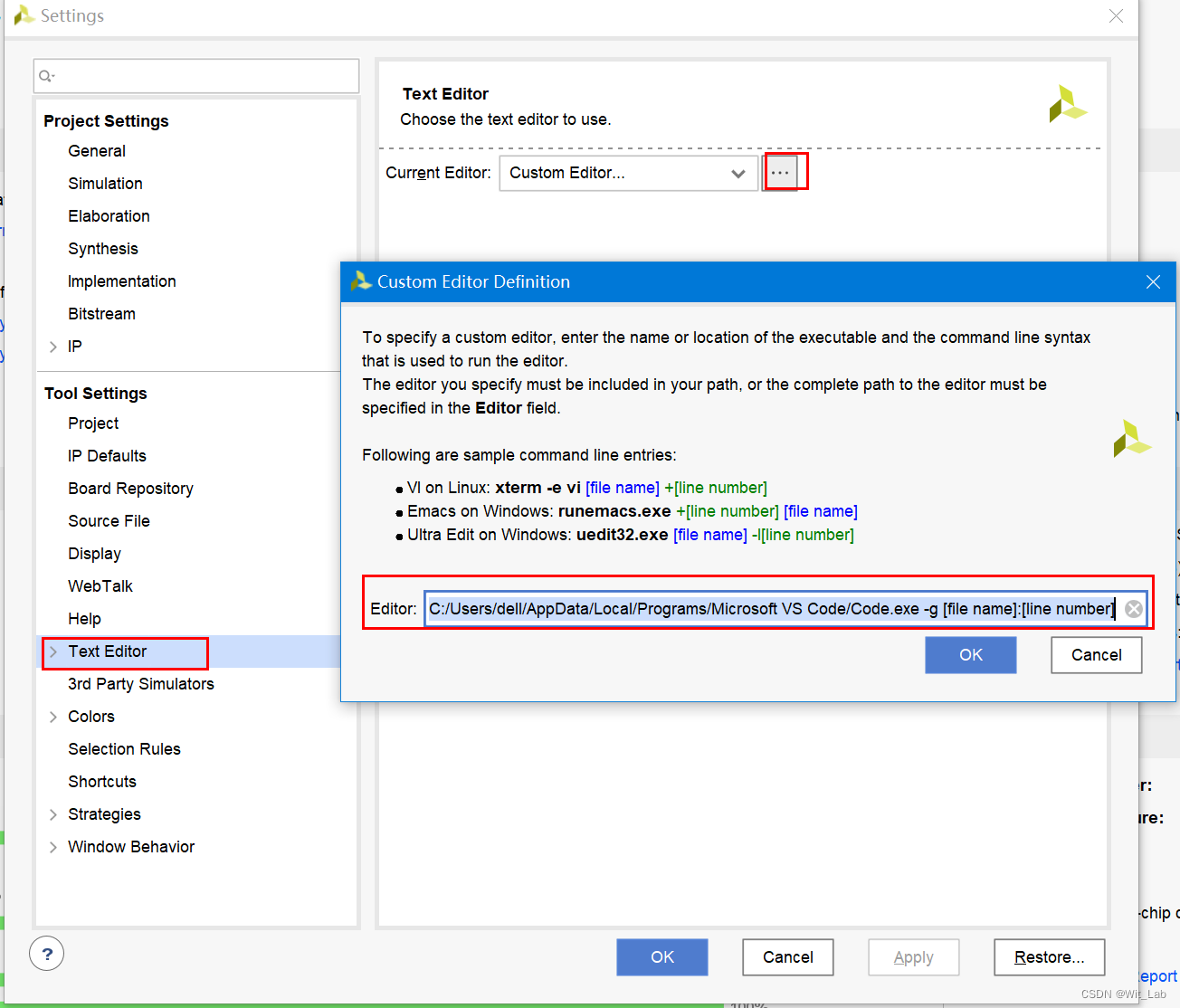

Vivado配置:Tools -> Settings -> Text Editor -> Current Editor 修改为Custom Editor,配置Editor地址为VS Code执行文件地址,格式为:<Your VS Code Addr> -g [file name]:[line number] 如下图所示

Quartus配置:Tools -> Options -> Preferred Text Editor,配置格式为:"<Your VS Code Addr> " -r -g %f:%l ,配置如下图所示(记得双引号不要丢):

2.4 重启系统

因为修改了环境变量需要重启系统才可识别新变量。

2.5 测试

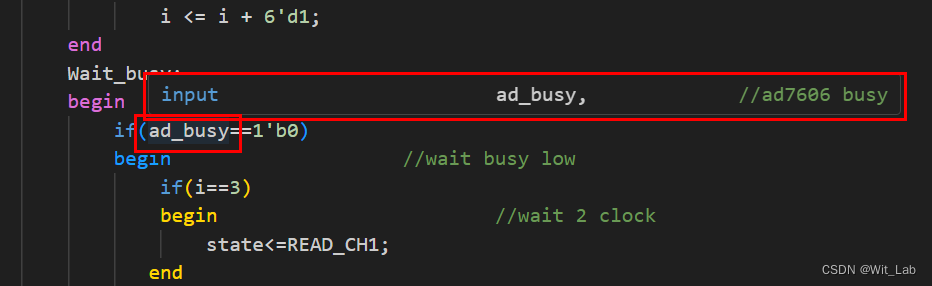

重启后在Vivado或Quartus中双击代码源文件,即可打开VS Code代码。当鼠标悬停在变量上方时,会自动弹出变量定义,也可以右键跳转到变量定义区域。

PS:推荐VS Code verilog代码格式化工具SystemVerilog and Verilog Formatter,配置如下

--column_limit 500 --indentation_spaces 4 --assignment_statement_alignment align --formal_parameters_indentation indent

本文指导如何在MicrosoftVisualStudioCode上配置Verilog开发环境,包括下载、安装插件如Verilog-HDL、配置Ctags、设置Vivado和Quartus工具选项,以实现代码编辑和跳转功能。

本文指导如何在MicrosoftVisualStudioCode上配置Verilog开发环境,包括下载、安装插件如Verilog-HDL、配置Ctags、设置Vivado和Quartus工具选项,以实现代码编辑和跳转功能。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?