Vivado版本:2018.3、2019.1、2019.2

FPGA: xc7k325t

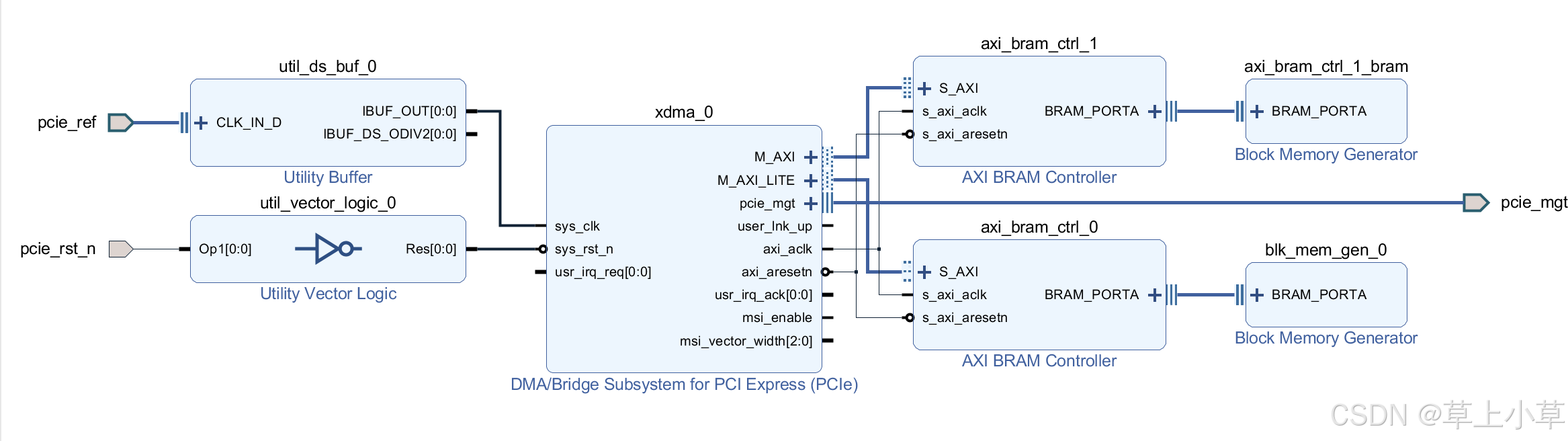

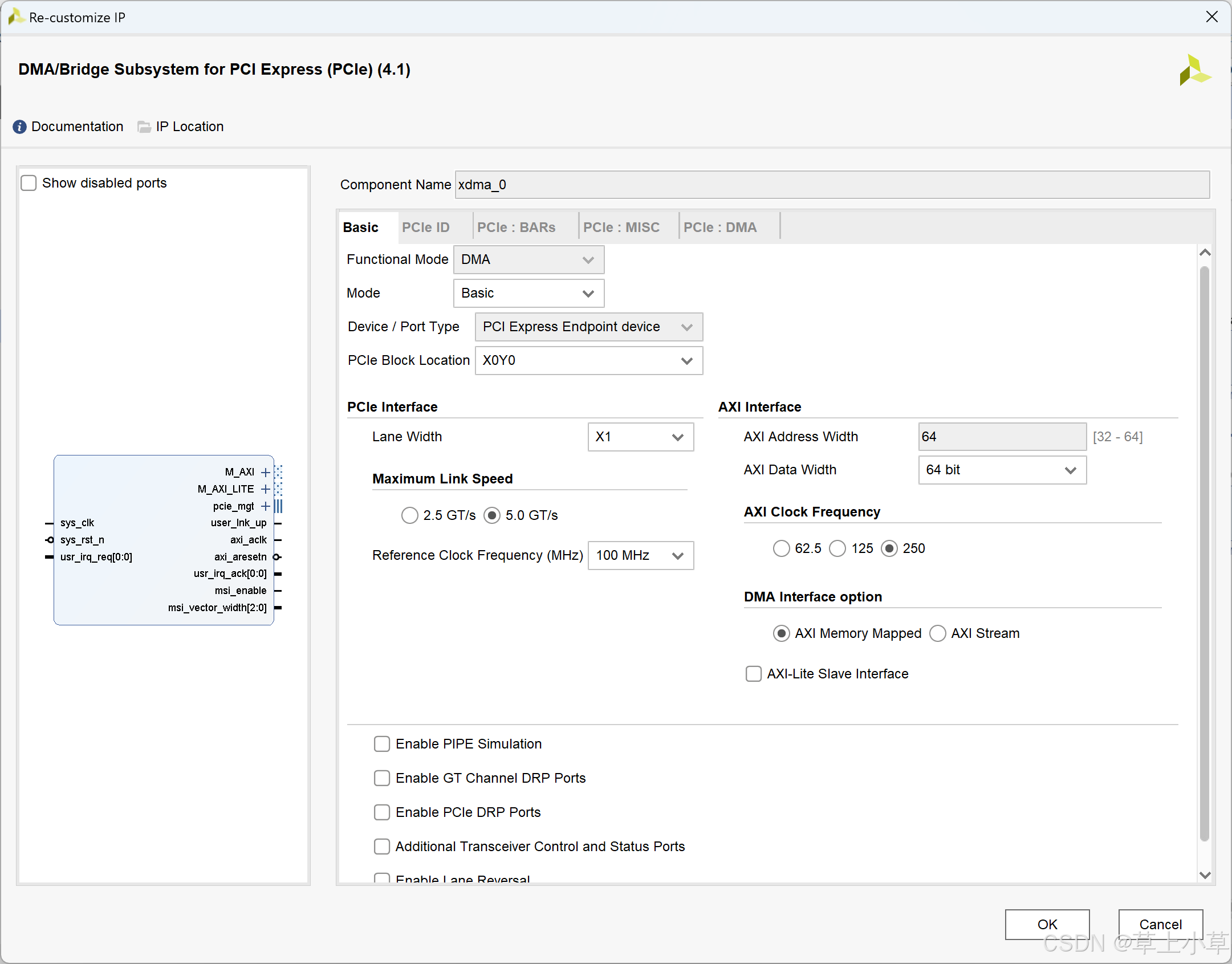

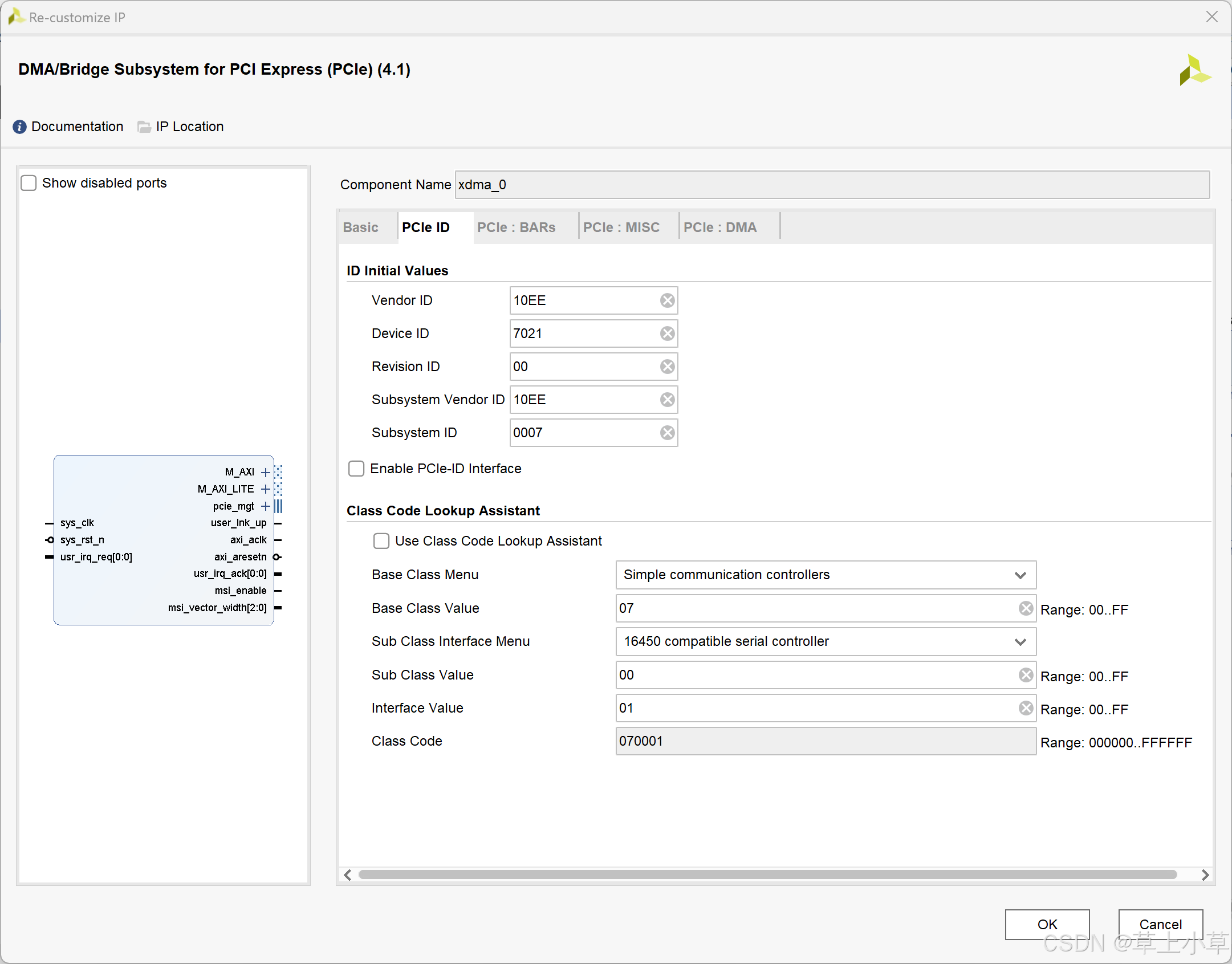

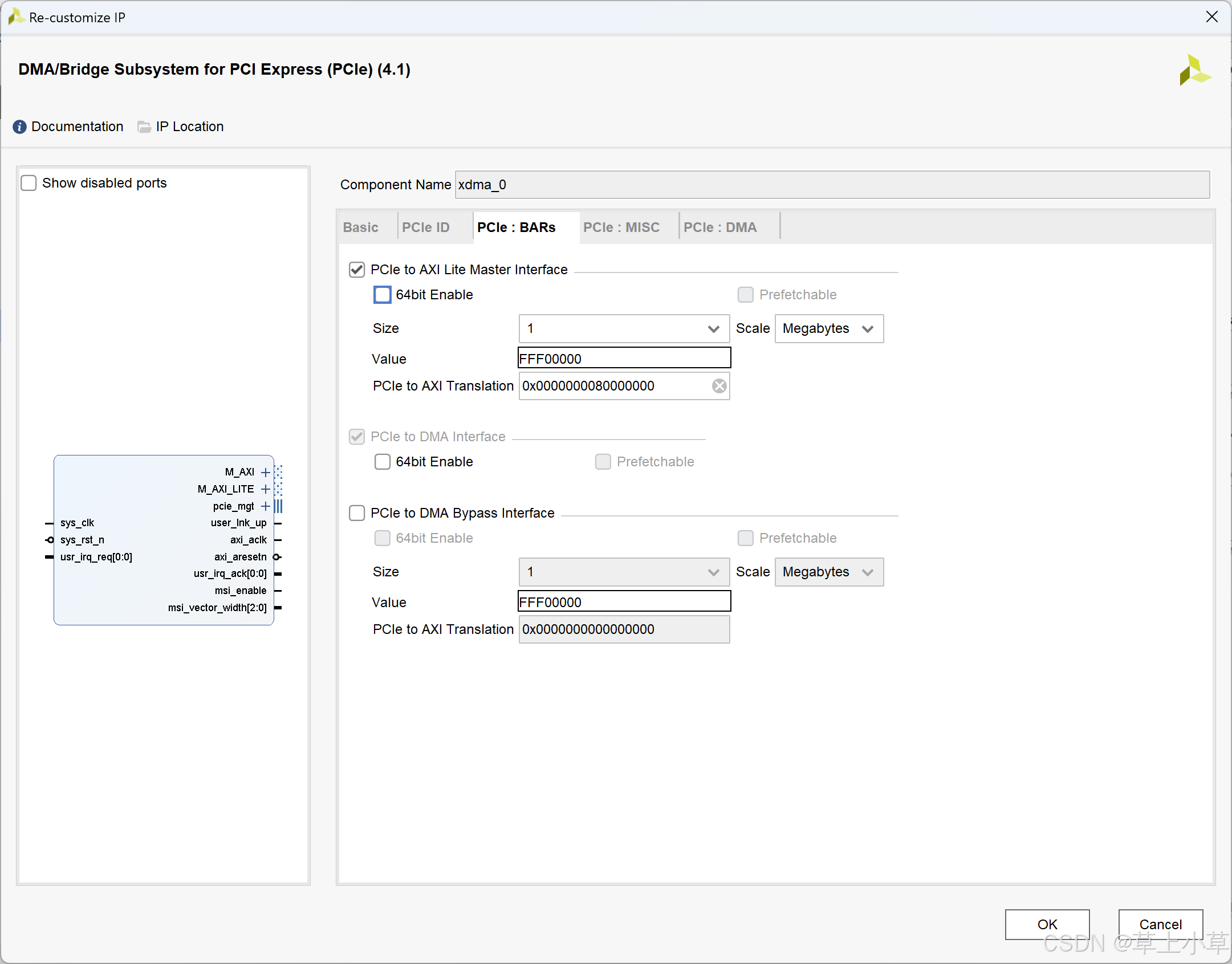

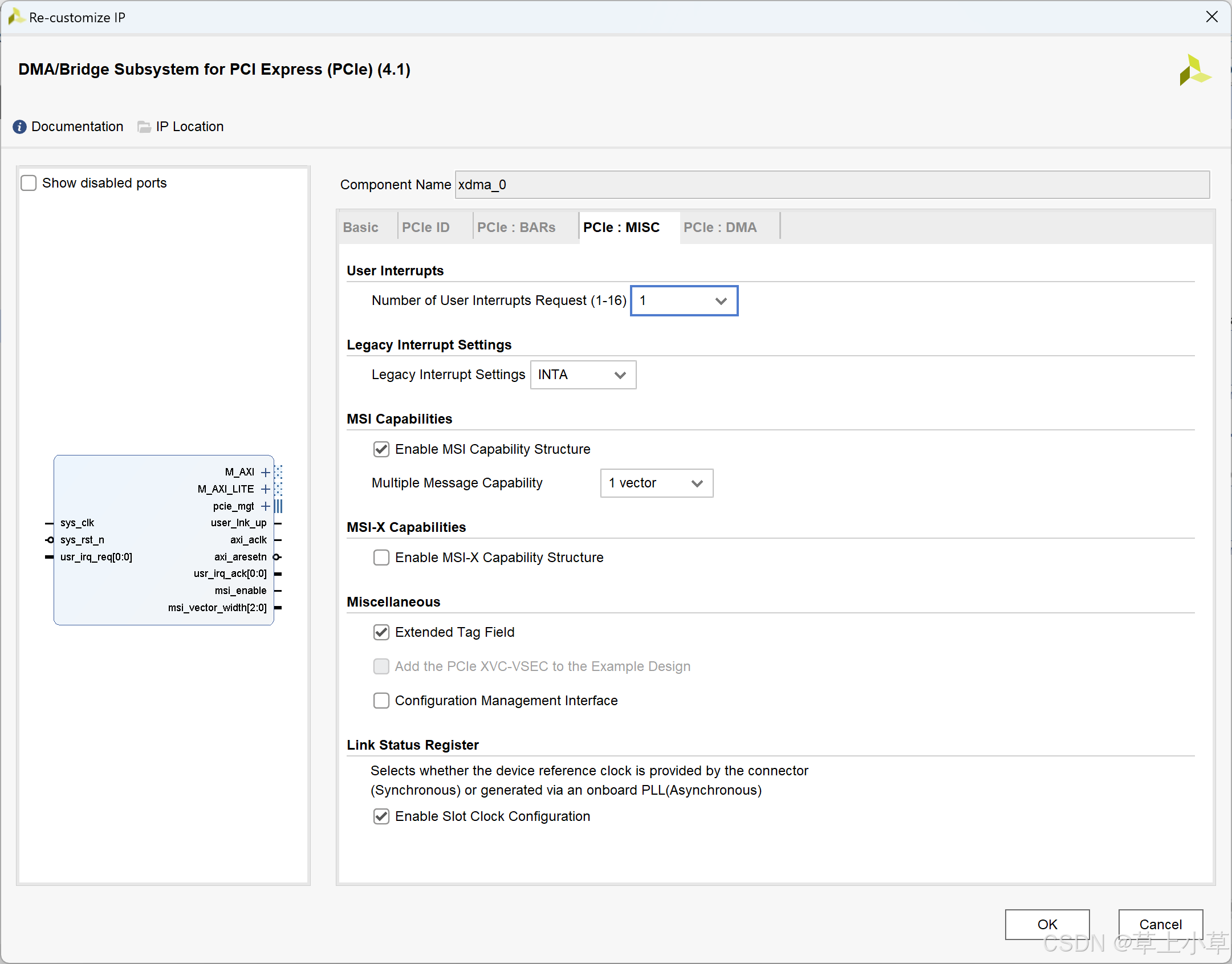

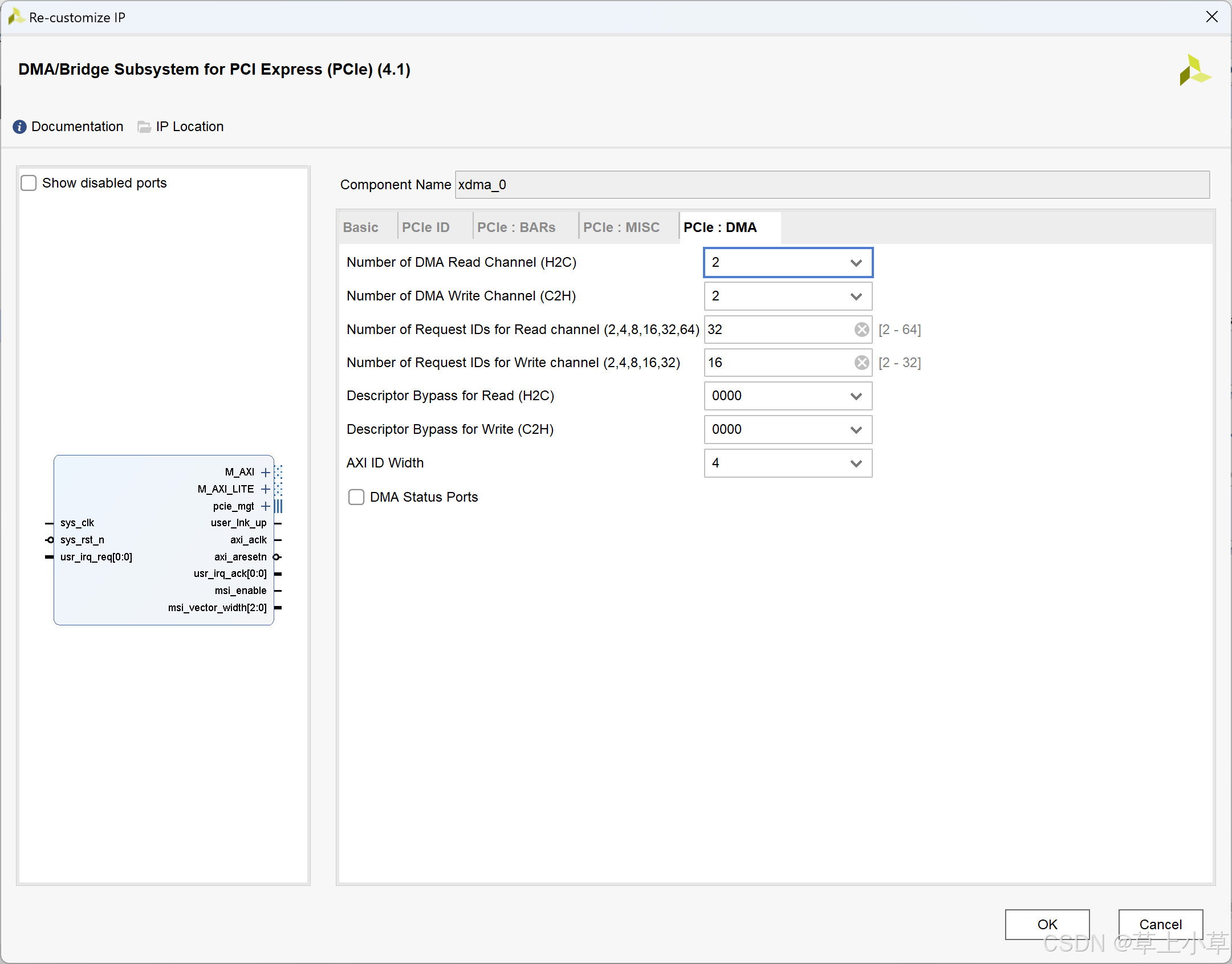

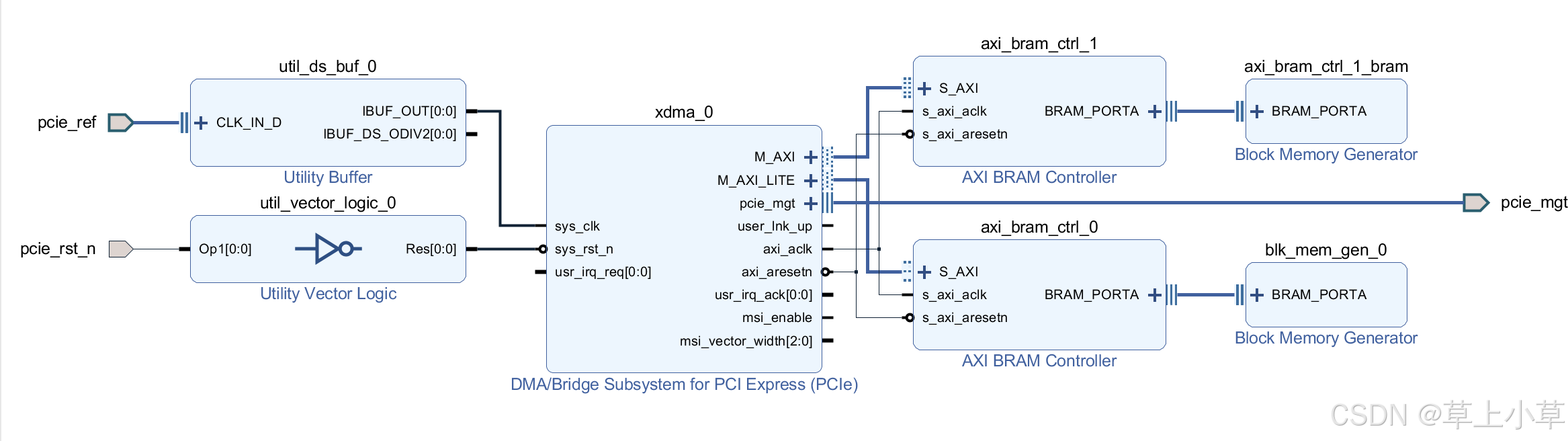

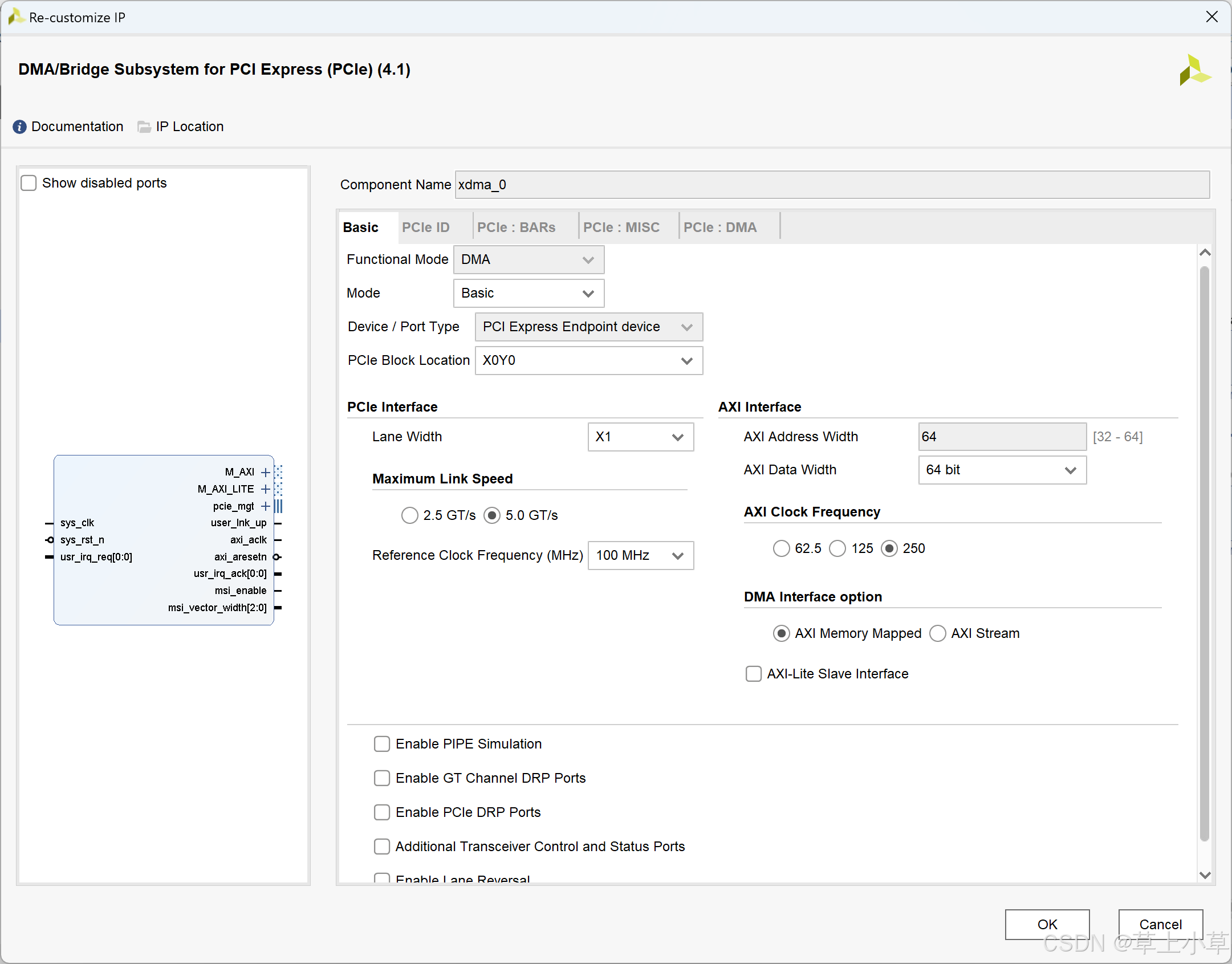

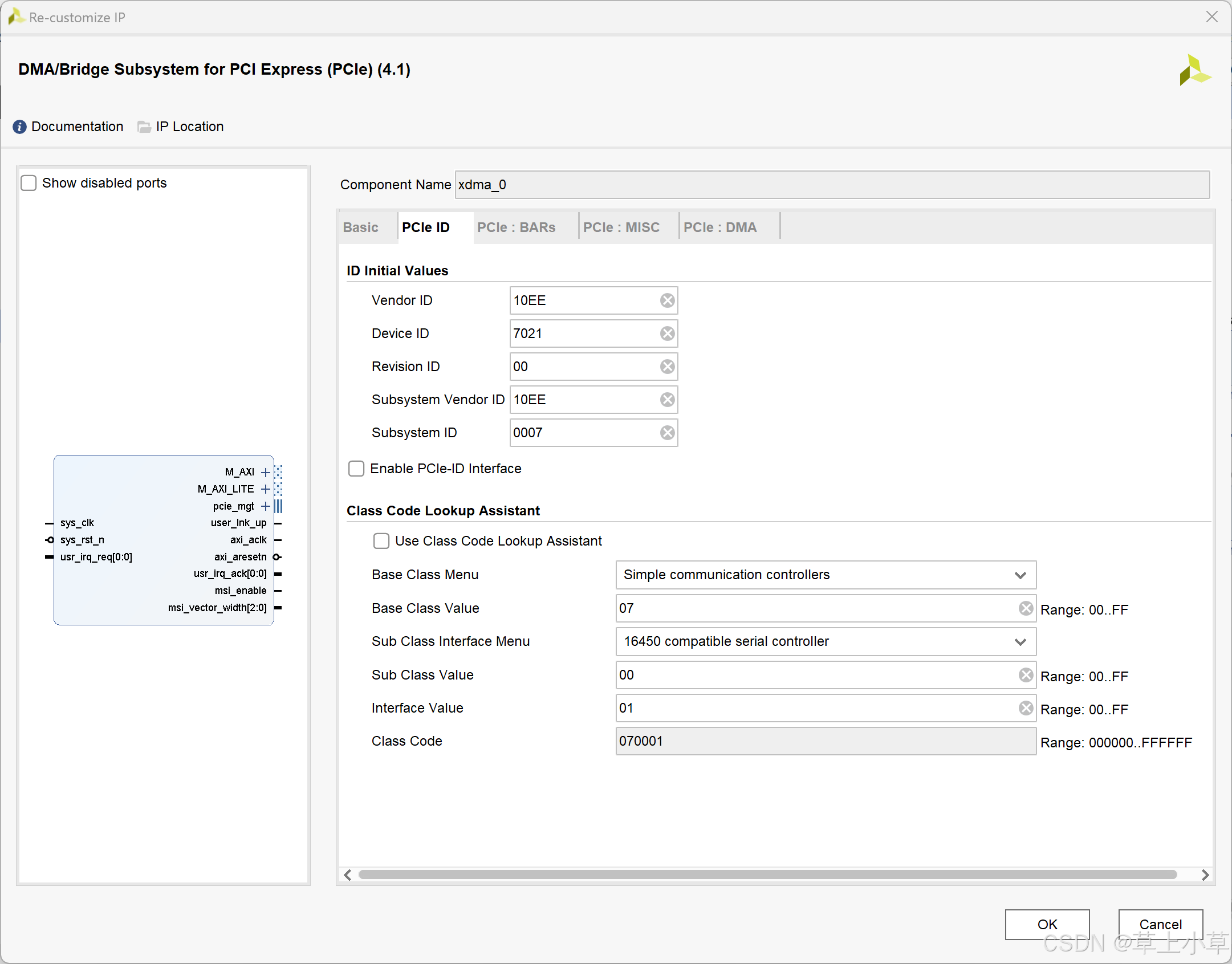

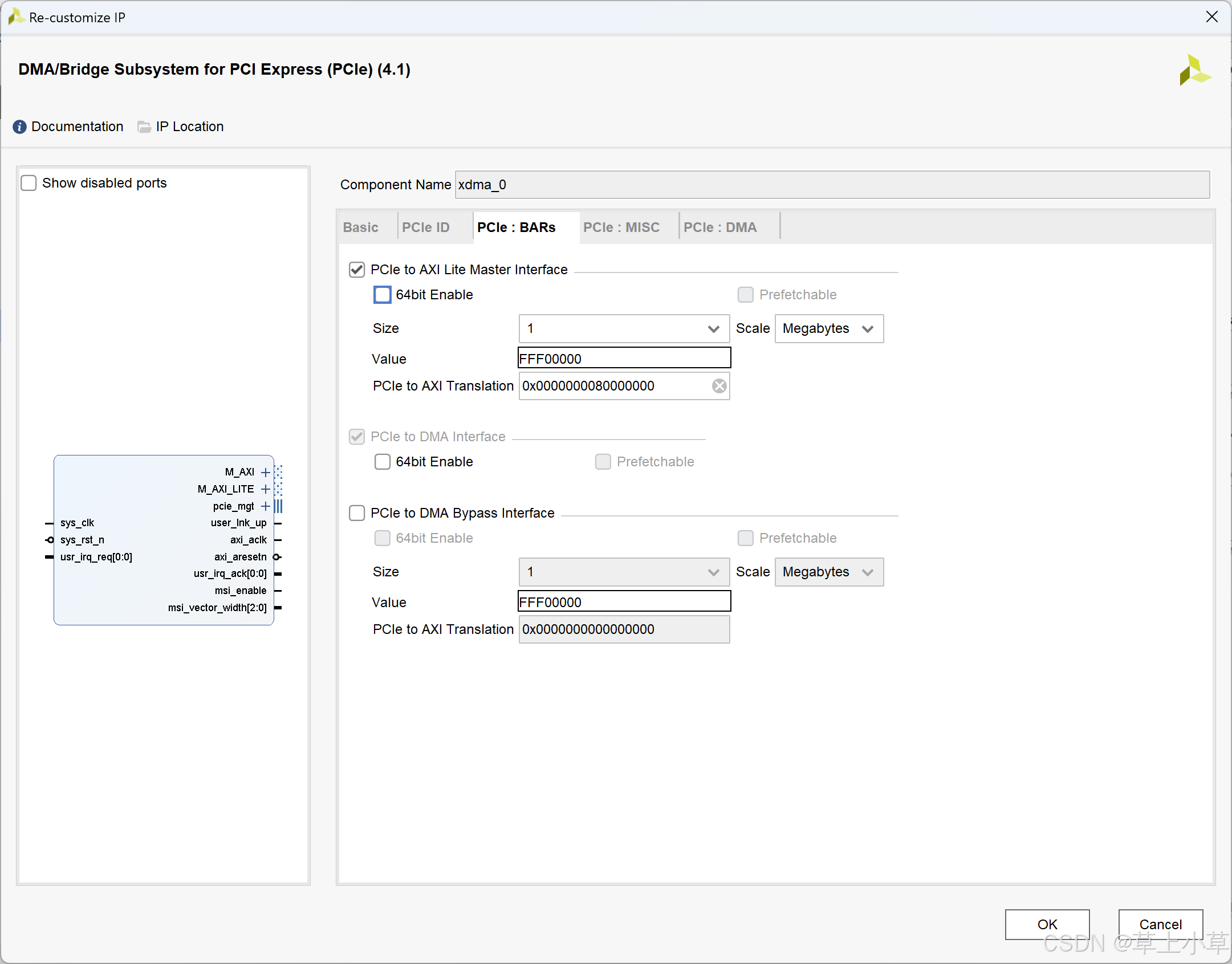

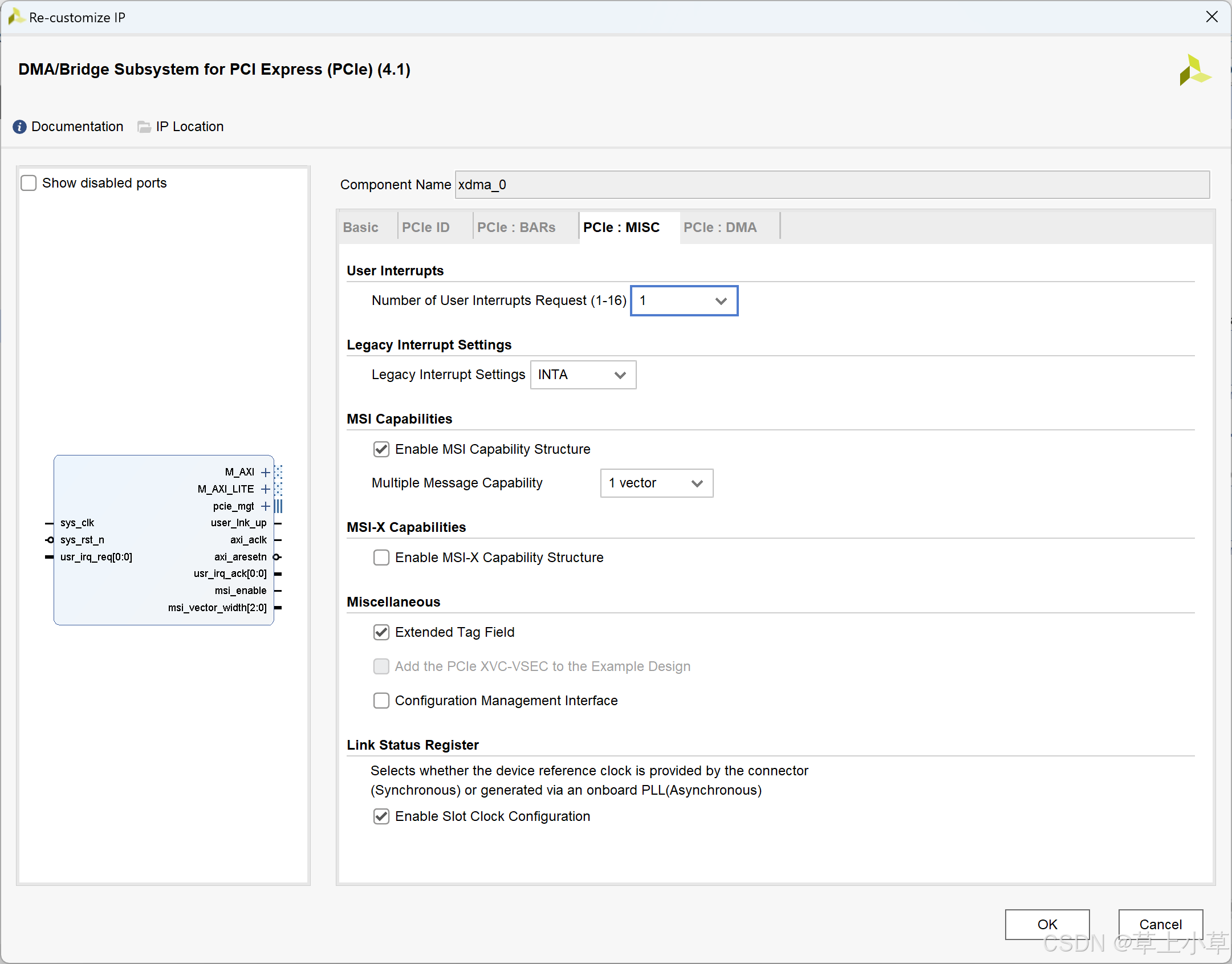

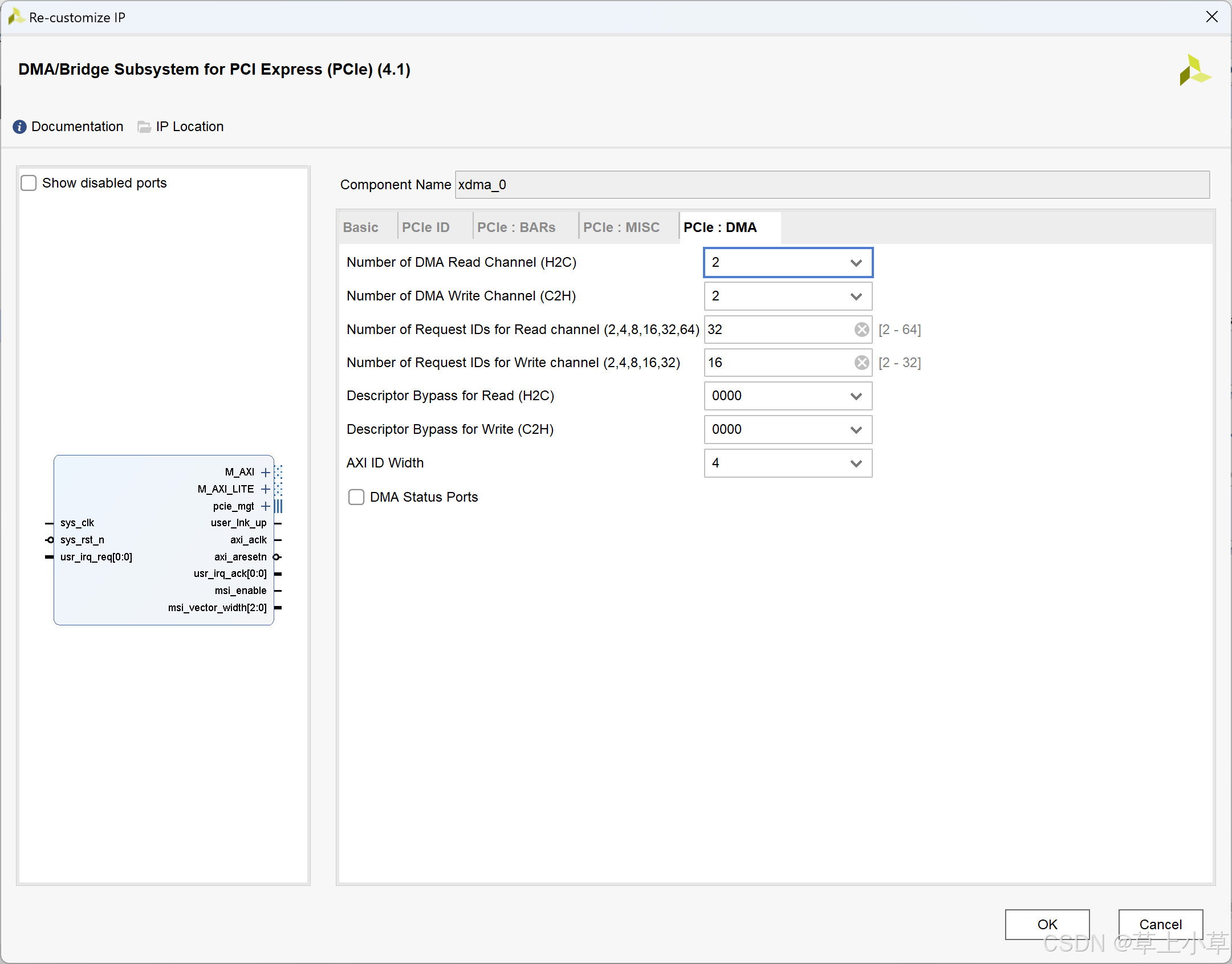

配置结构:

问题描述:

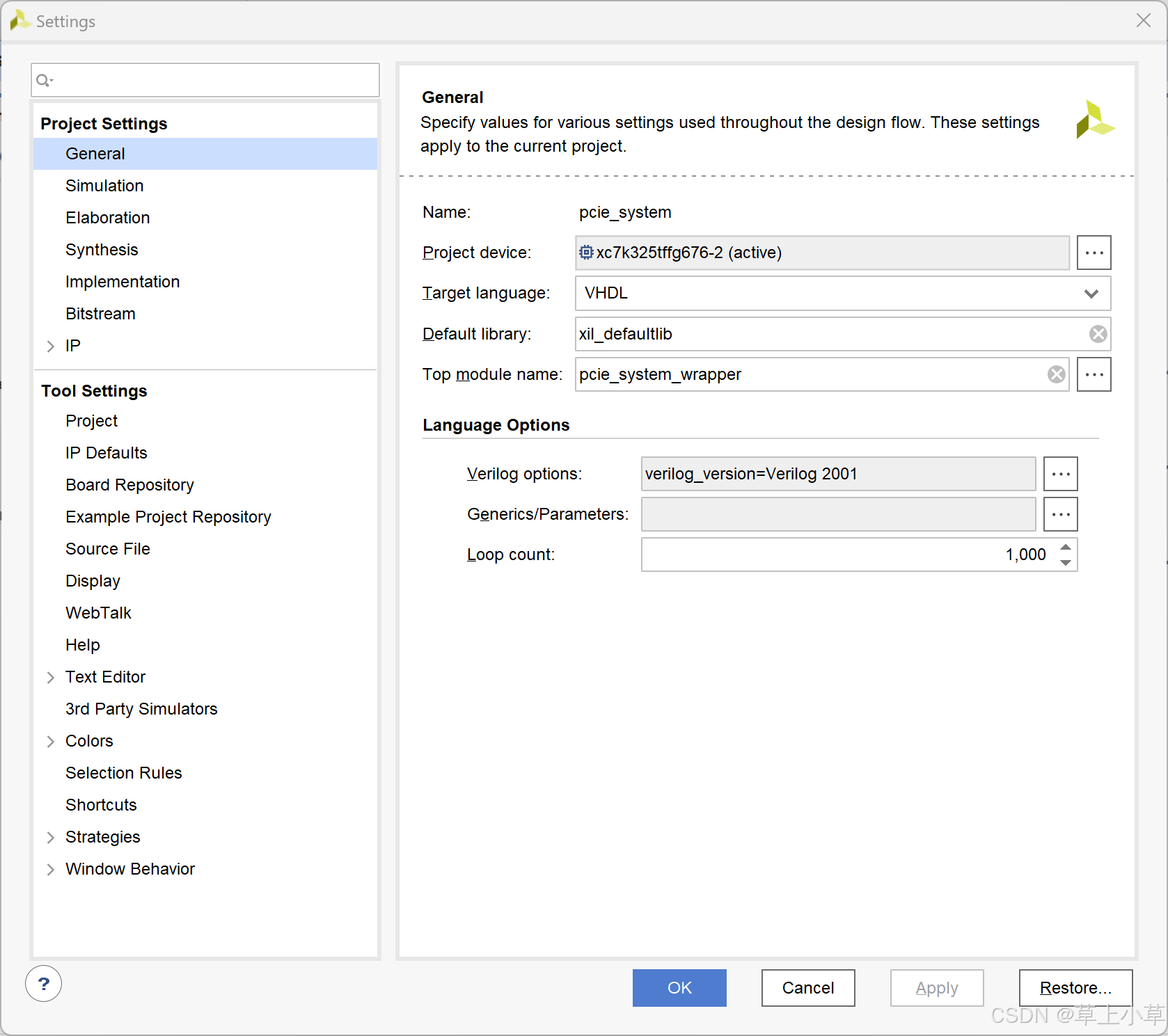

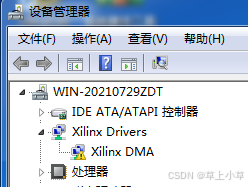

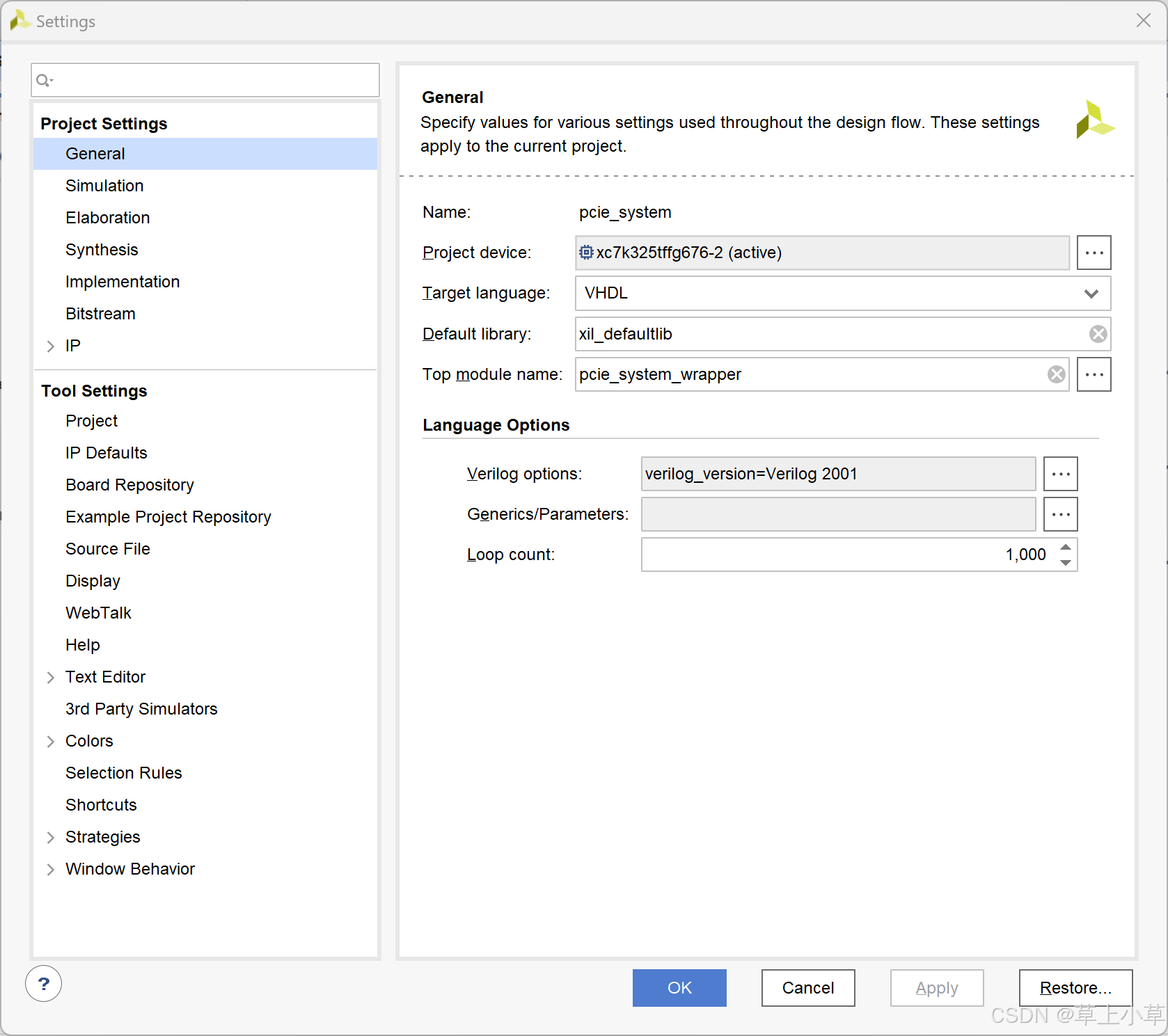

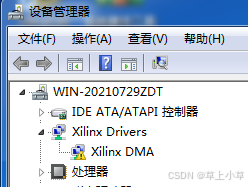

相同的结构和配置,自己做的工程版本烧入板卡后主机识别不到设备,一个前辈留下来的版本就没问题。所有的地方都比对过,唯一有差异的地方是Vivado工程设置里的Target language不一样。

能用的版本使用的是VHDL语言。照着更换语言后板卡识别正常!

该问题貌似跟FPGA型号有关,目前发现就7k325t存在这问题,手上的其他Xilinx芯片板子没出现!!

Vivado版本:2018.3、2019.1、2019.2

FPGA: xc7k325t

配置结构:

问题描述:

相同的结构和配置,自己做的工程版本烧入板卡后主机识别不到设备,一个前辈留下来的版本就没问题。所有的地方都比对过,唯一有差异的地方是Vivado工程设置里的Target language不一样。

能用的版本使用的是VHDL语言。照着更换语言后板卡识别正常!

该问题貌似跟FPGA型号有关,目前发现就7k325t存在这问题,手上的其他Xilinx芯片板子没出现!!

1651

1651

1147

1147

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?