应用场景:

提供给客户的总网表内存在子模块黑盒(例如Xilinx官方的RAM等IP核),自己这边再综合一次完整版的网表非常耗时,只能从现有总网表中提取黑盒模块网表提供给客户进行填充。

1.子模块网表的生成

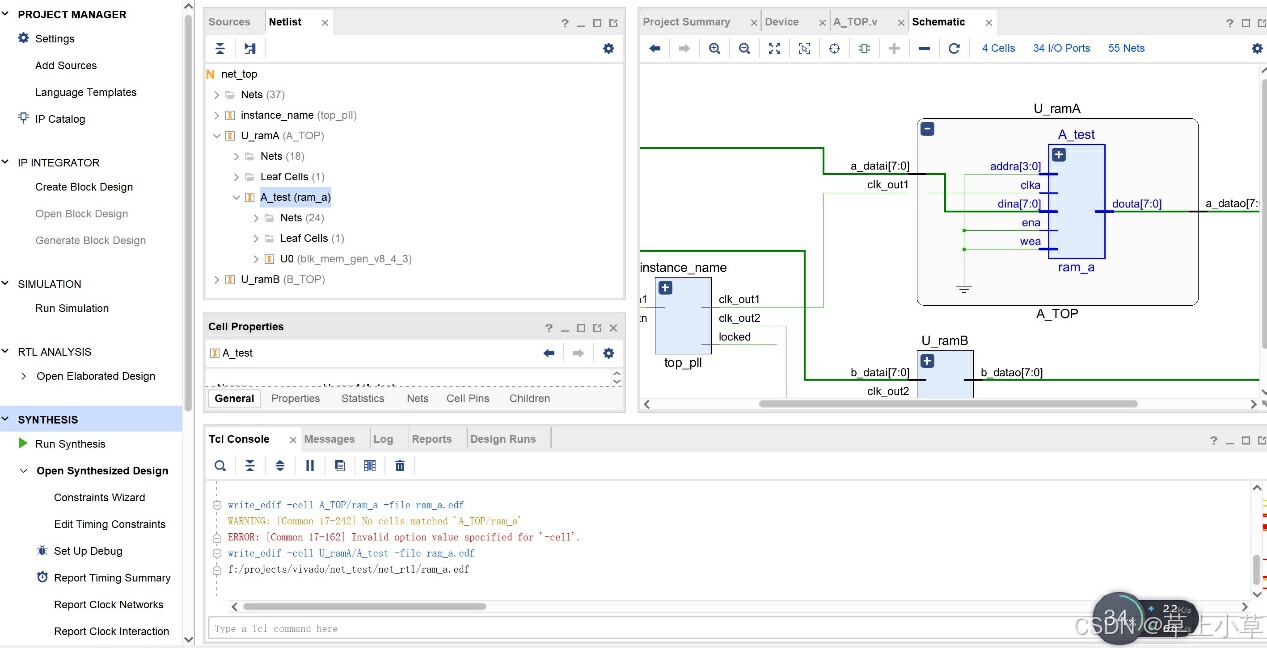

在Vivado中点击左侧栏“Open Synthesized Design”打开总网表,点击“Tcl Console”,在输入栏内使用

write_edif -cell <黑盒模块路径> -file <网表保存位置>

生成子模块网表

注意:子模块路径是例化名路径,而不是模块名路径

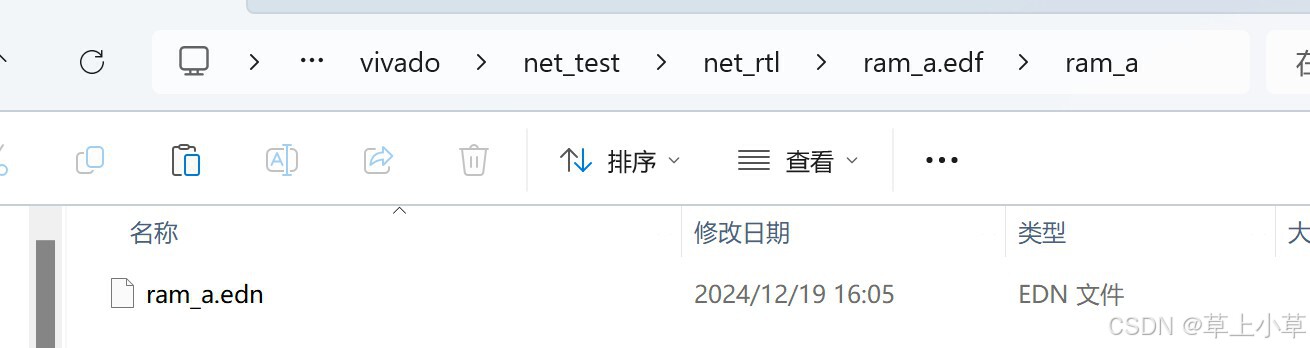

生成好网表后将.edn文件提供给客户

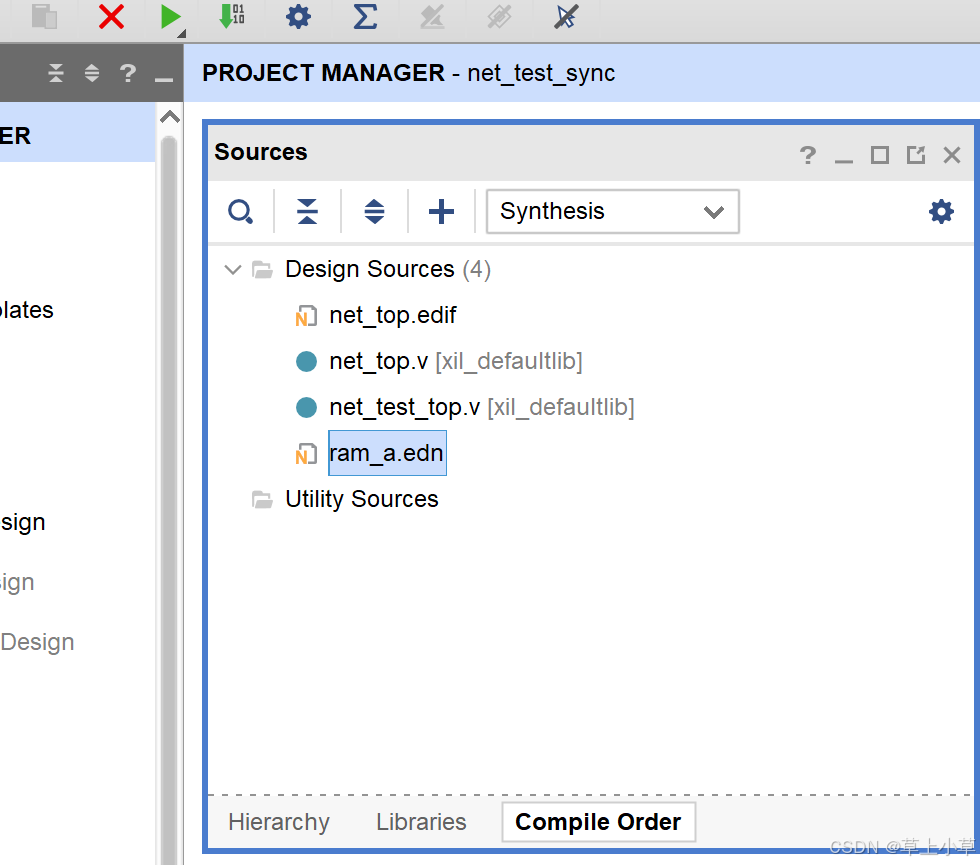

2.网表文件的导入

工程导入.edn网表后,点击切换到“Compile Order”窗口,将对应带.edn网表从“Utility Sources”手动拖进“Design Sources”栏里,否则综合时依旧会识别不到网表。

反向应用场景:

对方提供的网表里,某些Xilinx IP被识别成黑盒,对方没法短时间内提供完整版总网表。只能提供IP的配置信息,就可以先自行生成IP网表进行填充。

- 首先必须确定黑盒是Xilinx的官方IP,并且可由IP Catalog生成的模块。

- 在黑盒模块上包一层,然后通过IP Catalog生成想要的IP。

- 进行综合。

- 用write_edif命令将目标IP网表提取出来。

- 提取的网表导入目标工程中填充黑盒。

注意:如果总网表提供方的vivado版本跟自己的不一样,一些IP的网表文件名可能不一样。例如:

Vivado2023生成的总网表内RAM黑盒模块名称为:

XXXX_blk_mem_gen_v8_4_6

Vivado2019生成网表名为:

XXXX_blk_mem_gen_v8_4_2.edn

要直接将网表名改成与模块同名,Vivado才能识别到。

9654

9654

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?